Memory-based and disk-based algorithms for very high degree permutation groups

- 格式:pdf

- 大小:160.86 KB

- 文档页数:8

The flexibility to solve today’s tough problems...and get ready for tomorrowAgilentESA-E SeriesSpectrum AnalyzersThe Agilent ESA-E seriesFull measurement accuracy after just a five minute warm-up.Built-in tracking generator provides an RF source for scalar network analysis (optional).External mixing extends frequency range to 325 GHz. (optional)Weather resistant front panel allows operation in rain and high humidity.Built-in help function eliminates the need to carry manuals into the field.Zoom windows provides split screen display with both wide and narrow spans.Large high-resolution,high-contrast color display makes viewing multiple traces easy.Rugged case with rubber encased front and rear frames resists transportation stresses.Flexible hardware/software environment allows focused applications like GSM and cdmaOne.Built-in floppy disk drive provides PC compatibility and data archiving.Speed, accuracy, and dynamic range ...with a flexible platform for the future!2Built-in counter precisely identifies signals using the 1 Hz marker-basedcounter.A platformbuilt for speedAgilent uses the latest digital, RF and microwave designs to deliver the performance typically found in more expensive spectrum analyzers. The ESA-E series portable spectrum analyzers have a remarkableone-millisecond RF sweep timeand virtual real-time measurement updates to the display or through GPIB. Along with narrow digital resolution bandwidth filters (10 Hz to 300 Hz), and fast, time-domain sweeps you’ll spend less time testing and have your product to market faster.Specification summary*Designed for performance measurements and...• Fast test times• Superior resolution• Wide dynamic range• Measurement confidence*Includes optional performance, see ESA-E series technical specifications for complete details, literature number 5968-3386E.3 Frequency range summary*Choose the performance you need, when you need itThe Agilent ESA-E’s flexible platform means you can get exactly what you need today while still protecting your investment into the future. The six-slot option card cage lets you choose only the performance you need now (without paying for unneeded capability) and upgrade in the future.This scalable performance in com-bination with Agilent measurement personalities, downloaded into the internal memory, transform the ESA-E analyzer into an application-focused solution built around your unique needs.Built-in card cageprovides the flexibility to add application-specific performance....the flexibility to tailor that performance to your needs...Designed for upgradeabilityAfter the purchase of your analyzer,most optional performance can be installed and calibrated at an Agilent Service Center or in many cases, installed in your facility.Firmware upgrades, including many performance enhancements, are available free by download from the Agilent Web site.Over 35 options tochoose from...and more in the futureIncluding:•Digital resolution bandwidth filters of 10, 30, 100, 200 EMI, and 300 Hz •Time-gated spectrum analysis •FM demodulation/deviationmeasurements plus tune and listen •TV trigger with color picture on screen•1.5/3.0 GHz built-in tracking generator•30 Hz low frequency extension •Fast time-domain sweeps to 25 ns •Additional user memory to 10 MB •External mixing capability to 325 GHz•RF and digital demodulation/communication hardware •75 Ωinput•Snap on battery pack or 12 Vdc operation•Decreased phase noise at wide offsets for greater ACPR dynamic range•Software to perform remote spectrum analyzer control over the internetFor a complete list of options and accessories with ordering andcompatibility information please see the Agilent ESA/EMC Spectrum Analyzer Configuration Guide (literature #5968-3412E).4We’ll build one just for you.5...then add measurement personalities to create application focused solutions.Combine the ESA-E seriesoptional hardware configurations with downloadable measurement personalities to create application specific solutions.Measurement personalitiesFor a growing number of applications Agilent offers unique softwareprograms (provided on 3.5-in. disks)designed specifically for the ESA-E series. Downloaded into analyzer memory, each measurement person-ality provides measurement setups,routines,and results specific to your application, including a user interface with related terminology.Cable fault locationOptions 225 (measurement personali-ty), 1DN (tracking generator)and B7K (measurement kit) combine to identify distance to cable discontinuities for fault location and troubleshooting ofcable installation and maintenance.•Easy to use one-button measurements•Complex algorithms executed with a button press•Improved accuracy and repeatability•Operator independent results •Decreased training time •Improved productivityPhase noiseOption 226 (measurement personality)provides a log plot of phase noise in dBc/Hz versus offset frequency.Cable TV service and installationOption 227 (measurement personality)provides Cable TV operators fast,accurate and rugged spectrumanalysis for field installation, ingress evaluation and troubleshooting.General purpose measurement personalities6cdmaOneOptions BAC (measurement personality) and B74 (RF and digital demodulation hardware) combine to make the cdmaOne standard tests such as ACPR that are required to verify the perform-ance of cdmaOne transmitters.GSM/GPRSOptions BAH (measurement person-ality) and B74 (digital demodulation hardware) combine to provide all the GSM 450/900, DCS1800, PCS1900 tests required to verify the performance of GSM/GPRS mobile and BTS transmitters.Bluetooth ™Option 304 (measurement personality and digital demodulation hardware)provides one-button standard compliant Bluetooth transmitter measurements.Communication focused measurement personalities7Modulation analysisOption 229 (measurement person-ality) and B74 (RF and digitaldemodulation hardware) combine to allow measurements of EVM and related metrics for all major 2G/3G formats. Constellation and eye diagrams are provided to helpverify modulation quality.PerformancePortability8Ease-of-use9Productivity with speed,accuracy and dynamic rangeUp to 220 times faster than analogNow you don’t have to buy a high-priced spectrum analyzer to get advanced technology. The ESA-E series with its optional digital 10 Hz resolution bandwidth gives you sweep times up to 220 times faster than analog!Optional digital narrow resolution bandwidth filters (10 Hz, 30 Hz, 100 Hz,200 Hz and 300 Hz) provide the resolving power to measure closely spaced signals, plus give a narrow shape factor (≤5:1) for superior resolution. The filters deliver a lower noise floor and increased measurement sensitivity for a larger measurement range.Verify your designs with confidenceReduce project time with spectrum-analysis capabilities that optimize your designs. The ESA-E seriesoffers ±1 dB amplitude accuracy, 0.5%span accuracy,±101 Hz frequency accuracy,and a continuously phase-locked synthesizer for stability and repeatability. Calibrate out the frequency-related amplitude effects with built-in amplitude correction.The automatic background alignment offers continuous calibration toassure measurement confidence.Fewer measurement constraintsWhen a passband contains two or more signals such as CDMA or TDMA modulation, you don’t want dynamic range to limit your measurements.The ESA-E series has sensitivity down to –153 dBm, plus a third-order intercept point of +12.5 dBm (typically +16 dBm) and a second harmonic intercept point of+45 dBm to give you wide distortion free measurement range.Research and development10MeasureOne-button results with measurement personalitiesMeasure your designs easier with Agilent modulation analysis,Bluetooth ™, GSM/GPRS, cdmaOne,and phase noise measurement personalities. Execute complex algorithms with the press of a button by utilizing downloaded measurement personalities incombination with optional hardware.Expert yet easy EMI measurementsThe Agilent E7400A series of EMC analyzers takes advantage of the ESA-E series platform to provide precompliance measurements fordesign analysis.For more information see the Agilent EMC Analyzers and EMI Software brochure , literature number 5968-2516.View only the signals ofinterest with segmented sweep - paste together up to 32 discontinuous spans in to one sweep.CaptureCapture measurement results easily and quickly with IntuiLinkIntuiLink PC software provides easy transfer of ESA measurement trace data and images directly into MS Excel and Word documents for analysis, archiving, presentations, or printing. Transfer data and images over GPIB, RS232, or LAN.Save and restore analyzer states.Utilize automatic measurementtransfers by date and time. IntuiLink is included standard with GPIB and RS232 options.AnalyzeAnalyze measurement resultsAnalyze breadboard results easier with ESA instrument links supported by the Agilent EEsof Advanced Design System.Research and development11Characterize power statistics of nextgeneration digitally-modulated signals with leading test methods. Power Complementary Cumulative Distribution Function (CCDF)curves provide the peak to average data needed by 3G component designers.Six-offsets in ACPR allow convenient measurements on components subject to multi-carrier signals, (e.g. MCPAs).Every millisecond countsReal-time responseWhether you are tuning oscillators manually or performing high-volume, automatic tests on wireless products, the ESA-E series of spectrum analyzers gives a real-time response with up to 45 measurements per second. Eliminate your measurement-speed bottlenecks to help meet your production goals.This family of spectrum analyzers offers improved productivity, witha one-millisecond sweep time andas low as 25 ns in zero span.Use variable sweep points to optimize speed versus frequency resolution. Maximize speed by measuring only the frequencies of interest with segmented sweep.Unparalleled speed for manual or remote operationThe ESA-E series spectrum analyzers offer the following features to help you quickly build and test your products:•One-millisecond RF sweep time •25 ns zero span sweep time (optional)•Up to 45 measurements per second update to the display•Large 13.8-cm color VGA TFT active matrix display with wide viewing angle•Color VGA display output connector•Enhanced circuit tuning with continuous peak search•Instant printing (PCL5 printers)•Limit lines with large, colorfulpass/fail messagesMeasurements per secondESA-E series45 updates/sec. display45 updates/sec. GPIB8566B Turbo24 updates/sec. display 15 updates/sec. GPIB Swept-tuned spectrum analysis speedSetting a new standard for speed!Surpassing the GPIB speed record The ESA-E series surpasses the speed of the record-holding Agilent 8566B high-performance spectrum analyzer for moving data from the analyzerto a computer. Vastly improved sweep time and measurement update rate eliminate the GPIB data-rate bottleneck to help you more easily meet your productivity goals.• 45 measurements per second transferred to a computer•75 ms RF center frequencytuning time• Standard Commands for Programmable Instruments (SCPI) compliant• The Agilent 8590-series/ESA programming conversion guide • VXI plug&play drivers for ease of program development12Reduce test marginsThe excellent measurement accuracy reduces measurement uncertainty to allow for narrower test margins and improved yields. With an overall amplitude accuracy of ±1 dB,and a frequency accuracy of ±101 Hz plus the continuously phase-locked synthesizer, you get the performance you need to have confidence in your tests.Individual calibration certificate included standard with every analyzer.Built-in preamplifier maximizes sensitivityWhen your application calls for measurements of very low-level signals, the optional built-in preamplifier (to 3 GHz)in theESA-E series increases sensitivity.This high-gain, low-noise preamplifier lets you use wider bandwidths for even faster sweep times when searching for low-level signals.For circuit adjustments withreal-time results, the ESA-E series spectrum analyzers offers a one-millisecond sweep time and up to 45 measurement updates per second.13The ESA-E series hasdigital narrow resolution bandwidth filters and internal preamplifiers so you can identify low-level spurs.Leverage your software investmentIn the past decade, many manufactur-ers have installed Agilent 8590-series spectrum analyzers in automated production lines. If you are considering upgrading your automated stations to take advantage of the ESA-E series capabilities, Agilent can help preserve your software investment and minimize your change-over costs. An optional 8590-series programming code compatibility mode is available,which enables ESA-E series analyzers to work with more than 120 commonly used 8590-series programming commands.Calibrated field measurements in just FIVE minutes!The ESA-E series takes only 5 minutes to warm-up so technicians spend little time waiting for instrument stabilization. The automatic, internal background alignment feature gives consistently accurate results over varying temperatures. Measurement results are easily saved, printed or integrated into external tools for analysis and documentation using the standard 3.5 in floppy disk drive. The easy-to-use file manager with a time and date stamp helps to organize storage of measurement data. And, the optional rechargeable battery provides up to 1.9 hours of cordless operation.The tough ESA-E is field-rugged, yet offers uncompromising performance Snap-on battery provides freedomfrom AC power mains 14Easy,worry-free measurementsThe ESA-E series offers outstanding lab-grade performance, and protec-tion from the elements along with convenience and ease-of-use features tailored to field service.•Rubber-encased frames and the lack of vibration-prone internal adjustments improve reliability during transportation.•Snap-on rechargeable battery provides up to 1.9 hours of cordless operation (optional).•12 Vdc operation from automotive electrical systems•Rain-resistant front panel, shielded vents, and side-mounted fanprotect the instrument in adverse environments.•Vibration and shock resistance with solid state internal memory.Get accurate measurementsin every kind of field condition• Continuous automatic background alignment provides accuracy over varying temperature conditions.• Hard transit case, soft operating/carrying case or backpack provides choice of convenient transportation aids.•Flexible tilt handle optimizes line of sight whether the analyzer is viewed from the bench or ground.•Color display provides optimum readability regardless of lighting and viewing angle.•Find cable problems with the fault location measurement personality.•Troubleshoot cellular base stations with GSM and cdmaOne measurement personalities.•Make one-button RF power measurements for all the major2G/3G formats.Backpack with ESA to remote locations15Agilent ESA-E series – a whole product solution The performance of the ESA-E series spectrum analyzer isonly a small part of what you get from Agilent Technologies.Agilent strives to provide complete solutions that gobeyond our customers’ expectations. Only Agilent offersthe depth and breadth of enhancements, software,services, connectivity,accessibility and support to helpour customers reach their measurements objectives.Please contact Agilent for more information.Post-sales support• Standard three-year globalwarranty• Worldwide call center and calibrationservice center support network• One-year calibration intervals• FREE Firmware upgrades and servicenotes available from Agilent’s Web site• PC-based calibration software•Computer-based service training onCD-ROM•Flexible support options to meetyour needsThe Agilent ESA-E series ismanufactured in an ISO 9001registered facility to Agilent’sexacting standards.Training and access toinformation• Printer support matrix onAgilent’s Web site• Factory service training• Web-based support of frequentlyasked questions• Operation , programming andcalibration manuals on CD-ROM andon Agilent’s Web site• User and applications training•T echnical seminars•Cellular/PCS base stationtroubleshooting course•Calibration certificate standard•Localized operation manualsPC connectivity & software• Floppy disk drive• GPIB or RS232 interfaces• VXI plug&play drivers• IntuiLink spectrum analyzer software• EEsof Advanced Design Systemdriver (instrument link)•Programming examples on CD-ROM• SCPI (Standard Commands forProgrammable Instruments)• Custom software service• BenchLink web remote control software• 8590-series programming codecompatibility• 8590-series/ESA programmingconversion guideProduct peripherals andaccessories• Battery packs and 12 Vdc cables•Rack mounts•Operating/carrying, backpack andtransit cases•External mixers to 110 GHz•Preamplifiers to 26.5 GHz•High-impedance active probes•RF/MW limiters, adapters & cablesPre-sales services•Rentals, leasing, and financing• Application engineering andconsulting services• Application notes• Custom product modifications• Custom downloadable programs• Product literature available fromAgilent’s Web site• Demonstration units availablefor evaluation• Trade-up programs• Support at least 5 years beyondproduction life of product16Add an external VGA color monitor.12 Vdc operation from automotive batteries.Parallel port supports most HP printers (optional).Supports Agilent preselected external mixers (optional).Digital demodulation hardware for current and future communications systems (optional).Snap-on battery pack for portability (optional).Use an external frequency reference for even more accuracy.Input signal down converted to 21.4 MHz (optional).High speed GPIB interface(optional).17Ordering information ESA-E seriesAgilent E4401B Spectrum Analyzer 9 kHz to 1.5 GHz Agilent E4402B Spectrum Analyzer 9 kHz to 3.0 GHz Agilent E4404B Spectrum Analyzer 9 kHz to 6.7 GHz Agilent E4405B Spectrum Analyzer 9 kHz to 13.2 GHz Agilent E4407B Spectrum Analyzer 9 kHz to 26.5 GHzAdditional informationAgilent literatureNumber ESA-E Series Technical Specifications 5968-3386E ESA-E Series Configuration Guide 5968-3412E Spectrum Analyzer Selection Guide 5968-3413E ESA-E Series Self-Guided Demo 5968-3658E ESA Battery Pack Product Overview 5966-1851E EMI Pre-compliance Brochure5968-2516E N2717A Calibration Software Product Overview 5968-5478E GSM/GPRS Measurements Product Overview 5968-6871E cdmaOne Measurements Product Overview 5968-6869E TV Transmission Quality Measurements Flyer 5968-6874E Measuring Signals Above 26.5 GHz Flyer 5968-6873E Cable Fault Location Product Overview 5980-1915E Phase Noise Product Overview 5980-1191E Cable TV Product Overview5980-2297E Bluetooth™ Measurement Solutions Product Overview5980-2786EN Modulation Analysis Measurements Product Overview5988-2116EN IntuiLink Software Data Sheet 15980-3115EN BenchLink Web Remote Control Software Product Overview5988-2610ENFor the latest information on the Agilent ESA-E series see our Web page at: 1. For more information about IntuiLink software visit our Web site at: /find/IntuiLink1819Agilent Technologies’ Test and Measurement Support, Services, and AssistanceAgilent Technologies aims to maximize the value you receive, while minimizing your risk and problems. We strive to ensure that you get the test and measurement capabilities you paid for and obtain the support you need. Our extensive support resources and services can help you choose the right Agilent products for your applications and apply them successfully. Every instrument and system we sell has a global warranty. Support is available for at least five years beyond the production life of the product. Two concepts underlie Agilent’s overall support policy: “Our Promise” and “Your Advantage.”Our PromiseOur Promise means your Agilent test and measurement equipment will meet its advertised performance and functionality. When you are choosing new equipment, wewill help you with product information, including realistic performance specifications and practical recommendations from experienced test engineers. When you use Agilent equipment, we can verify that it works properly, help with product operation, and provide basic measurement assistance for the use of specified capabilities, at no extra cost upon request. Many self-help tools are available. Your AdvantageYour Advantage means that Agilent offersa wide range of additional expert test and measurement services, which you can purchase according to your unique technical and business needs. Solve problems efficiently and gain a competitive edge by contracting with us for calibration, extra-cost upgrades, out-of-warranty repairs, and on-site education and training,as well as design, system integration, project management, and other professional engineering services. Experienced Agilent engineers and technicians worldwide canhelp you maximize your productivity, optimize the return on investment of your Agilent instruments and systems, and obtain dependable measurement accuracy for thelife of those products.By internet, phone, or fax, get assistance with all your test and measurement needs.Online assistance:/find/assist Phone or Fax:United States:(tel)180****4844Canada:(tel)187****4414(fax) (905) 282-6495Europe:(tel) (31 20) 547 2323(fax) (31 20) 547 2390Japan:(tel) (81) 426 56 7832(fax) (81) 426 56 7840Latin America:(tel) (305) 269 7500(fax) (305) 269 7599Australia:(tel) 1 800 629 485(fax) (61 3) 9210 5947New Zealand:(tel) 0 800 738 378(fax) 64 4 495 8950Asia Pacific:(tel) (852) 3197 7777(fax) (852) 2506 9284Product specifications and descriptions in this document subject to change without notice. Copyright © 2000, 2001 Agilent Technologies Printed in USA, March 27, 20015968-3278EMicrosoft Excel® and Microsoft Word® are U.S. registered trademarks of Microsoft Corp. Bluetooth™ is a trademark owned by Telefonaktiebolaget LM Ericsson, Sweden and licensed to Agilent Technologies.。

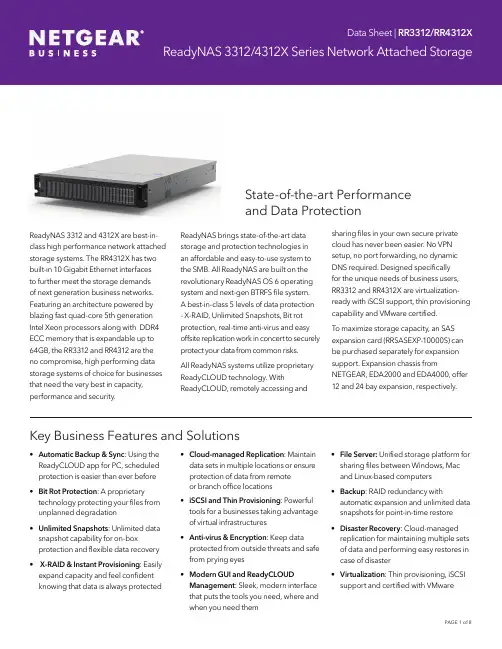

State-of-the-art Performance and Data ProtectionReadyNAS 3312 and 4312X are best-in-class high performance network attached storage systems. The RR4312X has two built-in 10 Gigabit Ethernet interfacesto further meet the storage demandsof next generation business networks. Featuring an architecture powered by blazing fast quad-core 5th generation Intel Xeon processors along with DDR4 ECC memory that is expandable up to 64GB, the RR3312 and RR4312 are the no compromise, high performing data storage systems of choice for businesses that need the very best in capacity, performance and security.ReadyNAS brings state-of-the-art datastorage and protection technologies inan affordable and easy-to-use system tothe SMB. All ReadyNAS are built on therevolutionary ReadyNAS OS 6 operatingsystem and next-gen BTRFS file system.A best-in-class 5 levels of data protection- X-RAID, Unlimited Snapshots, Bit rotprotection, real-time anti-virus and easyoffsite replication work in concert to securelyprotect your data from common risks.All ReadyNAS systems utilize proprietaryReadyCLOUD technology. WithReadyCLOUD, remotely accessing andsharing files in your own secure privatecloud has never been easier. No VPNsetup, no port forwarding, no dynamicDNS required. Designed specificallyfor the unique needs of business users,RR3312 and RR4312X are virtualization-ready with iSCSI support, thin provisioningcapability and VMware certified.To maximize storage capacity, an SASexpansion card (RRSASEXP-10000S) canbe purchased separately for expansionsupport. Expansion chassis fromNETGEAR, EDA2000 and EDA4000, offer12 and 24 bay expansion, respectively.Key Business Features and Solutions• Automatic Backup & Sync: Using the ReadyCLOUD app for PC, scheduled protection is easier than ever before• Bit Rot Protection: A proprietary technology protecting your files from unplanned degradation• Unlimited Snapshots: Unlimited data snapshot capability for on-box protection and flexible data recovery • X-RAID & Instant Provisioning: Easily expand capacity and feel confident knowing that data is always protected • Cloud-managed Replication: Maintaindata sets in multiple locations or ensureprotection of data from remoteor branch office locations• iSCSI and Thin Provisioning: Powerfultools for a businesses taking advantageof virtual infrastructures• Anti-virus & Encryption: Keep dataprotected from outside threats and safefrom prying eyes• Modern GUI and ReadyCLOUDManagement: Sleek, modern interfacethat puts the tools you need, where andwhen you need them• File Server: Unified storage platform forsharing files between Windows, Macand Linux-based computers• Backup: RAID redundancy withautomatic expansion and unlimited datasnapshots for point-in-time restore• Disaster Recovery: Cloud-managedreplication for maintaining multiple setsof data and performing easy restores incase of disaster• Virtualization: Thin provisioning, iSCSIsupport and certified with VMwareHardware ReadyNAS 3312ReadyNAS 4312S ReadyNAS 4312XCPU-10000S Intel Xeon E3-1225v63.3GHzQuad Core Processor,Max Turbo Speed3.7GHzIntel® Xeon E3-1245v6 3.5GHzQuad Core, HyperThreaded Processor,Max Turbo Speed3.9GHzIntel® Xeon E3-1245v6 3.5GHzQuad Core, HyperThreaded Processor,Max Turbo Speed3.9GHzCPU-20000S Intel Xeon E3-1225v63.3GHz, Max TurboSpeed 3.7GHzIntel Xeon E3-1245v63.5GHz, Max TurboSpeed 3.9GHzIntel Xeon E3-1245v63.5GHz, Max TurboSpeed 3.9GHzMemory8GB DDR4 ECC16GB DDR4 ECC16GB DDR4 ECC Memory Expansion64GB DDR464GB DDR464GB DDR4 Drive Bays121212Drive T ypes Supported SATA/SSD 2.5” or 3.5”SATA/SSD 2.5” or 3.5”SATA/SSD 2.5” or 3.5”Hot Swappable Drives Yes Yes Yes eSATA Ports222SAS Ports for Expansion Chassis (sold separately)222 Gigabit LAN Ports44410Gbps LAN Optical SFP+02010Gbps LAN Copper 10GBase-T002USB Ports2x USB3.02x USB3.02x USB3.0Power SupplyDual RedundantInternal 550 W; input100-240V AC,50-60HzDual RedundantInternal 550 W; input100-240V AC,50-60HzDual RedundantInternal 550 W; input100-240V AC,50-60HzChassis Warranty5 years including5 years NextBusiness Day hard-ware replacement5 years including5 years NextBusiness Day hard-ware replacement5 years including5 years NextBusiness Day hard-ware replacementFan (mm) 3 x 80 3 x 80 3 x 80 Dimensions DxWxH (mm)707 x 445 x 88 707 x 445 x 88 707 x 445 x 88 Weight (diskless) (kg)11.96 11.96 11.96 Software and Functionality ReadyNAS 3312ReadyNAS 4312S ReadyNAS 4312XCertification and Compatibility VMware vSphereESXi 6.0 VMware vSphereESXi 6.0VMware vSphereESXi 6.0Cloud-discovery, Setup and Management Yes Yes Yes Data Protection with Unlimited Snapshots Yes Yes Yes Web-managed Replication for Disaster Recovery Yes Yes Yes Real-time Antivirus Yes Yes Yes iSCSI and Thin Provisioning Yes Yes Yes ReadyNAS Rackmount ComparisonTechnical SpecificationsData Protection (Backup & Replication)• Unlimited block-based snapshots for continuous data protection• Restore Snapshots to any point in time• Restore Snapshot data from local admin GUI, ReadyCLOUD, or native Windows File Explorer• Scheduled and manual snapshots• File Synchronization (rsync)• Encrypted Remote Replication• Data compression• Cloud managed Remote Replication (ReadyNAS to ReadyNAS). No licenses required for ReadyNAS OS 6 devices.• AES 256-bit volume based encryption• X-RAID (automatic single volume online expansion)• Single Disk, JBOD• RAID Levels: 0, 1, 5, 6, 10, 50, 60• RAID Global Hot Spare• Backup to external storage (USB/eSATA)• Apple Time Machine support• Amazon Cloud Drive synchronization (requires Amazon account)• ReadyNAS Vault™ Cloud backup (optional service)• Dropbox™ file synchronization (requires Dropbox account)• Real-time Anti-Virus scanning using signature and heuristic algorithms. (No end-user licenses required)Protection for viruses, malware, worms, and Trojans.• Bitrot automatic detection & correction for degraded mediaStorage Area Networks (SAN), Virtualization• Unlimited iSCSI LUN Snapshot• Thin or thick provision LUNs• Multi-LUN per target• LUN mapping and masking• SPC-3 Persistent Reservation (iSCSI)• MPIO and MC/S (iSCSI)• Max # iSCSI Target: 256• Max # iSCSI LUN: 256• VMware vSphere 6• Citrix XenServer 6• Windows Server 2008 Hyper-V• Windows Server 2008 Failover Clustering• Windows Server 2012 R2ReadyCLOUD (cloud access to ReadyNAS• ReadyCLOUD portal based data access and management• Upgrade firmware remotely• VPN quality remote data transfer and management• Share data with friends & co-workers directly from portal• Share file via email linkReadyCLOUD Client Applications• ReadyCLOUD client applications for Apple OS X, Microsoft Windows, Android, and Apple iOS• VPN quality remote data transfer and management• Simple remote access through ReadyCLOUD client (no firewall or router configuration needed)• Sync files/folders between PC (Mac/Windows) & ReadyNAS• Sync files/folders between multiple PCs and ReadyNAS• Sync files/folders between multiple users and ReadyNAS• Backup files/folders from PC to ReadyNASFile System & Transfer Protocols• ReadyNAS OS 6.5 or later• Linux 4.x• Internal File System: BTRFS• External File System: EXT3, EXT4, NTFS, FAT32, HFS+• Copy-on-write file system• Microsoft Network (CIFS/SMB 3)• Apple OS X (AFP 3.3)• Linux/Unix (NFS v4)• Internet (HTTP)• Secure Internet (HTTPS)• File Transfer Protocol (FTP)• FTP over SSL / TLS (explicit)• FTP Passive mode with port range setup• FTP Bandwidth control• FTP Anonymous• FTP Transfer Log• Secure Shell (SSH)• Web Authoring (WebDAV)• Storage Array Network (iSCSI)• File Synchronization (rsync)• Local web file managerUsers/Groups• Max # Users: 8192• Max # User Groups: 8192• Max # Share Folder: 1024• Max # Concurrent Connections: 1024• Share Folder Level ACL Support• Advanced Folder Permissions with Subfolder ACL support for CIFS/SMB, AFP, FTP• Microsoft Active Directory (AD) Domain Controller Authentication• Local access list• ReadyCLOUD based ACL• Domain user login via CIFS/SMB, AFP, FTPManagement• ReadyCLOUD cloud based discovery and management• RAIDar local discovery agent (Windows/Mac)• Save and restore system configuration (clone devices)• Local event log• Local Graphical User Interface (GUI) Languages: English, German, French, Japanese, Chinese (Traditional &Simplified), Russian, Swedish, Portuguese, Italian, Spanish, Polish, Czech, Dutch, Korean• Unicode support• Volume Management• Thin provision Shares and LUNs• Instant Provisioning/Expansion with data protection• Restore to factory default• Operating Systems supported: Microsoft Windows 7, 8/8.1, 10, Microsoft Windows Server 2008 R2/2012, AppleOS X, Linux/Unix, Solaris, Apple iOS, Google Android• Supported Web Browsers (Microsoft Internet Explorer 9+, Microsoft Edge, Mozilla Firefox 14+, Google Chrome50+, Apple Safari 5+)System Monitoring• Device capacity, performance, resource and health monitoring• Bad block scan• Hard Drive S.M.A.R.T.• File System Check• Disk Scrubbing• Disk Defragment• Volume balance• Alerts (SMTP email, SNMP, local log)• Auto-shutdown (hard drive, fan, UPS)• Auto-restart on power recoveryNetworking Protocols• TCP/IP• IPv4• IPv6• Static IP Address• Dynamic IP Address• Multiple IP Settings• DHCP Client• UPnP Discovery• Bonjour Discovery• Link Aggregation IEEE 802.3ad• Port Trunking (balanced round robin, active backup, balance xor, broadcast, 802.3ad link aggregation LACP,transmit load balancing, adaptive load balancing)• Hash Types IEEE 802.3ad LACP or XOR (Layer 2, Layer3, Layer 4)• Jumbo Frames• Static routes• Secure Shell (SSH)• Simple Network Management Protocol v2, v3• Network Time Protocol (NTPMedia• ReadyDLNA (UPnP DLNA Media Server)• ReadyDLNA streams to any compliant device including Playstation and Xbox• ReadyDLNA mobile clients for remote media streaming (iOS, Android)• ReadyDLNA supported music formats (wav, wma, pcm, ogg, mp3, m4a, flac, aac)• ReadyDLNA supported photo formats (jpg, jpeg)• ReadyDLNA supported video formats (3gp, mp4, wmv, xvid, vob, ts, tivo, mts, mpeg, mpg, mp4, mov, mkv, m4v,m4p, m2t, m2ts, flv, flc, fla, divx, avi, asf)• ReadyDLNA supported playlist formats (pls, m3u)• ReadyNAS Surveillance (free trial, license required) supports over 70 brands and 1600 models of IP cameras• iTunes Server• iTunes supported audio formats (mp3, m4a, m4p, wav, aif)• iTunes supported video formats (m4v, mov, mp4)• iTunes supported playlist formats (m3u, wpl)• TiVo Archiving• Plex Media Server streams to DLNA and Plex clients (mobile, desktop, Android TV, Roku, Samsung & LG TVs)HardwareCPU• ReadyNAS 3312: Intel® Xeon E3-1225v5 3.3GHz Quad Core Processor, Max Turbo Speed 3.7GHz• ReadyNAS 4312S: Intel® Xeon E3-1245v5 3.5GHz Quad Core, Hyper Threaded Processor, Max Turbo Speed 3.9GHz• ReadyNAS 4312X: Intel® Xeon E3-1245v5 3.5GHz Quad Core, Hyper Threaded Processor, Max Turbo Speed 3.9GHzMemory• ReadyNAS 3312: 8GB DDR4 ECC• ReadyNAS 4312S:16GB DDR4 ECC• ReadyNAS 4312X:16GB DDR4 ECC• Memory Expansion: 64GB DDR4• Flash: 256MB for OS• 12 Hot Swappable Drive Bays• Drive Types Supported: SATA/SSD 2.5” or 3.5”• Two eSATA ports• Two USB3.0 ports• Total solution capacity: 120TB w/o expansion 600TB w/ 2 x EDA4000• RR4312X: dual 10GbE copper ports• RR4312S: dual 10GbE SFP+ ports• Quad Gigabit Ethernet ports with link aggregation and failover• LEDs: Power, System, 4 x LAN• Three 80mm fans• Dimensions (DxWxH):707mm x 445mm x 88mm• Weight (diskless): 11.96 kg• Dual 550 watt redundant power supplies• Power cord localized to country of sale• Rackmount sliding rail includedCompliance• ENGR 10049 EST Environmental Stress Test Guideline• ENGR 10045 EVT Engineering Validation Test Guideline• ENGR 10048 CVT Compliance Validation Test Guideline• ENGR 10046 System Validation Test Guideline• ENGR 10023 HALT Accelerated Life Test Guideline• ENGR 10036 CDG Component Derating GuidelineEnvironment• Noise levels: <49dBA @ 25C• Operating Temperature: 0-45C• Operating Humidity: 20-80% relative humidity, non-condensing• Smart Fan• Scheduled Power on/off• UPS Support• Network UPS with SNMP Management• Wake on LANEnvironment• Hard drive disk spin down• Auto-power on (after shutdown)• AC Input Power Voltage 100V to 240V• Power Frequency: 50Hz to 60Hz, Single Phase• Power Consumption (Max/Wake on LAN) RR3312: 210/9.2 watts• Power Consumption (Max/Wake on LAN) RR4312S: 210/9.2 watts• Power Consumption (Max/Wake on LAN) RR4312X: 210/9.2 watts• Certification: FCC Class A, CE Class A, RoHS, VCCI Class A• MTBF: 70,723 hoursAccessories• RTRAY04-10000S: Replacement/additional 3.5” or 2.5” hard drive tray• RFAN04-10000S: Replacement 80mm fan• RRAIL03-10000S: Replacement/additional sliding rack mount rail• RPSU03-10000S: Replacement/additional 550W power supply unit• RMEM04-10000S: Replacement 8GB memory module for RR3312 and RR4312X• RMEM05-10000S:16GByte DDR4 ECC U-DIMM 2Rx8 Memory Expansion, applicable to RR3312, RR4312X andRR4312S• RRSASEXP-10000S: SAS Expansion cardAdd-on Applications• One click installation of add-on applications directly through local GUI• Application available for productivity, media, backup, surveillance, and many others• NETGEAR applications include Surveillance, Photo Sharing, Advanced configuration tools• Partner applications include BitTorrent Sync, Plex, Memeo, DVBlink• Community applications include Transmission, ownCloud, qBittorent, MySQL, VPN server, Syslog, Wordpress,joomla, Media Wiki, and others• Application availability subject to change• Applications may impact overall performance• Software Development Kit (SDK) available for 3rd party developersWarranty and SupportHardware Limited Warranty 5 years*Next-Business-Day (NBD) Replacement YesT echnical Support 90 days free from date of purchase** This product comes with a limited warranty that is valid only if purchased from a NETGEAR authorized reseller, and covers unmodified hardware, fans and internal power supplies – not software or external power supplies, and requires product registration at https:// or using the Insight App within 90 days of purchase; see https:///about/warranty for details. Intended for indoor use only.NETGEAR, the NETGEAR Logo, ReadyNAS, ReadyCLOUD, ReadyNAS Vault, and X-RAID are trademarks of NETGEAR, Inc. in the United States and/or other countries. Other brand names mentioned herein are for identification purposes only and may be trademarks of their respective holder(s). Information is subject to change without notice.© 2022 NETGEAR, Inc. All rights reserved.NETGEAR,Inc.350E.PlumeriaDrive,SanJose,CA95134-1911USA,1-888-NETGEAR(638-4327),E-mail:****************,DS-3312/4312S/4312X -25May22。

Disulfide by Design Version 1.20© Wayne State University 2003, All Rights Reserved09/16/03Users’ GuideAlan A. Dombkowski, Ph.D., Institute of Environmental Health Sciences,Wayne State University, Detroit, MI domski@Contents1 Description (2)Requirements (2)2 System3 Installation (2)4 Running Disulfide by Design (2)4.1 Loading a PDB file (3)4.2 Run (4)4.3 Output (4)4.4 SavingResults (4)4.5 Creating a mutant PDB file (5)5 Options (5)Intra-chain (5)and5.1 InterCβ for glycines (5)5.2 Building5.3 Chi3 torsion angle tolerance (5)5.4 Ca-Cb-S angle tolerance (6)Details (6)6 TechnicalNotes (7)7 Release8 References (7)1 DescriptionDisulfide by Design is an application for the rational design of disulfide bonds in proteins. For a given protein structural model, all residue pairs are rapidly assessed for proximity and geometry consistent with disulfide formation, assuming the residues were mutated to cysteines. The output displays residue pairs meeting the appropriate criteria. The input model will typically be a Protein Data Bank (PDB) structure for the protein of interest; however, structures developed through homology modeling may also be used. Engineered disulfides have proven useful for increasing the stability of proteins and to assist the investigation of protein dynamics and interactions. This software was written by Dr. Alan Dombkowski and based on algorithms created for disulfide identification in protein fold recognition methods (Dombkowski & Crippen, 2000). The Disulfide by Design algorithm has been successfully used for disulfide engineering (Anthony et al., 2002; Anthony & Burgess, 2002).2 System RequirementsDisulfide by Design is currently available for the Windows operating system. It has been tested with Windows 98, NT, 2000 and XP. The application uses about five megabytes of memory and less than one megabyte of disk space. Monitor resolution should be a minimum of 1024 x 768 with 16 or 32 bit color.3 InstallationSimply double click on “Disulfide by Design Install.exe” and the installer will step you through the installation process. A license agreement will be displayed during the installation process. Proceeding with installation requires agreement with the software license. Upon installation, an icon will be installed under the “Programs” tab of the “Start” menu. To run the program simply double-click the icon. The software can be uninstalled using the Add/Remove Programs tab of the control panel.4 Running Disulfide by DesignRunning Disulfide by Design is as simple as loading a PDB file then pressing “Run.” The default option settings are recommended for general use. However, it may be desirable to change option settings, such as to increase assessment criteria stringency. The options are discussed in greater detail below.4.1 Loading a PDB fileThe input file must be in PDB format with atomic coordinates. File selection isperformed with the “Load Structure” button. All residues with a complete main chainbackbone and a Cβ atom are used in the analysis. In the case of glycine, a Cβ will becreated if the “Build Cb for Gly” check box is selected. After the structure file has beenread a message is displayed showing the number of residues having a complete backbone and Cβ. For NMR structures with multiple models only the first model will be used.124.2 RunAfter successful loading of a PDB file, simply press “Run” to start the analysis. Each possible pair of residues will be assessed for potential disulfide formation, assuming the residues were mutated to cysteines. With the default setting, both inter and intra-chain disulfides are analyzed. Deselect the appropriate check box to change the intra/inter-chain setting.4.3 OutputThe output text box displays one line per potential disulfide. Each line shows a pair of residues that have the appropriate geometry to form a disulfide bond if the residues were mutated to cysteines. The analysis is based on the assumption that the mutations would not significantly perturb the protein backbone conformation. Each displayed disulfide meets the minimum geometric criteria, including user-selected parameters. The chain id, residue number, and original amino acid type are shown for each residue in the pair. Chain id and residue number are consistent with the input PDB designations. Also shown are the estimated χ3 torsion angle and an energy value in kcal/mol. χ3 angles of known disulfides have a bimodal distribution with peaks observed at +100 and -80 (Petersen et al., 1999), see figure in technical details. These values provide useful selection criteria for disulfide design. The estimated chirality and torsion angle are based on the best possible orientation of putative mutant cysteine Sγ atoms, as determined by an energy minimization performed within Disulfide by Design (see technical details below). The energy value is useful for comparison of potential disulfides to select the best possible candidates. Disulfides with a lower energy value are preferential to those with a higher score. The calculated energy is not intended as a comprehensive assessment of conformational energy, but it is provided to allow comparisons of prospective disulfide bonds. Figure 3 is a histogram of energy values calculated for 706 known disulfides using the Disulfide by Design algorithm. This data reveals the distribution of energy values for naturally occurring disulfides and may be helpful when selecting putative bonds for disulfide engineering. The mean energy value is 1.07 kcal/mol and the maximum observed value is 7.91 kcal/mol.4.4 Saving ResultsResults displayed in the output text box can be saved to a user-specified file using the “Save Results” button. Text is saved in tab-delimited format, so the data can easily be imported into Excel or other spreadsheet software.4.5 Creating a mutant PDB fileA modified form of the original input PDB file can be created by selecting one or more of the potential disulfides then pressing “Create PDB File.” Disulfides are selected by simply pointing the mouse at the desired line then left-clicking. Disulfides may be deselected by clicking a second time. For each disulfide selected, the original amino acids are replaced in the PDB file with cysteines. The respective SSBOND records are inserted near the beginning of the mutant PDB file. The mutant PDB file can be subsequently imported into molecular modeling software such as Rasmol for visualization of the designed disulfides.5 Options5.1 Inter and Intra-chainBy default, Disulfide by Design checks all potential inter and intra-chain disulfides. However, it may be desirable to restrict analysis to either inter or intra-chain. This is accomplished by simply deselecting the appropriate check box.5.2 Building Cβ for glycinesThe disulfide design algorithm requires coordinates for Cβ atoms to determine the potential for disulfide formation. Since glycine residues do not include a Cβ atom they cannot be used in the analysis unless a Cβ is created. The “Build Cb for Gly” check box enables the construction of Cβ atoms. The Cβ location is determined by using the coordinates of the residue backbone atoms. The algorithm was tested by building Cβatoms for cysteine residues of proteins with a known structure. The coordinates of the constructed atoms were compared with the actual Cβ locations, and the average distance was only 0.12 Å indicating accurate modeling of the Cβ atoms.5.3 Chi3 torsion angle toleranceThe χ3 torsion angle is formed by the Cβ-Sγ-Sγ-Cβ bonds, with rotation about the Sγ-Sγbond (see Figure 1 below). The distribution of χ3 angles observed in disulfides of known protein structures is bimodal with sharp peaks at +100 and -80 (see Figure 2 below). It may be desirable to restrict candidate disulfides to those having an estimated χ3 value that falls within the region of observed χ3 values. The χ3 angle tolerance can be selected in the options box. The default setting is +100 ± 30º and -80 ± 30º. If numerous putative disulfides are identified using the default setting it may be useful to decrease the tolerance resulting in a shorter list with preferential characteristics.5.4 Ca-Cb-S angle toleranceThe distribution of C α−C β−S γ angles observed in known disulfides has a peak near 115º and covers a range from approximately 105º to 125º (Petersen et al., 1999). The tolerance of this bond angle is selectable, with a default setting of 114.6 ± 10º.6 Technical DetailsFigure (1) represents a cysteine pair coupled by a disulfide bond. The approach uses a disulfide model with fixed C β-S γ and S γ-S γ bond lengths, 1.81 and 2.04 Å respectively, and fixed C β-S γ-S γ bond angles of 104.15º. These bond lengths and angles are consistent with values observed in a survey of protein disulfide bonds (Petersen et al ., 1999). The χ3 torsion angle, formed by rotation of the C β atoms about the S γ-S γ bond, is allowed to vary in the model and can be described as a function of the distance between C β atoms(Dombkowski & Crippen, 2000). To “fit” the disulfide model between a pair of residues, the algorithm simply rotates the χ3 angle to obtain a C β-C β distance that matches the C β-C β distance measured between the residues. Numerous S γ locations are possible, so all possible S γ orientations are examined and the atomic coordinates providing the lowest energy (E ij ) are selected, based on the χ1 and χ3 torsion angles and the two C α-C β-S γ angles. The χ1 torsion angle is defined by the N-C α-C β-S γ atoms . E ij is calculated per equations (1-4), where i and j are residue indices, θ is the C α-C β-S γ angle, and θ0 is set to 114.6º. Energy units are kcal/mol.)()()()()(3,1,1j i j i ij E E E E E E θθχχχ++++=(1)[])3cos(14.1)(11χχ+=E (2)[])1602cos(10.4)(33+−=χχE (3)[]200.55)(θθθ−=E (4)The energy calculation provides minima at χ3 values of +100º and -80º and χ1 values of ±60º and ±180º, consistent with values observed in the latest survey of disulfide bonds (Petersen et al ., 1999). Since the disulfide model uses fixed bond lengths, no term is included for bond stretching. The energy calculation provides a means to compare potential disulfides during disulfide design. The distribution of energy values for 706 known disulfide bonds reveals a mean energy value, calculated per equations (1-4), of 1.07 kcal/mol and a maximum of 7.91 kcal/mol.7 Release NotesChanges in version 1.20 include:•Corrected bug that caused text to go beyond the right-hand border of the dialog box with some terminal settings.Changes in version 1.12 include:•Energy units are now in kcal/mol.•For residues with multiple conformers only the first set of coordinates encountered are used.•For NMR structures with multiple models only the first model found in the PDB file is used.•Fixed bug in torsion angle calculation that caused crashes for a small number of PDB structures.8 ReferencesDombkowski A.A., 2003, Disulfide by Design: A computational method for the rational design of disulfide bonds in proteins, Bioinformatics, vol. 19 no. 14, 22 Sep.2003.Anthony, L.C. and Burgess, R.R., 2002, Conformational Flexibility in sigma 70 Region 2 during Transcription Initiation, J Biol Chem. Nov 29;277(48):46433-46441.Anthony, L.C., Dombkowski, A.A., and Burgess, R.R., 2002, Using disulfide engineering to study conformational changes in the β’260-309 coiled-coil region of E. Coli RNA polymerase during σ70 binding, J Bacteriol. May;184(10):2634-41.Dombkowski A.A.and Crippen G.M., 2000, Disulfide recognition in an optimized threading potential, Protein Engineering, vol. 13 no. 10, 679-689.Petersen, M., Jonson, P.H., and Petersen, S.B., 1999, Amino acid neighbours and detailed conformational analysis of cysteines in proteins, Protein Engineering, vol. 12, no 7, 535-548.-80+100 Figure 2。