BS62LV1600FCP55中文资料

- 格式:pdf

- 大小:216.26 KB

- 文档页数:10

部分VHS型录像机上磁鼓代换一揽表国产型号牌名适用录像机型号电路板编号SG-62-10 松下AG-6100 AG-6200 VEH0225松下AG6800 VEH0239 SG-62-20 松下NV-370 NV-380 or (VEH0171) VEH0218松下NV-300 NV-332 NV-333 NV-340 NV-390NV-2000 NV-3000 NV-7000 NV-7200 NV-7500NV-7800 NV-7850 NV-8200 NV-8170 NV-8400NV-8600 NV-8610 NV-8620VEH0099VEH0103VEH0131VEH0121SG-62-22ORION爱浪VH-1 VH-2SG-62-21 松下NV-230 NV-250 NV-260 NV-270 NV-280NV-450 NV-470 NV-480 NV-G9VEH0270VJB00D16SG-62-23 松下NV-G10 NV-G11 NV-G12 NV-G15 VEH0287松下NV-180 VEH0252松下NV-330 NV-777 VEH0177SG-62-21 松下NV-430 NV-460 VEH0286松下NV-600 VEH0209 SG-62-24 松下NV-730 VEH0256 松下NV-G7 VEH0295 SG-62-25 松下NV-G20 NV-J25 VEH0343SG-62-26 松下NV-G30 VEH0386 SG-62-27 松下NV-G33 NV-L15 VEH0385SG-62-28 松下NV-8500 VEH0180 JVC日本HR-2200 HR-3300 HR-3330 HR-3320 HR-3360 HR-3350HR-3660 HR-3860 HR-7610 HR-4100 HR-7200 HR-7600HR-7650 HR-4000 HR-7700 HR-D110 HR-D220 HR-D220HR-D121EC4P1214东芝V-55 V-57日立VT-3000AKAI日本赤井VP-7100 VP-7200 VS-9300 VS-9500 VS-9700 VS-9800VP-77 VP-83 VS-10 VS-1 VS-2 VS-3VS-5 VS-PIEV三菱日本HS-200 英国3V-01 3V-06 3V-16 3V-22 3V-30SG-62-30西徳VC-30 VR-7730 VR-2000 VR-6000 VR-9010 VR-70VR-80 VR-90 VR-3605 VR-3905 VR-3912 VR-3985V-320 V-321 V-323 V-326 VK-2140 VC-2830VK-37 VK-3301V V-250 V-300 V-301 V-302SG-62-31 JVC日本HR-D210EC FUNAI(福奈) VIP-1000 VIP-1400 VIP-3000 VIP-2500 VIP-3000 E-1100 DPE1194HBPOLARIS日本IV-300 IV-500 IV-700 VC-28 DPE1194HBSG-62-40MONEXE日本VCP-777 DPE1194HB SG-62-41 南朝鲜国内装斯塔VF-2215 乐音VF-2215 兰宝VD-888P 东洋900罗兰士宝LS-900VCP F-900T 和康VP-9100 TP-920KITT F-900 VD-8818凸鼓部分VHS 型录像机上磁鼓代换一揽表国产型号 牌 名 适 用 录 像 机 型 号 电路板编号 SG-62-42 南朝鲜国内装 佳韵VCP-9028 VCP -9038 佳威VCP-707D 佳声VP-4100 TP-4300 VCP-A704D VR-2600 VCP-980 LS-4130D 高士达CHV-1232 GHV-1240D GHV-1245D 北京牌VCP-4100 皇冠牌 金钱牌 东洋牌, 飞 梭VCP-4130D原机上磁鼓型号为 PAL-SP513 -209B 用 370代换SG-62-43FUNAI 福奈 VIP-3000触点连接方式 SG-62-44 PROSCO 日本 IV-707 370SG-62-50 日立日本 VT-33E VF-34E VT-11E VT-14 VT-930 VT-330EVT-340E VT-P10 VT-61E VT-5030E VT-63E VT-62E VTP10 VTP30593315 548992 5458282 5458993 IS-39V-OSG-62-51 日立日本 VT-136 VT-138 VT-426 VT-4275457478 SG-62-80东芝日本V-73 V-74 V-83 V-84 V-93 V-94 V-9870195152 TLC-137-T -V-OSG-62-60夏普日本VC-200 VC-2000 VC-8100 VC-9500 VC-9300 VC-900 VC-970 VC-220 VC-300 VC-9800 VC-9700 VC-3300 VC-381 VC-384 VC-385 VC-387 VC-481 VC-477 VC-9400 VC-930 VC-9600 VC-110 VC-386 VC-482DDRMU001HE DDRMU002HE 02 or 04,05,06 SG-62-70 ORION 爱浪 VH-2A VH-2B VH-2C VH-200 VH-3A VH-3BVH-3C VH-300 VH-400 VH-404 VH-555 VH-700 VH-704 VH-770 VH-844 VC-150 VC-180 VH-1000 VH-201 VH-303 VH-312 VH-33 VH-900 VH-10 V-88日立日本 VT660 5458704注以上表中SG 系列磁鼓系大连市电子研究所视频磁头厂产品嘉伟电器技术服务中心 20020405 秦 炎。

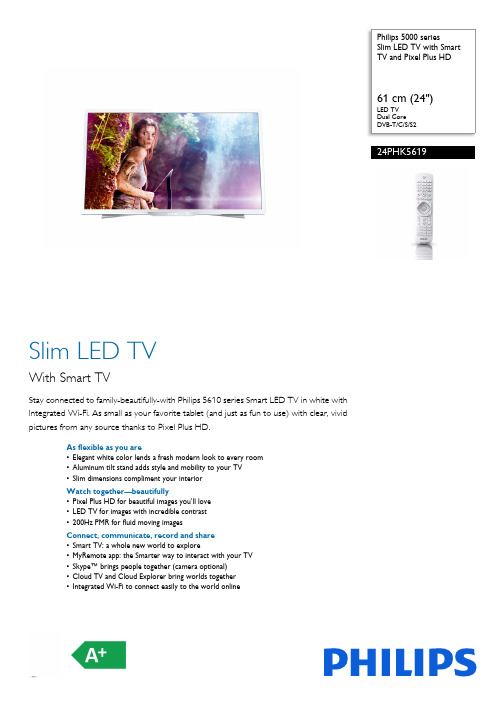

Philips 5000 seriesSlim LED TV with Smart TV and Pixel Plus HD61 cm (24")LED TV Dual Core DVB-T/C/S/S224PHK5619Slim LED TVWith Smart TVStay connected to family-beautifully-with Philips 5610 series Smart LED TV in white with Integrated Wi-Fi. As small as your favorite tablet (and just as fun to use) with clear, vivid pictures from any source thanks to Pixel Plus HD.As flexible as you are•Elegant white color lends a fresh modern look to every room •Aluminum tilt stand adds style and mobility to your TV •Slim dimensions compliment your interior Watch together—beautifully•Pixel Plus HD for beautiful images you’ll love •LED TV for images with incredible contrast •200Hz PMR for fluid moving imagesConnect, communicate, record and share •Smart TV: a whole new world to explore•MyRemote app: the Smarter way to interact with your TV •Skype™ brings people together (camera optional)•Cloud TV and Cloud Explorer bring worlds together •Integrated Wi-Fi to connect easily to the world onlineHighlightsModern white designBecause we know you want a small screen TV that looks as great as it performs, our design team paired an elegant frame of sophisticated white and metal veneer to create a fresh, modern design that compliments any room its in.Aluminum folded standThe benefit of a small screen TV is its mobility. But why sacrifice style for function? Designed like a picture frame, this stylish stand can either fold out to sit on a counter, or lay flush at the back to hang on a wall.Pixel Plus HDThere’s nothing like settling in to watch your favorite movie or documentary. And whether you stream online or watch a DVD, Philips Pixel Plus HD Engine delivers a more realistic picture thanks to brighter whites and blacker blacks.LED TVWith LED backlight you can enjoy low power consumption and beautiful lines combined with high brightness, incredible contrast and vibrant colors.200Hz Perfect Motion RateNothing beats the adrenaline rush of gaming,fast paced sporting events or action films.That's why this Philips TV has 200Hz PerfectMotion Rate; so you’ll enjoy fluid movingimages. Because even though your pulse mayjump, the image you’re watching shouldn’t.Smart TVDiscover a Smarter experience that liesbeyond traditional TV. Rent and streammovies, videos or games from online videostores. Watch catch-up TV from your favoritechannels and enjoy a growing selection ofonline apps such as Youtube.MyRemote*Control your Philips TV directly from yourSmart device. With the MyRemote app itsnever been easier stay up to date thanks to theTV Program Guide.Skype™ TV video calls*Add a new dimension to your calls and shareexperiences with the people that matter toyou, wherever they are. With Skype™ on yourTV, make voice and video calls from your livingroom. Just connect the optional Philips TVcamera (PTA317) to your TV and enjoyexcellent video and sound quality from thecomfort of your couch.Cloud TV* & Explorer"Because you’re unique, we think the way youwatch TV should be too. With it’s constantlygrowing selection, Philips Cloud TV lets youchoose from hundreds of TV channels fromaround the world. Cloud Explorer makessharing with friends near and far easy byallowing you to access your Dropbox™account via your TV, letting you view yourcontent on the big screen.Wi-fi integratedIntegrated Wi-Fi on your Philips Smart TVmakes connecting to your home networkquick and easy, allowing you to access a worldof content or share wirelessly at home.Slim profilePhilips Slim profile TV makes a statement withits sleek, sophisticated dimensions. After all,why shouldn’t your TV be as beautiful as it isfunctional?Issue date 2022-06-03 Version: 7.2.112 NC: 8670 001 11184 EAN: 87 12581 70840 5© 2022 Koninklijke Philips N.V.All Rights reserved.Specifications are subject to change without notice. Trademarks are the property of Koninklijke Philips N.V. or their respective owners.SpecificationsPicture/Display•Display: LED HD TV•Diagonal screen size: 24 inch / 61 cm•Panel resolution: 1366 x 768p•Aspect ratio: 4:3/16:9•Brightness: 350 cd/m²•Picture enhancement: Pixel Plus HD, 200Hz Perfect Motion Rate, Micro DimmingSmart TV•Interactive TV:HbbTV•SmartTV apps*: Catch-up TV, Netflix, Spotify, Online apps, Online Video stores, Open Internet browser, YouTube•Social TV: Skype, Twitter•TV programe guide*: 8 day Electronic Program GuideUser Interaction•Wireless interaction: SimplyShare, MultiRoom Client, Wi-fi Miracast Certified*, Cloud TV* and Cloud Explorer•Program: Pause TV, USB Recording*•Ease of Installation: Auto detect Philips devices, Device connection wizard, Network installation wizard, Settings assistant wizard•Ease of Use: One-stop Home button, Onscreen Usermanual•Firmware upgradeable: Firmware auto upgrade wizard, Firmware upgradeable via USB, Online firmware upgrade•Screen Format Adjustments: Basic - Fill Screen, Fit to Screen, Advance - Shift, Stretch, Zoom •Signal strength indication•Teletext: 1000 page Hypertext•My Remote App*: Control, Simply Share, TV Guide CPU•Processor type: Dual-CoreSound•Output power (RMS): 10W•Sound Enhancement: Incredible Surround, Clear Sound, Bass Enhancement, Auto Volume Leveler, Smart SoundConnectivity•Number of HDMI connections: 2•Number of component in (YPbPr): 1•Number of scarts(RGB/CVBS):1•Number of USBs: 1•Wireless connection: Wi-Fi 2x2 Integrated •Other connections: CI+1.3 certified, SatelliteConnector, Antenna IEC75, Common InterfacePlus (CI+), Ethernet-LAN RJ-45, Digital audio out(optical), PC-in VGA + Audio L/R in, Headphoneout, Service connector•EasyLink (HDMI-CEC): Remote control pass-through, System audio control, System standby,Auto subtitle shift (Philips)*, Pixel Plus link(Philips)*, One touch playMultimedia Applications•Video Playback Formats: Containers: AVI, MKV,H264/MPEG-4 AVC, MPEG-1, MPEG-2, MPEG-4,WMV9/VC1•Subtitles Formats Support: .AAS, .SMI, .SRT, .SSA,.SUB, .TXT•Music Playback Formats: AAC, AMR, LPCM, M4A,MP3, MPEG1 L1/2, WMA (v2 up to v9.2)•Picture Playback Formats: JPEG, BMP, GIF, JPS,PNG, PNSSupported Display Resolution•Computer inputs: up to 1920x1080 @ 60Hz•Video inputs: 24, 25, 30, 50, 60 Hz, up to1920x1080pTuner/Reception/Transmission•Digital TV: DVB-T/C/S/S2•MPEG Support: MPEG2, MPEG4•Video Playback: NTSC, PAL, SECAMPower•Mains power: AC 220 - 240 V 50/60Hz•Ambient temperature: 5 °C to 35 °C•Eu Energy Label power: 18 W•Annual energy consumption: 26 kW·h•Energy Label Class: A+•Standby power consumption: < 0.3 W•Power Saving Features: Auto switch-off timer, Ecomode, Picture mute (for radio)•Off mode power consumption: < 0.3Dimensions•Box dimensions(W x H x D):610 x 432 x 114 mm•Set dimensions(W x H x D): 552 x 332 x 55 mm•Set dimensions with stand (W x H x D):552 x 339 x 122 mm•Compatible wall mount: 75 x 75mm•Product weight: 3.4 kg•Product weight (+stand): 3.7 kg•Weight incl. Packaging: 4.8 kgAccessories•Included accessories: Remote Control, 2 x AAABatteries, Aluminum tilt stand, Power cord, Quickstart guide, Legal and safety brochure, WarrantyLeaflet•Optional accessories: Philips TV camera PTA317*MyRemote app and related functionalities varies per TV model andcountry, as well as smart device model and OS. For more detail,please visit: /TV.*For smart TV app, visit /TV to discover the servicesoffering in your country*Cloud TV offering depends on country availability and regulations*Compatibility depends on Wifi Miracast certification & Android 4.2or later. For more details please refer to your device documentation.*USB recording for digital channels only, recordings may be limited bybroadcast copy protection (CI+). Country and channel restrictionsmay apply.*Philips TV camera (PTA317) is sold separately.*The TV supports DVB reception for 'Free to air' broadcast. SpecificDVB operators may not be supported. An up to date list can befound in the FAQ section of the Philips support website. For someoperators Conditional Access and subscripction are required.Contact your operator for more information.*Energy consumption in kWh per year, based on the powerconsumption of the television operating 4 hours per day for 365days. The actual energy consumption will depend on how thetelevision is used.*(Philips) only compatible with specific Philips player device.*EPG and actual visibility (up to 8 days) is country and operatordependent.。

MX29LV160C T/B16M-BIT [2Mx8/1Mx16] CMOS SINGLE VOLTAGE3V ONLY FLASH MEMORY•Ready/Busy# pin (RY/BY#)- Provides a hardware method of detecting program or erase operation completion.•Sector protection- Hardware method to disable any combination of sectors from program or erase operations- Temporary sector unprotect allows code changes in previously locked sectors.•CFI (Common Flash Interface) compliant- Flash device parameters stored on the device and provide the host system to access•100,000 minimum erase/program cycles•Latch-up protected to 100mA from -1V to VCC+1V •Boot Sector Architecture - T = Top Boot Sector - B = Bottom Boot Sector•Low VCC write inhibit is equal to or less than 1.4V •Package type:- 44-pin SOP - 48-pin TSOP - 48-ball CSP- All Pb-free devices are RoHS Compliant •Compatibility with JEDEC standard- Pinout and software compatible with single-power supply Flash•10 years data retentionFEATURES•Extended single - supply voltage range 2.7V to 3.6V •2,097,152 x 8/1,048,576 x 16 switchable •Single power supply operation- 3.0V only operation for read, erase and program operation•Fully compatible with MX29LV160B device •Fast access time: 55R/70/90ns •Low power consumption- 30mA maximum active current - 0.2uA typical standby current •Command register architecture- Byte/word Programming (9us/11us typical)- Sector Erase (Sector structure 16K-Bytex1,8K-Bytex2, 32K-Bytex1, and 64K-Byte x31)•Auto Erase (chip & sector) and Auto Program- Automatically erase any combination of sectors with Erase Suspend capability.- Automatically program and verify data at specified address•Erase Suspend/Erase Resume- Suspends sector erase operation to read data from,or program data to, any sector that is not being erased,then resumes the erase.•Status Reply- Data# Polling & Toggle bit for detection of program and erase operation completion.GENERAL DESCRIPTIONThe MX29L V160C T/B is a 16-mega bit Flash memory organized as 2M bytes of 8 bits or 1M words of 16 bits.MXIC's Flash memories offer the most cost-effective and reliable read/write non-volatile random access memory. The MX29LV160C T/B is packaged in 44-pin SOP , 48-pin TSOP and 48-ball CSP . It is designed to be reprogrammed and erased in system or in standard EPROM programmers.The standard MX29LV160C T/B offers access time as fast as 55ns, allowing operation of high-speed micropro-cessors without wait states. To eliminate bus conten-tion, the MX29LV160C T/B has separate chip enable (CE#) and output enable (OE#) controls.MXIC's Flash memories augment EPROM functionality with in-circuit electrical erasure and programming. The MX29LV160C T/B uses a command register to manage this functionality. The command register allows for 100%TTL level control inputs and fixed power supply levels during erase and programming, while maintaining maxi-mum EPROM compatibility.MXIC Flash technology reliably stores memory contents even after 100,000 erase and program cycles. The MXIC cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and program operations produces reliable cy-cling. The MX29LV160C T/B uses a 2.7V~3.6V VCC supply to perform the High Reliability Erase and auto Program/Erase algorithms.The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up pro-tection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC + 1V.MX29LV160C T/BPIN CONFIGURATIONSPIN DESCRIPTIONSYMBOL PIN NAME A0~A19Address Input Q0~Q14Data Input/OutputQ15/A-1Q15(Word mode)/LSB addr(Byte mode)CE#Chip Enable Input WE#Write Enable Input BYTE#Word/Byte Selection input RESET#Hardware Reset Pin/Sector Protect UnlockOE#Output Enable Input RY/BY#Ready/Busy OutputVCC Power Supply Pin (2.7V~3.6V)GNDGround Pin48 TSOP (Standard Type) (12mm x 20mm)44 SOP(500 mil)A B C D E F GH6A13A12A14A15A16BYTE#Q15/A-1GND 5A9A8A10A11Q7Q14Q13Q64WE#RESET#NCA19Q5Q12VCC Q43RY/BY#NC A18NC Q2Q10Q11Q32A7A17A6A5Q0Q8Q9Q11A3A4A2A1A0CE#OE#GND48-Ball CSP 6mm x 8mm (Ball Pitch=0.8mm) Top View, Balls Facing Down234567891011121314151617181920212244434241403938373635343332313029282726252423RESET#A18A17A7A6A5A4A3A2A1A0CE#GND OE#Q0Q8Q1Q9Q2Q10Q3Q11WE#A19A8A9A10A11A12A13A14A15A16BYTE#GND Q15/A-1Q7Q14Q6Q13Q5Q12Q4VCCM X 29L V 160C T /BA15A14A13A12A11A10A9A8A19NC WE#RESET#NC NC RY/BY#A18A17A7A6A5A4A3A2A1123456789101112131415161718192021222324A16BYTE#GND Q15/A-1Q7Q14Q6Q13Q5Q12Q4VCC Q11Q3Q10Q2Q9Q1Q8Q0OE#GND CE#A0484746454443424140393837363534333231302928272625MX29LV160C T/BMX29LV160C T/BBLOCK STRUCTURETable 1: MX29LV160CT SECTOR ARCHITECTURESector Sector Size Address range Sector Address Byte Mode Word Mode Byte Mode(x8) Word Mode(x16)A19A18A17A16A15A14A13A12 SA064Kbytes32Kwords000000-00FFFF00000-07FFF00000X X X SA164Kbytes32Kwords010000-01FFFF08000-0FFFF00001X X X SA264Kbytes32Kwords020000-02FFFF10000-17FFF00010X X X SA364Kbytes32Kwords030000-03FFFF18000-1FFFF00011X X X SA464Kbytes32Kwords040000-04FFFF20000-27FFF00100X X X SA564Kbytes32Kwords050000-05FFFF28000-2FFFF00101X X X SA664Kbytes32Kwords060000-06FFFF30000-37FFF00110X X X SA764Kbytes32Kwords070000-07FFFF38000-3FFFF00111X X X SA864Kbytes32Kwords080000-08FFFF40000-47FFF01000X X X SA964Kbytes32Kwords090000-09FFFF48000-4FFFF01001X X X SA1064Kbytes32Kwords0A0000-0AFFFF50000-57FFF01010X X X SA1164Kbytes32Kwords0B0000-0BFFFF58000-5FFFF01011X X X SA1264Kbytes32Kwords0C0000-0CFFFF60000-67FFF01100X X X SA1364Kbytes32Kwords0D0000-0DFFFF68000-6FFFF01101X X X SA1464Kbytes32Kwords0E0000-0EFFFF70000-77FFF01110X X X SA1564Kbytes32Kwords0F0000-0FFFFF78000-7FFFF01111X X X SA1664Kbytes32Kwords100000-10FFFF80000-87FFF10000X X X SA1764Kbytes32Kwords110000-11FFFF88000-8FFFF10001X X X SA1864Kbytes32Kwords120000-12FFFF90000-97FFF10010X X X SA1964Kbytes32Kwords130000-13FFFF98000-9FFFF10011X X X SA2064Kbytes32Kwords140000-14FFFF A0000-A7FFF10100X X X SA2164Kbytes32Kwords150000-15FFFF A8000-AFFFF10101X X X SA2264Kbytes32Kwords160000-16FFFF B0000-B7FFF10110X X X SA2364Kbytes32Kwords170000-17FFFF B8000-BFFFF10111X X X SA2464Kbytes32Kwords180000-18FFFF C0000-C7FFF11000X X X SA2564Kbytes32Kwords190000-19FFFF C8000-CFFFF11001X X X SA2664Kbytes32Kwords1A0000-1AFFFF D0000-D7FFF11010X X X SA2764Kbytes32Kwords1B0000-1BFFFF D8000-DFFFF11011X X X SA2864Kbytes32Kwords1C0000-1CFFFF E0000-E7FFF11100X X X SA2964Kbytes32Kwords1D0000-1DFFFF E8000-EFFFF11101X X X SA3064Kbytes32Kwords1E0000-1EFFFF F0000-F7FFF11110X X X SA3132Kbytes16Kwords1F0000-1F7FFF F8000-FBFFF111110X X SA328Kbytes4Kwords1F8000-1F9FFF FC000-FCFFF11111100 SA338Kbytes4Kwords1FA000-1FBFFF FD000-FDFFF11111101 SA3416Kbytes8Kwords1FC000-1FFFFF FE000-FFFFF1111111XNote: Byte mode: address range A19:A-1, word mode:address range A19:A0.MX29LV160C T/BTable 2: MX29LV160CB SECTOR ARCHITECTURESector Sector Size Address range Sector Address Byte Mode Word Mode Byte Mode (x8)Word Mode (x16)A19A18A17A16A15A14A13A12 SA016Kbytes8Kwords000000-003FFF00000-01FFF0000000X SA18Kbytes4Kwords004000-005FFF02000-02FFF00000010 SA28Kbytes4Kwords006000-007FFF03000-03FFF00000011 SA332Kbytes16Kwords008000-00FFFF04000-07FFF000001X X SA464Kbytes32Kwords010000-01FFFF08000-0FFFF00001X X X SA564Kbytes32Kwords020000-02FFFF10000-17FFF00010X X X SA664Kbytes32Kwords030000-03FFFF18000-1FFFF00011X X X SA764Kbytes32Kwords040000-04FFFF20000-27FFF00100X X X SA864Kbytes32Kwords050000-05FFFF28000-2FFFF00101X X X SA964Kbytes32Kwords060000-06FFFF30000-37FFF00110X X X SA1064Kbytes32Kwords070000-07FFFF38000-3FFFF00111X X X SA1164Kbytes32Kwords080000-08FFFF40000-47FFF01000X X X SA1264Kbytes32Kwords090000-09FFFF48000-4FFFF01001X X X SA1364Kbytes32Kwords0A0000-0AFFFF50000-57FFF01010X X X SA1464Kbytes32Kwords0B0000-0BFFFF58000-5FFFF01011X X X SA1564Kbytes32Kwords0C0000-0CFFFF60000-67FFF01100X X X SA1664Kbytes32Kwords0D0000-0DFFFF68000-6FFFF01101X X X SA1764Kbytes32Kwords0E0000-0EFFFF70000-77FFF01110X X X SA1864Kbytes32Kwords0F0000-0FFFFF78000-7FFFF01111X X X SA1964Kbytes32Kwords100000-10FFFF80000-87FFF10000X X X SA2064Kbytes32Kwords110000-11FFFF88000-8FFFF10001X X X SA2164Kbytes32Kwords120000-12FFFF90000-97FFF10010X X X SA2264Kbytes32Kwords130000-13FFFF98000-9FFFF10011X X X SA2364Kbytes32Kwords140000-14FFFF A0000-A7FFF10100X X X SA2464Kbytes32Kwords150000-15FFFF A8000-AFFFF10101X X X SA2564Kbytes32Kwords160000-16FFFF B0000-B7FFF10110X X X SA2664Kbytes32Kwords170000-17FFFF B8000-BFFFF10111X X X SA2764Kbytes32Kwords180000-18FFFF C0000-C7FFF11000X X X SA2864Kbytes32Kwords190000-19FFFF C8000-CFFFF11001X X X SA2964Kbytes32Kwords1A0000-1AFFFF D0000-D7FFF11010X X X SA3064Kbytes32Kwords1B0000-1BFFFF D8000-DFFFF11011X X X SA3164Kbytes32Kwords1C0000-1CFFFF E0000-E7FFF11100X X X SA3264Kbytes32Kwords1D0000-1DFFFF E8000-EFFFF11101X X X SA3364Kbytes32Kwords1E0000-1EFFFF F0000-FFFFF11110X X X SA3464Kbytes32Kwords1F0000-1FFFFF F8000-FFFFF11111X X XNote: Byte mode:address range A19:A-1, word mode:address range A19:A0.MX29LV160C T/BBLOCK DIAGRAMCONTROL INPUT LOGICPROGRAM/ERASE HIGH VOLTAGEWRITE STATE MACHINE (WSM)STATE REGISTERFLASH ARRAYX-DECODERADDRESS LATCHAND BUFFERY -PASS GATEY -DECODERARRAY SOURCE HVCOMMAND DATADECODERCOMMAND DATA LATCHI/O BUFFERPGM DATA HVPROGRAM DATA LATCHSENSE AMPLIFIERQ0-Q15/A-1A0-A19CE#OE#WE#RESET#MX29LV160C T/BAUTOMATIC PROGRAMMINGThe MX29L V160C T/B is byte/word programmable using the Automatic Programming algorithm. The Automatic Programming algorithm makes the external system do not need to have time out sequence nor to verify the data programmed. The typical chip programming time at room temperature of the MX29LV160C T/B is less than 18 sec (byte)/12 sec (word).AUTOMATIC PROGRAMMING ALGORITHMMXIC's Automatic Programming algorithm requires the user to only write program set-up commands (including 2 unlock write cycle and A0H) and a program command (program data and address). The device automatically times the programming pulse width, provides the pro-gram verification, and counts the number of sequences.A status bit similar to Data# Polling and a status bit toggling between consecutive read cycles, provide feed-back to the user as to the status of the programming operation. Refer to write operation status, table 7, for more information on these status bits.AUTOMATIC CHIP ERASEThe entire chip is bulk erased using 10 ms erase pulses according to MXIC's Automatic Chip Erase algorithm. T ypical erasure at room temperature is accomplished in less than 25 second. The Automatic Erase algorithm automatically programs the entire array prior to electrical erase. The timing and verification of electrical erase are controlled internally within the device.AUTOMATIC SECTOR ERASEThe MX29L V160C T/B is sector(s) erasable using MXIC's Auto Sector Erase algorithm. The Automatic Sector Erase algorithm automatically programs the specified sector(s) prior to electrical erase. The timing and verifi-cation of electrical erase are controlled internally within the device. An erase operation can erase one sector, multiple sectors, or the entire device.AUTOMATIC ERASE ALGORITHMMXIC's Automatic Erase algorithm requires the user to write commands to the command register using stan-dard microprocessor write timings. The device will auto-matically pre-program and verify the entire array. Then the device automatically times the erase pulse width, provides the erase verification, and counts the number of sequences. A status bit toggling between consecutive read cycles provides feedback to the user as to the sta-tus of the erasing operation.Register contents serve as inputs to an internal state-machine which controls the erase and programming cir-cuitry. During write cycles, the command register inter-nally latches address and data needed for the program-ming and erase operations. During a system write cycle, addresses are latched on the falling edge, and data are latched on the rising edge of WE# or CE#, whichever happens first.MXIC's Flash technology combines years of EPROM experience to produce the highest levels of quality, reli-ability, and cost effectiveness. The MX29LV160C T/B electrically erases all bits simultaneously using Fowler-Nordheim tunneling. The bytes are programmed by us-ing the EPROM programming mechanism of hot electron injection.During a program cycle, the state-machine will control the program sequences and command register will not respond to any command set. During a Sector Erase cycle, the command register will only respond to Erase Suspend command. After Erase Suspend is completed, the device stays in read mode. After the state machine has completed its task, it will allow the command regis-ter to respond to its full command set.AUTOMATIC SELECTThe automatic select mode provides manufacturer and device identification, and sector protection verification, through identifier codes output on Q7~Q0. This mode is mainly adapted for programming equipment on the de-vice to be programmed with its programming algorithm. When programming by high voltage method, automatic select mode requires VID (11.5V to 12.5V) on address pin A9. Other address pin A6, A1 and A0 as referring to T able 3. In addition, to access the automatic select codes in-system, the host can issue the automatic select com-mand through the command register without requiring VID, as shown in table 5.To verify whether or not sector being protected, the sec-tor address must appear on the appropriate highest orderMX29LV160C T/BA19A11A9A8A6A5A1A0Description Mode CE#OE#WE#RESET# || | |Q15~Q0A12A10A7A2Read Silicon ID LLHHXXVID XL XLLC2HManufacture Code Device ID Word L L H H X X VID X L X L H 22C4H (Top Boot Block)Byte L L H H X X VID X L X L H XXC4H Device IDWordL L H H X X VID X L X L H 2249H (Bottom Boot Block)ByteL L H H X X VID X L X L H XX49H XX01HSector Protection LLHHSAXVIDXLXHL(protected)VerificationXX00H(unprotected)TABLE 3. MX29LV160C T/B AUTO SELECT MODE BUS OPERATION (A9=VID)NOTE: SA=Sector Address, X=Don't Care, L=Logic Low, H=Logic Highaddress bit (see T able 1 and T able 2). The rest of address bits, as shown in T able 3, are don't care. Once all neces-sary bits have been set as required, the programming equipment may read the corresponding identifier code on Q7~Q0.MX29LV160C T/BQUERY COMMAND AND COMMON FLASH INTERFACE (CFI) MODEMX29L V160C T/B is capable of operating in the CFI mode. This mode all the host system to determine the manu-facturer of the device such as operating parameters and configuration. T wo commands are required in CFI mode. Query command of CFI mode is placed first, then the Reset command exits CFI mode. These are described in T able 4.The single cycle Query command is valid only when the device is in the Read mode, including Erase Suspend, Standby mode, and Automatic Select mode; however, it is ignored otherwise.The Reset command exits from the CFI mode to the Read mode, or Erase Suspend mode, or Automatic Se-lect mode. The command is valid only when the device is in the CFI mode.Table 4-1. CFI mode: Identification Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) Query-unique ASCII string "QRY"201000512211005224120059 Primary vendor command set and control interface ID code2613000228140000 Address for primary algorithm extended query table2A1500402C160000 Alternate vendor command set and control interface ID code (none)2E17000030180000 Address for secondary algorithm extended query table (none)32190000341A0000 Table 4-2. CFI Mode: System Interface Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) VCC supply, minimum (2.7V)361B0027 VCC supply, maximum (3.6V)381C0036 VPP supply, minimum (none)3A1D0000 VPP supply, maximum (none)3C1E0000 Typical timeout for single word/byte write (2N us)3E1F0004 Typical timeout for Minimum size buffer write (2N us) (not supported)40200000 Typical timeout for individual sector erase (2N ms)4221000A Typical timeout for full chip erase (2N ms)44220000 Maximum timeout for single word/byte write times (2N X Typ)46230005 Maximum timeout for buffer write times (2N X Typ)48240000 Maximum timeout for individual sector erase times (2N X Typ)4A250004 Maximum timeout for full chip erase times (not supported)4C260000MX29LV160C T/B Table 4-3. CFI Mode: Device Geometry Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) Device size (2N bytes)4E270015 Flash device interface code (x8/x16 async.)5028000252290000 Maximum number of bytes in multi-byte write (not supported)542A0000562B0000 Number of erase sector regions582C0004 Erase sector region 1 information (refer to the CFI publication 100)5A2D00005C2E00005E2F004060300000 Erase sector region 2 information62310001643200006633002068340000 Erase sector region 3 information6A3500006C3600006E37008070380000 Erase sector region 4 information7239001E743A0000763B0000783C0001 Table 4-4. CFI Mode: Primary Vendor-Specific Extended Query Data Values(All values in these tables are in hexadecimal)Description Address Address Data(Byte Mode)(Word Mode) Query-unique ASCII string "PRI"804000508241005284420049 Major version number, ASCII86430031 Minor version number, ASCII88440030 Address sensitive unlock (0=required, 1= not required)8A450000 Erase suspend (2= to read and write)8C460002 Sector protect (N= # of sectors/group)8E470001 Temporary sector unprotect (1=supported)90480001 Sector protect/chip unprotect scheme92490004 Simultaneous R/W operation (0=not supported)944A0000 Burst mode type (0=not supported)964B0000 Page mode type (0=not supported)984C0000MX29LV160C T/Bin the improper sequence will reset the device to the read mode. Table 5 defines the valid register command sequences. Note that the Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Sector Erase operation is in progress.COMMAND DEFINITIONSDevice operations are selected by writing specific ad-dress and data sequences into the command register.Writing incorrect address and data values or writing them First Bus Second Bus Third Bus Fourth Bus Fifth Bus Sixth Bus CommandBusCycleCycleCycleCycleCycle CycleCycle AddrData Addr Data Addr Data Addr DataAddrData Addr DataReset 1XXXH F0H Read1RARDRead Silicon IDWord 4555H AAH 2AAH 55H 555H 90H ADI DDI Byte4AAAH AAH 555H 55H AAAH 90H ADI DDI Sector Protect Word4555H AAH 2AAH55H555H90H (SA)XX00H Verifyx02HXX01H Byte4AAAH AAH 555H55HAAAH90H (SA)00H x04H01H Program Word 4555H AAH 2AAH 55H 555H A0H PA PD Byte4AAAH AAH 555H 55H AAAH A0H PAPDChip Erase Word 6555H AAH 2AAH 55H 555H 80H 555H AAH 2AAH 55H 555H 10H Byte6AAAH AAH 555H 55H AAAH 80H AAAH AAH 555H 55H AAAH 10H Sector Erase Word 6555H AAH 2AAH 55H 555H 80H 555H AAH 2AAH 55H SA 30H Byte6AAAH AAH 555H 55HAAAH80H AAAH AAH555H 55HSA30HSector Erase Suspend 1XXXH B0H Sector Erase Resume 1XXXH 30H CFI QueryWord 155H 98ByteAAHTABLE 5. MX29L V160C T/B COMMAND DEFINITIONSNote:1. ADI = Address of Device identifier; A1=0, A0 = 0 for manufacturer code,A1=0, A0 = 1 for device code. A2-A19=do not care. (Refer to table 3)DDI = Data of Device identifier : C2H for manufacture code, C4H/49H (x8) and 22C4H/2249H (x16) for device code. X = X can be VIL or VIHRA=Address of memory location to be read. RD=Data to be read at location RA.2.PA = Address of memory location to be programmed. PD = Data to be programmed at location PA. SA = Address of the sector to be erased.3.The system should generate the following address patterns: 555H or 2AAH to Address A10~A0 in word mode/AAAH or 555H to Address A10~A-1 in byte mode.Address bit A11~A19=X=Don't care for all address commands except for Program Address (P A) and Sector Address (SA). Write Sequence may be initiated with A11~A19 in either state.4. For Sector Protect Verify operation: If read out data is 01H, it means the sector has been protected. If read out data is 00H,it means the sector is still not being protected.5. Any number of CFI data read cycles are permitted.MX29LV160C T/BTABLE 6. MX29L V160C T/B BUS OPERATIONADDRESS Q8~Q15 DESCRIPTION CE#OE#WE#RE- A19A11A9A8A6A5A1A0Q0~Q7BYTE BYTESET#A12A10A7A2=VIH=VIL Read L L H H AIN Dout Dout Q8~Q14=High ZQ15=A-1 Write L H L H AIN DIN(3)DINReset X X X L X High Z High Z High Z Temporary sector unlock X X X VID AIN DIN DIN High Z Output Disable L H H H X High Z High Z High Z Standby Vcc±X X Vcc±X High Z High Z High Z0.3V0.3VSector Protect L H L VID SA X X X L X H L DIN X XChip Unprotect L H L VID X X X X H X H L DIN X X Sector Protection Verify L L H H SA X VID X L X H L CODE(5)X XNOTES:1.Manufacturer and device codes may also be accessed via a command register write sequence. Refer to T able 4.2. VID is the high voltage, 11.5V to 12.5V.3.Refer to T able 5 for valid Data-In during a write operation.4.X can be VIL or VIH.5.Code=00H/XX00H means unprotected.Code=01H/XX01H means protected.6.A19~A12=Sector address for sector protect.7.The sector protect and chip unprotect functions may also be implemented via programming equipment.MX29LV160C T/BREQUIREMENTS FOR READING ARRAY DATAT o read array data from the outputs, the system must drive the CE# and OE# pins to VIL. CE# is the power control and selects the device. OE# is the output control and gates array data to the output pins. WE# should re-main at VIH.The internal state machine is set for reading array data upon device power-up, or after a hardware reset. This ensures that no spurious alteration of the memory con-tent occurs during the power transition. No command is necessary in this mode to obtain array data. Standard microprocessor read cycles that assert valid address on the device address inputs produce valid data on the device data outputs. The device remains enabled for read access until the command register contents are altered. WRITE COMMANDS/COMMAND SEQUENCESTo program data to the device or erase sectors of memory, the system must drive WE# and CE# to VIL, and OE# to VIH.An erase operation can erase one sector, multiple sec-tors, or the entire device. T able 1 and T able 2 indicate the address space that each sector occupies. A "sector ad-dress" consists of the address bits required to uniquely select a sector. The Writing specific address and data commands or sequences into the command register ini-tiates device operations. Table 5 defines the valid regis-ter command sequences. Writing incorrect address and data values or writing them in the improper sequence resets the device to reading array data. Section has de-tails on erasing a sector or the entire chip, or suspend-ing/resuming the erase operation.After the system writes the "read silicon-ID" and "sector protect verify" command sequence, the device enters the "read silicon-ID" and "sector protect verify" mode. The system can then read "read silicon-ID" and "sector protect verify" codes from the internal register (which is separate from the memory array) on Q7-Q0. Standard read cycle timings apply in this mode. Refer to the "read silicon-ID" and "sector protect verify" Mode and "read silicon-ID" and "sector protect verify" Command Se-quence section for more information.ICC2 in the DC Characteristics table represents the ac-tive current specification for the write mode. The "AC Characteristics" section contains timing specification table and timing diagrams for write operations. STANDBY MODEWhen using both pins of CE# and RESET#, the device enter CMOS Standby with both pins held at Vcc ± 0.3V. If CE# and RESET# are held at VIH, but not within the range of VCC ± 0.3V, the device will still be in the standby mode, but the standby current will be larger. During Auto Algorithm operation, Vcc active current (ICC2) is required even CE# = "H" until the operation is completed. The device can be read with standard access time (tCE) from either of these standby modes, before it is ready to read data.OUTPUT DISABLEWith the OE# input at a logic high level (VIH), output from the devices are disabled. This will cause the output pins to be in a high impedance state.RESET# OPERATIONThe RESET# pin provides a hardware method of reset-ting the device to reading array data. When the RESET# pin is driven low for at least a period of tRP, the device immediately terminates any operation in progress, tristates all output pins, and ignores all read/write com-mands for the duration of the RESET# pulse. The device also resets the internal state machine to reading array data. The operation that was interrupted should be re-initiated once the device is ready to accept another com-mand sequence, to ensure data integrity.Current is reduced for the duration of the RESET# pulse. When RESET# is held at VSS±0.3V, the device draws CMOS standby current (ICC4). If RESET# is held at VIL but not within VSS±0.3V, the standby current will be greater.The RESET# pin may be tied to system reset circuitry.A system reset would that also reset the Flash memory, enabling the system to read the boot-up firmware from the Flash memory.If RESET# is asserted during a program or erase opera-tion, the RY/BY# pin remains a "0" (busy) until the inter-MX29LV160C T/Bnal reset operation is complete, which requires a time of tREADY (during Embedded Algorithms). The system can thus monitor RY/BY# to determine whether the reset op-eration is complete. If RESET# is asserted when a pro-gram or erase operation is completed within a time of tREADY (not during Embedded Algorithms). The system can read data tRH after the RESET# pin returns to VIH. Refer to the AC Characteristics tables for RESET# pa-rameters and to Figure 22 for the timing diagram.READ/RESET COMMANDThe read or reset operation is initiated by writing the read/ reset command sequence into the command register. Microprocessor read cycles retrieve array data. The de-vice remains enabled for reads until the command regis-ter contents are altered.If program-fail or erase-fail happen, the write of F0H will reset the device to abort the operation. A valid com-mand must then be written to place the device in the desired state.SILICON-ID READ COMMANDFlash memories are intended for use in applications where the local CPU alters memory contents. As such, manu-facturer and device codes must be accessible while the device resides in the target system. PROM program-mers typically access signature codes by raising A9 to a high voltage (VID). However, multiplexing high voltage onto address lines is not generally desired system de-sign practice.The MX29LV160C T/B contains a Silicon-ID-Read op-eration to supple traditional PROM programming meth-odology. The operation is initiated by writing the read silicon ID command sequence into the command regis-ter. Following the command write, a read cycle with A1=VIL, A0=VIL retrieves the manufacturer code of C2H/ 00C2H. A read cycle with A1=VIL, A0=VIH returns the device code of C4H/22C4H for MX29L V160CT, 49H/2249H for MX29L V160CB.The system must write the reset command to exit the "Silicon-ID Read Command" code.AUTOMATIC CHIP ERASE COMMANDSChip erase is a six-bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command 80H. T wo more "unlock" write cycles are then followed by the chip erase command 10H. The device does not require the system to entirely pre-program prior to executing the Automatic Chip Erase. Upon executing the Automatic Chip Erase, the device will automatically program and verify the entire memory for an all-zero data pattern. When the device is auto-matically verified to contain an all-zero pattern, a self-timed chip erase and verify begin. The erase and verify operations are completed when the data on Q7 is "1" at which time the device returns to the Read mode. The system is not required to provide any control or timing during these operations.When using the Automatic Chip Erase algorithm, note that the erase automatically terminates when adequate erase margin has been achieved for the memory array (no erase verification command is required).If the Erase operation was unsuccessful, the data on Q5 is "1" (see Table 8), indicating the erase operation ex-ceed internal timing limit.The automatic erase begins on the rising edge of the last WE# or CE# pulse, whichever happens first in the com-mand sequence and terminates when either the data on Q7 is "1" at which time the device returns to the Read mode or the data on Q6 stops toggling for two consecu-tive read cycles at which time the device returns to the Read mode.。

BS62LV1600FI55中⽂资料Very Low Power CMOS SRAM 2M X 8 bitBS62LV1600Pb-Free and Green package materials are compliant to RoHSn FEATURESWide V CC operation voltage : 2.4V ~ 5.5V Very low power consumption : V CC = 3.0V Operation current : 46mA (Max.) a t 55ns 2mA (Max.) at 1MHz Standby current : 1.5uA (Typ.) at 25 O C V CC = 5.0V Operation current : 115mA (Max.) a t 55ns 10mA (Max.) a t 1MHz Standby current : 6.0uA (Typ.) at 25O C ? High speed access time : -55 55ns (Max.) at V CC :3.0~5.5V -70 70ns (Max.) at V CC : 2.7~5.5V ? Automatic power down when chip is deselected ? Easy expansion with CE1, CE2 and OE options ? Three state outputs and TTL compatible ? Fully static operation ? Data retention supply voltage as low as 1.5V n DESCRIPTIONThe BS62LV1600 is a high performance, very low power CMOS Static Random Access Memory organized as 2048K by 8 bits and operates form a wide range of 2.4V to 5.5V supply voltage.Advanced CMOS technology and circuit techniques provide both high speed and low power features with typical CMOS standby current of 1.5uA at 3.0V/25O C and maximum access time of 55ns at 3.0V/85O C.Easy memory expansion is provided by an active LOW chip enable (CE1), an active HIGH chip enable (CE2), and active LOW output enable (OE) and three-state output drivers.The BS62LV1600 has an automatic power down feature, reducing the power consumption significantly when chip is deselected. The BS62LV1600 is available in JEDEC standard 44-pin TSOP II and 48-ball BGA package.n POWER CONSUMPTIONPOWER DISSIPATIONSTANDBY(I CCSB1, Max)Operating(I CC , Max)V CC =5.0V V CC =3.0V PRODUCT FAMILYOPERATING TEMPERATUREV CC =5.0V V CC =3.0V1MHz10MHzf Max. 1MHz10MHzf Max.PKG TYPEBS62LV1600EC TSOP II-44 BS62LV1600FC Commercial +0O C to +70O C 50uA 8.0uA 9mA 48mA 113mA 1.5mA 19mA 45mABGA-48-0912 BS62LV1600EITSOP II-44 BS62LV1600FIIndustrial -40O C to +85O C100uA 16uA 10mA 50mA 115mA 2mA 20mA 46mABGA-48-0912n PIN CONFIGURATIONSn BLOCK DIAGRAMBrilliance Semiconductor, Inc. reserves the right to change products and specifications without notice.G H F E D C B A 1 2 3 4 5 6 A9 A11 A10 A19A12 A14 A13 A15 WE NC NC NC DQ7 A17 A16 A7 VSS VCC DQ2 DQ1 DQ6 DQ5 NC A5 OE A3 A0 A6 A4 A1A2CE2 NC NC NCCE1 DQ4 NC 48-ball BGA top view NC NC DQ0 VSS VCC DQ3 NC A18 A20 A8n TRUTH TABLEn ABSOLUTE MAXIMUM RATINGS (1)SYMBOL PARAMETER RATING UNITSV TERM Terminal Voltage withRespect to GND-0.5(2) to 7.0 VT BIAS Temperature UnderBias-40 to +125 O CT STG Storage Temperature -60 to +150 O CP T Power Dissipation 1.0 WI OUT DC Output Current 20 mA1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2. –2.0V in case of AC pulse width less than 30 ns. n OPERATING RANGERANGAMBIENTTEMPERATUREV CC Commercial 0O C to + 70O C 2.4V ~ 5.5VIndustrial -40O C to + 85O C 2.4V ~ 5.5Vn CAPACITANCE (1) (T A = 25O C, f = 1.0MHz) SYMBOL PAMAMETER CONDITIONS MAX. UNITS C INInputCapacitanceV IN = 0V 10 pFC IOInput/OutputCapacitanceV I/O = 0V 12 pF1. This parameter is guaranteed and not 100% tested.n DC ELECTRICAL CHARACTERISTICS (T A =-40O C to +85OC)1. Typical characteristics are at T A =25O C and not 100% tested.2. Undershoot: -1.0V in case of pulse width less than 20 ns.3. Overshoot: V CC +1.0V in case of pulse width less than 20 ns.4. F MAX =1/t RC.5. I CC(MAX.) is 45mA/113mA at V CC =3.0V/5.0V and T A =70O C.6. I CCSB1(MAX.) is 8.0uA/50uA at V CC =3.0V/5.0V and T A =70O C.n DATA RETENTION CHARACTERISTICS (T A = -40O C to +85OC)1. V CC =1.5V, T A =25O C and not 100% tested.2. t RC = Read Cycle Time.3. I CCRD(Max.) is4.0uA at T A =70O C.n LOW V CC DATA RETENTION WAVEFORM (1) (CE1 Controlled)Data Retention Mode V CCt CDRV CC t RV IHV IHCE1≧V CC - 0.2V V DR ≧1.5V CE1V CCn LOW V CC DATA RETENTION WAVEFORM (2) (CE2 Controlled)n AC TEST CONDITIONS (Test Load and Input/Output Reference)Input Pulse Levels Vcc / 0V Input Rise and Fall Times 1V/ns Input and Output Timing Reference Level 0.5Vcc t CLZ , t OLZ , t CHZ , t OHZ , t WHZ C L = 5pF+1TTL Output LoadOthersC L = 30pF+1TTL1. Including jig and scope capacitance.n KEY TO SWITCHING WAVEFORMSn AC ELECTRICAL CHARACTERISTICS (T A = -40O C to +85OC)READ CYCLECE2 Data Retention Mode V CC t CDR V CC t R V ILV IL V CCV DR ≧1.5V CE2≦0.2V 1 TTL ALL INPUT PULSES→← 90%V CC GND Rise Time : 1V/ns Fall Time : 1V/ns90%→← 10%10%n SWITCHING WAVEFORMS (READ CYCLE)READ CYCLE 1 (1,2,4)READ CYCLE 2 (1,3,4)READ CYCLE 3 (1, 4)NOTES:1. WE is high in read Cycle.2. Device is continuously selected when CE1 = V IL and CE2= V IH .3. Address valid prior to or coincident with CE1 transition low and/or CE2 transition high.4. OE = V IL .5. Transition is measured ± 500mV from steady state with C L = 5pF. The parameter is guaranteed but not 100% tested. t RC t OHt AA D OUT ADDRESS t OHD OUTCE2 CE1D OUTCE2 CE1 OE ADDRESSn AC ELECTRICAL CHARACTERISTICS (T A = -40OC to +85OC)WRITE CYCLEn SWITCHING WAVEFORMS (WRITE CYCLE)WRITE CYCLE 1 (1)t WCt WR1(3)t CW(11)t CW(11)t WP(2)t AWt OHZ(4,10)t AS t WR2(3)t DHt DWD IND OUTWECE2CE1OEADDRESS(5)(5)WRITE CYCLE 2 (1,6)NOTES:1. WE must be high during address transitions.2. The internal write time of the memory is defined by the overlap of CE1 and CE2 active and WE low. All signals must be active to initiate a write and any one signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the second transition edge of the signal that terminates the write.3. t WR is measured from the earlier of CE1 or WE going high or CE2 going low at the end of write cycle.4. During this period, DQ pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.5. If the CE1 low transition or the CE2 high transition occurs simultaneously with the WE low transitions or after the WE transition, output remain in a high impedance state.6. OE is continuously low (OE = V IL ).7. D OUT is the same phase of write data of this write cycle. 8. D OUT is the read data of next address.9. If CE1 is low and CE2 is high during this period, DQ pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them. 10. T ransition is measured ± 500mV from steady state with C L = 5pF. The parameter is guaranteed but not 100% tested. 11. t CW is measured from the later of CE1 going low or CE2 going high to the end of write.D IND OUTWE CE2 CE1ADDRESSn ORDERING INFORMATIONBSI (Brilliance Semiconductor Inc.) assumes no responsibility for the application or use of any product or circuit described herein. BSI does not authorize its products for use as critical components in any application in which the failure of the BSI product may be expected to result in significant injury or death, including life-support systems and critical medical instruments.n PACKAGE DIMENSIONSTSOP II-44n PACKAGE DIMENSIONS (continued)3: SYMBOL "N" IS THE NUMBER OF SOLDER BALLS.1: CONTROLLING DIMENSIONS ARE IN MILLIMETERS. 2: PIN#1 DOT MARKING BY LASER OR PAD PRINT.N EDNOTES:4812.09.0E1D1e3.755.250.75 48 mini-BGA (9mm x 12mm)n Revision HistoryRevision No. History Draft Date Remark2.2 Add Icc1 characteristic parameter Jan. 13, 2006Improve Iccsb1 spec.I-grade from 220uA to 100uA at 5.0V20uA to 16uA at 3.0VC-grade from 110uA to 50uA at 5.0V10uA to 8.0uA at 3.0V2.3 Change I-grade operation temperature range May. 25, 2006 - from –25O C to –40O C。

POWER DISSIPATION SPEED(ns)STANDBY (I CCSB1, Max)Operating(I CC , Max)PRODUCT FAMILY OPERATING TEMPERATUREVcc RANGEVcc=5.0VPKG TYPE BS62LV1029SC SOP-32BS62LV1029TC TSOP-32BS62LV1029STC STSOP-32BS62LV1029PC PDIP-32BS62LV1029JC SOJ-32BS62LV1029DC +0O C to +70OC4.5V ~5.5V 55/708.0uA 46mA DICE BS62LV1029SI SOP-32BS62LV1029TI TSOP-32BS62LV1029STI STSOP-32BS62LV1029PI PDIP-32BS62LV1029JI SOJ-32BS62LV1029DI-40O C to +85OC4.5V~5.5V 55/7020uA 47mA DICEVery Low Power/Voltage CMOS SRAM 128K X 8 bit•Vcc operation voltage : 4.5V ~ 5.5V •Very low power consumption :Vcc = 5.0V C-grade : 46mA (@55ns) operating currentI-grade : 47mA (@55ns) operating current C-grade : 38mA (@70ns) operating current I-grade : 39mA (@70ns) operating current 0.6uA (Typ.) CMOS standby current•High speed access time :-55 55ns -70 70ns•Automatic power down when chip is deselected •Three state outputs and TTL compatible •Fully static operation•Data retention supply voltage as low as 1.5V •Easy expansion with CE2, CE1, and OE optionsThe BS62LV1029 is a high performance, very low power CMOS Static Random Access Memory organized as 131,072 words by 8 bits and operates from a range of 4.5V to 5.5V supply voltage.Advanced CMOS technology and circuit techniques provide both high speed and low power features with a typical CMOS standby current of 0.6uA at 5V/25o C and maximum access time of 55ns at 5V/85o C.Easy memory expansion is provided by an active LOW chip enable (CE1), an active HIGH chip enable (CE2), and active LOW output enable (OE) and three-state output drivers.The BS62LV1029 has an automatic power down feature, reducing the power consumption significantly when chip is deselected.The BS62LV1029 is available in DICE form , JEDEC standard 32 pin 450mil Plastic SOP, 300mil Plastic SOJ, 600mil Plastic DIP, 8mmx13.4mm STSOP and 8mmx20mm TSOP.DESCRIPTIONFEATURESBLOCK DIAGRAMPRODUCT FAMILYPIN CONFIGURATIONSBrilliance Semiconductor, Inc . reserves the right to modify document contents without notice.BS62LV10293231302928272625242322212019181712345678910111213141516NC A16A14A12A7A6A5A4A3A2A1A0DQ0DQ1DQ2GNDVCC A15CE2WE A13A8A9A11OE A10CE1DQ7DQ6DQ5DQ4DQ332313029282726252423222120191817•BS62LV1029SC BS62LV1029SI BS62LV1029PC BS62LV1029PIBS62LV1029JCBS62LV1029JIA7Address Input BufferRow DecoderMemory Array 1024 x 1024Column I/O Write Driver Sense AmpColumn DecoderData BufferOutput Address Input BufferA3A2A1A0A10Data BufferInput ControlGndVdd OE WE CE1DQ7DQ6DQ5DQ4DQ3DQ2DQ1DQ0A14A9A11A8A13A12A68888141281024102420A16A15A4A5CE2BSIOE A10CE1DQ7DQ6DQ5DQ4DQ3GND DQ2DQ1DQ0A0A1A2A312345678910111213141516A11A9A8A13WE CE2A15VCC NC A16A14A12A7A6A5A4•BS62LV1029TC BS62LV1029STC BS62LV1029TI BS62LV1029STI55ns :4.5~5.5V 70ns :4.5~5.5VVcc=5.0V55ns70ns38mA39mASYMBOLPARAMETERCONDITIONSMAX.UNITC IN InputCapacitanceV IN =0V 6pF C DQ Input/Output Capacitance V I/O =0V 8pFABSOLUTE MAXIMUM RATINGS (1)OPERATING RANGECAPACITANCE (1) (TA = 25o C, f = 1.0 MHz)1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operationalsections of this specification is not implied. Exposure to absolutemaximum rating conditions for extended periods may affect reliability.1. This parameter is guaranteed and not 100% tested.SYMBOL PARAMETERRATINGUNITSV TERM Terminal Voltage with Respect to GND -0.5 to Vcc+0.5VT BIAS Temperature Under Bias -40 to +85OC T STG Storage Temperature -60 to +150OCP T Power Dissipation 1.0W I OUTDC Output Current20mARANGEAMBIENT TEMPERATUREVccCommercial 0O C to +70O C 4.5V ~ 5.5V Industrial-40O C to +85O C4.5V ~5.5VTRUTH TABLEPIN DESCRIPTIONSNameFunctionA0-A16 Address Input These 17 address inputs select one of the 131,072x 8-bit words in the RAM CE1 Chip Enable 1 InputCE2 Chip Enable 2 InputCE1 is active LOW and CE2 is active HIGH. Both chip enables must be active when data read from or write to the device. If either chip enable is not active, the device is deselected and is in a standby power mode. The DQ pins will be in the highimpedance state when the device is deselected.WE Write Enable InputThe write enable input is active LOW and controls read and write operations. With the chip selected, when WE is HIGH and OE is LOW, output data will be present on the DQ pins; when WE is LOW, the data present on the DQ pins will be written into the selected memory location.OE Output Enable InputThe output enable input is active LOW. If the output enable is active while the chip is selected and the write enable is inactive, data will be present on the DQ pins and they will be enabled. The DQ pins will be in the high impedance state when OE is inactive.DQ0-DQ7 Data Input/Output Ports These 8 bi-directional ports are used to read data from or write data into the RAM.Vcc Power Supply GndGroundMODE WE CE1CE2OE I/O OPERATIONVcc CURRENT X H X X Not selected (Power Down)X X L X High Z I CCSB , I CCSB1Output DisabledH L H H High Z I CC Read H L H L D OUT I CC WriteLLHXD INI CCPARAMETERNAMEPARAMETER TEST CONDITIONSMIN. TYP . (1) MAX.UNITS V IL Guaranteed Input LowVoltage (2)Vcc=5.0V -0.5 -- 0.8VV IH Guaranteed Input HighVoltage (2)Vcc=5.0V2.2 -- V cc +0.3 V I ILInput Leakage Current Vcc = Max, V IN = 0V to Vcc-- -- 1 uA I LO Output Leakage CurrentVcc = Max, CE1= V IH , CE2= V IL, orOE = V IH , V I/O = 0V to Vcc -- -- 1 uAV OL Output Low Voltage Vcc = Max, I OL = 2.0mA Vcc=5.0V -- -- 0.4 V V OH Output High VoltageVcc = Min, I OH = -1.0mAVcc=5.0V2.4 -- -- V 55ns -- -- 47 I CC (5)Operating Power Supply Current CE1 = V IL , or CE2 = V IH , I DQ = 0mA, F = Fmax (3)70nsVcc=5.0V-- -- 39mAI CCSB Standby Current-TTLCE1 = V IH , or CE2 = V IL ,I DQ = 0mAVcc=5.0V-- -- 1.0 mAI CCSB1(4)Standby Current-CMOSCE1≧Vcc-0.2V or CE2≦0.2V,V IN ≧Vcc-0.2V or V IN ≦0.2VVcc=5.0V-- 0.6 20 uA1. Typical characteristics are at T A = 25o C.2. These are absolute values with respect to device ground and all overshoots due to system or tester notice are included.3. Fmax = 1/t RC .4. I cc SB1_Max.is 8.0uA at Vcc=5.0V and T A =70o C. 5. Icc _Max.is 46mA(@55ns)/38mA(@70ns) at Vcc=5.0V and T A = 0o C~70o C.DATA RETENTION CHARACTERISTICS ( TA = -40o C to + 85o C )1. Vcc = 1.5V,T A = + 25O C2.t RC = Read Cycle Time3. Icc DR_MAX.is 0.2uA at T A =70O C. DC ELECTRICAL CHARACTERISTICS ( TA = -40o C to + 85o C )LOW V CC DATA RETENTION WAVEFORM (1) ( CE1 Controlled )CE1Data Retention ModeVcct CDRVcct RV IHV IHVccV DR 1.5V≥CE1 Vcc -0.2V≥ LOW V CC DATA RETENTION WAVEFORM (2) ( CE2 Controlled )SYMBOLPARAMETERTEST CONDITIONSMIN. TYP . (1) MAX.UNITSV DR Vcc for Data Retention CE1 ≧ Vcc - 0.2V or CE2 ≦ 0.2V,V IN ≧ Vcc - 0.2V or V IN ≦ 0.2V 1.5 -- -- V I CCDR (3) Data Retention Current CE1 ≧ Vcc - 0.2V or CE2 ≦ 0.2V,V IN ≧ Vcc - 0.2V or V IN ≦ 0.2V -- 0.05 0.3 uA t CDR Chip Deselect to Data Retention Time0 -- -- ns t ROperation Recovery TimeSee Retention WaveformT RC (2)-- --nsCE2Data Retention ModeVcct CDRVcct RV ILV IL VccV DR ≧1.5VCE2 ≦0.2VKEY TO SWITCHING WAVEFORMSWAVEFORMINPUTS OUTPUTS MUST BE STEADY MAY CHANGE FROM H TO L DON T CARE:ANY CHANGE PERMITTED DOES NOT APPLYMUST BE STEADY WILL BE CHANGEFROM H TO L CHANGE :STATEUNKNOWN CENTERLINE IS HIGH IMPEDANCE ”OFF ”STATEMAY CHANGE FROM L TO H WILL BE CHANGEFROM L TO H ,AC TEST CONDITIONS(Test Load and Input/Output Reference)Input Pulse LevelsVcc / 0V Input Rise and Fall Times1V/ns Input and OutputTiming Reference Level 0.5VccOutput LoadC L = 30pF+1TTL C L = 100pF+1TTLAC ELECTRICAL CHARACTERISTICS ( TA = -40o C to + 85o C )READ CYCLEJEDECPARAMETERNAMENAMEDESCRIPTIONUNIT t AVAX t RC Read Cycle Time 55----70----ns t AVQV t AA Address Access Time ----55----70ns t E1LQV t ACS1Chip Select Access Time (CE1)----55----70ns t E2HOV t ACS2Chip Select Access Time (CE2)----55----70ns t GLQV t OE Output Enable to Output Valid ----30----40ns t E1LQX t CLZ1Chip Select to Output Low Z (CE1)10----10----ns t E2HOX t CLZ2Chip Select to Output Low Z (CE2)10----10----ns t GLQX t OLZ Output Enable to Output in Low Z 10----10----ns t E1HQZ t CHZ1Chip Deselect to Output in High Z (CE1)----35----40ns t E2HQZ t CHZ2Chip Deselect to Output in High Z (CE2)----35----40ns t GH QZ t OHZ Output Disable to Output in High Z ----30----35ns t AXOXt OHData Hold from Address Change10----10----nsPARAMETERCYCLE TIME : 55ns MIN. TYP. MAX.(Vcc = 4.5~5.5V)MIN. TYP. MAX.(Vcc = 4.5~5.5V)CYCLE TIME : 70nsREAD CYCLE3(1,4)READ CYCLE2(1,3,4)NOTES:1. WE is high in read Cycle.2. Device is continuously selected when CE1 =V IL and CE2=V IH.3. Address valid prior to or coincident with CE1 transition low and/or CE2 transition high.4. OE =V IL .5. The parameter is guaranteed but not 100% tested.tCLZ(5)D OUTCE2CE1(5)t ACS2tACS1tOHt RCtOEtCLZ2tCHZ2(2,5)D OUTCE2CE1OEADDRESS(5)tCLZ1(5)t ACS1t ACS2t CHZ1(1,5)t OHZ (5)tOLZtAAtCHZ1,tCHZ2SWITCHING WAVEFORMS (READ CYCLE)READ CYCLE1(1,2,4)t RCt OHt AAD OUTADDRESSt OHWRITE CYCLE1(1)t WR1t WC(3)t CW(11)(11)t CW(2)t WPtAWt OHZ(4,10)t ASt WR2(3)t DHt DWD IND OUTWECE2CE1OEADDRESS(5)(5)AC ELECTRICAL CHARACTERISTICS ( TA = -40o C to + 85o C )WRITE CYCLEJEDECPARAMETERNAMEPARAMETERNAMEDESCRIPTIONUNIT t AVAX t WC Write Cycle Time55----70----ns t E1LWH t CW Chip Select to End of Write 55----70----ns t AVWL t AS Address Set up Time 0----0----ns t AVWH t AW Address Valid to End of Write 55----70----ns t WLWH t WP Write Pulse Width 35----50----ns t WHAX t WR1Write Recovery Time (CE1 , WE)0----0----ns t E2L AX t WR2Write Recovery Time (CE2)0----0----ns t WLOZ t WHZ Write to Output in High Z ----25----30ns t DVWH t DW Data to Write Time Overlap 25----30----ns t WHDX t DH Data Hold from Write Time 0----0----ns t GHOZ t OHZ Output Disable to Output in High Z ----25----30ns t WHQXt OWEnd of Write to Output Active5----5----nsCYCLE TIME : 55ns MIN. TYP. MAX.MIN. TYP. MAX.(Vcc = 4.5~5.5V)(Vcc = 4.5~5.5V) SWITCHING WAVEFORMS (WRITE CYCLE)CYCLE TIME : 70nsNOTES:1. WE must be high during address transitions.2. The internal write time of the memory is defined by the overlap of CE1 and CE2 active and WE low. All signals must be active to initiate a write and any one signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the second transition edge of the signal that terminates the write.3. T WR is measured from the earlier of CE1 or WE going high or CE2 going low at the end of write cycle.4. During this period, DQ pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.5. If the CE1 low transition or the CE2 high transition occurs simultaneously with the WE low transitions or after the WE transition, output remain in a high impedance state.6. OE is continuously low (OE =V IL ).7.D OUT is the same phase of write data of this write cycle.8.D OUT is the read data of next address.9. If CE1 is low and CE2 is high during this period, DQ pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them.10. The parameter is guaranteed but not 100% tested.11.T CW is measured from the later of CE1 going low or CE2 going high to the end of write.WRITE CYCLE2(1,6)t WCtCW(11)(11)t CW(2)t WPtAWt WHZ(4,10)t ASt WR2(3)t DHt DWD IND OUTWECE2CE1ADDRESS(5)(5)t OW(7)(8)(8,9)ORDERING INFORMATIONPACKAGE DIMENSIONSBASE METALWITH PLATINGc c1SECTION A-Ab1bSOP -32Note:BSI (Brilliance Semiconductor Inc.) assumes no responsibility for the application or use of any product or circuit described herein. BSI does not authorize its products for use as critical components in any application in which the failure of the BSI product may be expected to result in significant injury or death, including life-support systems and critical medical instruments.PACKAGE J: SOJ S: SOP P: PDIPT: TSOP (8mm x 20mm)ST: Small TSOP (8mm x 13.4mm)D: DICEBS62LV1029 X X Z Y YGRADEC: +0o C ~ +70o C I: -40o C ~ +85o C SPEED 55: 55ns 70: 70nsPKG MATERIAL -: Normal G: Green P:Pb freeTSOP -32STSOP -32PDIP -32SOJ -32。

PhilipsLCD monitor Array140 cm (55")Full HDBDL5545EEntice your target audiencewith stunning picture clarity in full HDDeliver your marketing messages in style with this cost-effective 140 cm (55") LCDdisplay. With a wide array of features this full HD display is sure to leave your audiencespellbound.Operational flexibility•Open Pluggable Specification Slot•Display Port for faster graphics support•SmartPower for energy saving•Smart insert in the backcover to place a small pc•Enhanced zoom feature supports tiled matrix applications•Remote Management and Configuration via RS232•Many Functions.One WireOptimized for public viewing•Full HD LCD display, 1920x1080p•Slim bezel design for a stylish lookLower total cost of ownership•Brightness automatically adjusts with ambient conditions•Advanced anti image sticking functionHighlightsOPS SlotDeveloped for the Digital Signage market, the Open Pluggable Specification (OPS) slot is designed to make changing or upgrading your media player mere child’s play. Simply plug your media player in to the display - and you’re ready. No matter whether you have an entry level, mid-range or high-end media player, OPS is fully compatible bringing you a lower TCO over the longer term.Display PortEnjoy crystal clear images with the high-bandwidth graphics support of the Display Port. As well as transmitting full high-definition video the Display Port will also transmit audio, thus eliminating the need for extra cables. Slim bezelA slim bezel design adds a stylish look to a public display to nicely blend in just about any environment. Furthermore this design makes the display ideal for tiled matrix video walls. Full HD LCD display 1920x1080pThis display has a resolution that is referred to as Full HD. The state-of-the-art LCD screen technology has the full high-definition widescreen resolution of 1080 progressive lines, each with 1920 pixels. This allows the best possible picture quality for HD input signals with up to 1080 lines. It produces brilliant flicker-free progressive scan pictures with optimum brightness and superb colors. This vibrant and sharp image will provide youwith an enhanced viewing experience.Smart insertProfessional PC's are part of most publicsignage installations. Quite often they increasethe overall depth to the display and cause a lotof cable clutter. So we have designed thisdisplay with Smart insert in thebackcoverwhich is ideal for the integration of aprofessional small form factor PC. On top ofthat, the cable management system offers agreat solution to keep your cables neat andprofessional looking.SmartPowerThe backlight intensity can be controlled andpre-set by the system to reduce the powerconsumption by up to 50%, which savessubstantially on energy costs.Zoom function for tiled matrixThe internal zoom function enables easyimplementation of a video wall matrix, withoutthe need for expensive external equipment.Capable of many different configurations,creating a stunning video wall has becomesimplicity itself.Advanced anti image stickingStatic images left on-screen for extendedperiods of time may leave a "ghost image" orimage sticking effect on LCD displays.Although image sticking in LCD displays is notpermanent, you want to prevent this tohappen, especially in locations where contentis shown 24/7.Automatic brightness controlThe adjustment of display settings tocorrespond with ambient light without userintervention.Remote Management:: RS232Remote Management allows the user tocontrol and adjust the displays remotely via theRS232 protocol. Using CEC commands, youare able to have full control over all thedisplays in your signage network at any time.One WireTake full control of your display by running alloperational commands as well as your videosignal through just one single HDMI cable. Thisunique feature makes it so much easier andmore convenient to ensure the smoothrunning and maintenance of your display.Consumer Electronics Control (CEC)commands make finding out vital informationabout your display absolute childsplay.Issue date 2022-04-21Version: 4.6.112 NC: 8670 000 76927EAN: 87 12581 60488 2© 2022 Koninklijke Philips N.V.All Rights reserved.Specifications are subject to change without notice. Trademarks are the property of Koninklijke Philips N.V. or their respective owners.SpecificationsPicture/Display•Panel resolution: 1920x1080p•Optimum resolution: 1920 x 1080 @ 60 Hz •Brightness: 500 cd/m²•Contrast ratio (typical): 5000:1•Response time (typical): 8 ms •Aspect ratio: 16:9•Viewing angle (H / V): 178 / 178 degree •Display colors: 1.07 Billion•Diagonal screen size: 55 inch / 139.7 cm •Pixel pitch: 0.63 x 0.63mm•Display screen type: LCD Full HD W-UXGA Act. matrix•Picture enhancement: 3/2 - 2/2 motion pull down, 3D Combfilter, Motion compens. deinterlacing, Progressive scan, 3D MA deinterlacing, Dynamic contrast enhancementSupported Display Resolution•Computer formats Resolution Refresh rate 640 x 480 60, 67, 72, 75Hz 800 x 600 56, 60, 72, 75Hz 1024 x 768 60Hz 1280 x 768 60Hz 1280 x 800 60Hz 1280 x 1024 60Hz 1360 x 768 60Hz 1366 x 768 60Hz 1440 x 900 60Hz 1600 x 1200 60Hz 1920 x 1080 60Hz 1920 x 1200 60Hz •Video formats Resolution Refresh rate 480i 60Hz 480p 60Hz 576p 50Hz 576i 50Hz 720p 50, 60Hz 1080i 50, 60Hz 1080p 50, 60HzConnectivity•PC: VGA-in D-Sub 15HD, VGA-out D-Sub 15HD, DVI-D x1, RS232 D-Sub9, RS232 D-sub9 output, 3.5 mm PC audio input x1•AV input: Component (BNC) x1, Audio (L/R) x2•AV output: Audio (L/R) x2•Other connections: OPS, AC-out, HDMI, DisplayPortConvenience•Picture in picture: PBP, PIP, POP •Signal Loop Through: RS232, VGA •Keyboard control: Hidden, Lockable•Ease of installation: AC Out, Carrying Handles, Smart Insert•Energy saving functions: Ambient light sensor, Smart Power•Packaging: Reusable box•Network controllable: RS232•Tiled Matrix: Up to 5 x 5Dimensions•Bezel thickness: 42.2 mm / 1.6"•Set dimensions (W x H x D): 1299 x 769.8 x 129.9 mm•Set dimensions in inch (W x H x D): 51.1 x 30.3 x 5.1 inch •Product weight: 42.7 kg •Product weight (lb): 88•VESA Mount: 400 x 200 / 400 x 400 mmOperating conditions•Temperature range (operation): 0 - 40 °C •Relative humidity: 5 - 90 %•MTBF: 60,000 hour(s)Power•Standby power consumption: <0.5W •Consumption (On mode): 215W (Typ)Sound•Built-in speakers: 2 x 7W (RMS)Accessories•Included accessories: Remote Control, Batteries for remote control, AC Power Cord, VGA cable, User manual on CD-ROM, Quick start guide •Optional accessories: Fixed wall mount, Flexible wall mount, Ceiling mount •Stand: BM05211Miscellaneous•On-Screen Display Languages: English, French, German, Italian, Polish, Turkish, Russian, Simplified Chinese•Regulatory approvals: CE, FCC, Class B, UL/cUL, CCC, RoHSPackaging dimensions•EAN: 87 12581 60488 2•Number of products included: 1•Packaging type: Carton。

Philips 6000 series4K Ultra Slim Smart LED TV with Pixel Plus UltraHD139 cm (55") 4K Ultra HD LED TV Quad CoreDVB-T/T255PUT61024K Ultra Slim Smart LED TVwith Pixel Plus Ultra HDEnjoy functional elegance and smart connectivity. The Philips 6100 Series boasts 4K Ultra HD picture quality for superb detail. Better still, its built-in Smart TV is easy to use - making it an excellent choice for effortless entertainment.The right features presented elegantly•Ultra Slim lines for a refined profilePassionate about Picture Quality•4K Ultra HD is unlike any resolution you’ve ever seen before•Discover Ultra HD Picture Quality with Pixel Plus Ultra HD•Micro Dimming optimizes the contrast on your TVConnect to a bigger world with this Smart TV•Smart TV: a whole new world to exploreHighlightsUltra Slim profileSleek. Cutting edge. Refined. Precise. The Philips Ultra Slim silhouette. That something so slim can inspire so much interest shouldn’t be surprising, given how much sophistication it will bring to your décor.4K Ultra HDUltra HD TV has four times the resolution of a conventional Full HD TV. With over 8 million pixels and our unique Ultra Resolution Upscaling technology, you'll experience the best possible picture quality. The higher the quality of your original content, the better images and resolution you will be able to experience. Enjoy improved sharpness,increased depth perception, superior contrast, smooth natural motion, and flawless details.Pixel Plus Ultra HDExperience 4K Ultra HD sharpness with the Philips Pixel Plus Ultra HD engine. It optimizes picture quality to deliver smooth, fluid images with incredible detail and depth – Enjoy sharper 4K images with brighter whites and blacker blacks every time.Smart TVDiscover a Smarter experience that lies beyond traditional TV. Rent and stream movies, videos or games from online videostores. Watch catch-up TV from your favorite channels and enjoy a growing selection of online apps with Smart TV.Micro DimmingThanks to our special software that analyzes the picture in 6400 different zones and adjusts it accordingly, you’ll enjoy incredible contrast and image quality for a truly lifelike visualexperience.Issue date 2018-07-16 Version: 6.2.212 NC: 8670 001 44867 EAN: 87 18863 01203 1© 2018 Koninklijke Philips N.V.All Rights reserved.Specifications are subject to change without notice. Trademarks are the property of Koninklijke Philips N.V. or their respective owners.SpecificationsPicture/Display•Display: 4K Ultra HD LED•Panel resolution: 3840x2160•Aspect ratio: 16:9•Brightness: 350 cd/m²•Picture enhancement: Pixel Plus Ultra HD, Micro DimmingSmart TV Features•User Interaction: MultiRoom Client, SimplyShare, Wi-Fi Miracast Certified*•Interactive TV:HbbTV•Program: Pause TV, USB Recording*•SmartTV apps*: Online Video Stores, Open Internet Browser, Social TV, TV on Demand, Youtube, Netflix TV•Ease of Installation: Auto detect Philips devices, Device connection wizard, Network installation wizard, Settings assistant wizard•Firmware upgradeable: Firmware auto upgrade wizard, Firmware upgradeable via USB, Online firmware upgrade•Screen Format Adjustments: Advance - Shift, Basic - Fill Screen, Fit to Screen, Zoom, Stretch •Philips TV Remote app*: Apps, Channels, Control, NowOnTV, TV Guide, Video On Demand Sound•Output power (RMS): 20W•Sound Enhancement: Incredible Surround, Clear Sound, Auto Volume Leveller, Smart Sound Connectivity•Number of HDMI connections: 4•Number of component in (YPbPr): 1•Number of AV connections: 1•Number of USBs: 3•Wireless connections: Wi-Fi 11n 2x2 integrated, Wi-Fi Direct•Other connections: Antenna IEC75, Digital audio out (optical), Audio L/R in, Audio in (DVI), Headphone out, Service connector, Ethernet-LAN RJ-45•HDMI features:Audio Return Channel •EasyLink (HDMI-CEC): Remote control pass-through, System audio control, System standby, Pixel Plus link (Philips)*, One touch play Multimedia Applications•Video Playback Formats: Containers: AVI, MKV,H264/MPEG-4 AVC, MPEG-1, MPEG-2, MPEG-4,WMV9/VC1, HEVC (H.265)•Subtitles Formats Support: .SMI, .SRT, .SUB, .TXT,.AAS•Music Playback Formats: AAC, MP3, WAV, WMA(v2 up to v9.2), WMA-PRO (v9 and v10)•Picture Playback Formats: JPEG, BMP, GIF, PNGSupported Display Resolution•Computer inputs on HDMI1/2: up to FHD1920x1080 @60Hz, up to 4K UHD3840x2160 @30Hz•Computer inputs on HDMI3/4: up to 4K UHD3840x2160 @60Hz•Video inputs on HDMI1/2: up to 4K UHD3840x2160 @30Hz, up to FHD1920x1080 @ 60Hz•Video inputs on HDMI3/4: up to 4K UHD3840x2160 @60HzTuner/Reception/Transmission•Digital TV: DVB-T/T2•MPEG Support: MPEG2, MPEG4•Video Playback: NTSC, PAL, SECAM•TV Program guide*: 8 day Electronic ProgramGuide•Signal strength indication•Teletext: 1000 page Hypertext•HEVC supportPower•Mains power: AC 110-240V +/-•Ambient temperature: 5 °C to 35 °C•Standby power consumption: <0.5W•Power Saving Features: Auto switch-off timer,Picture mute (for radio)Dimensions•Box dimensions(W x H x D):1343 x 828 x 168 mm•Set dimensions(W x H x D):1239.20 x 714.04 x 90.26 mm•Set dimensions with stand (W x H x D):1239.20 x 780.32 x 259.06 mm•Product weight: 15.3 kg•Product weight (+stand): 15.6 kg•Weight incl. Packaging: 21.5 kg•VESA wall mount compatible: 400 x 200 mmAccessories•Included accessories: Remote Control, Powercord, Quick start guide, Legal and safety brochure,Table top stand, 2 x AAA Batteries*EPG and actual visibility (up to 8 days) is country and operatordependent.*Energy consumption in kWh per year, based on the powerconsumption of the television operating 4 hours per day for 365days. The actual energy consumption will depend on how thetelevision is used.*The TV supports DVB reception for 'Free to air' broadcast. SpecificDVB operators may not be supported. An up to date list can befound in the FAQ section of the Philips support website. For someoperators Conditional Access and subscripction are required.Contact your operator for more information.*(Philips) only compatible with specific Philips player device.*Philips TV Remote app and related functionalities vary per TV model,operator, and country, as well as smart device model and OS. Formore details please visit: /TVRemoteapp.*Smart TV app offerings vary per TV model and country. For moredetails please visit: /smarttv.*USB recording for digital channels only, recordings may be limited bybroadcast copy protection (CI+). Country and channel restrictionsmay apply.*Compatibility depends on Wifi Miracast certification & Android 4.2or later. For more details please refer to your device documentation.。

华为155/622光端机的板件介绍和告警等2014年3月9号编辑:沈文明板件有:IU1:光接口板位,可以安插OI2S/OI2D/OI4/SB2等IU2,IU3:光/电接口板位,可以安插OI2S/OI2D/OI4/SB2,SP1/SP2/SM1/HP2/PL3等IU3:环境监控,可以安插EMUIU4:电接口板位,可以安插PD2T/PM2/TDA/ET1/AIU等SCB:系统控制板位,可以安插A:防尘网,电源滤波板,可以安插B:风扇板位,FAN123左边)板:SB2L4右边)板:SB2R5SB2D6、1路STM-4光接口板:OI4例如:155的就有:OI2S是单光口板件OI2D就是双光口板件655的就有:OI4S是单光口板件OI4D就是双光口板件光接口版位都插IU1,IU2,IU3.其中如果用单光口板件时优先插在IU1,IU2上2M电接口版件SP1可插在IU1,IU2,IU3上。

2M电接口版件PD2可插在IU4上交叉板叫X42可插在SCB上。

时钟板叫STG可插在SCB上。

主控板叫SCC可插在SCB上。

开销板叫OHP可插在SCB上。

OI2功能光接口板件1.光/电及电/光转换功能。

2.所有再生段、复用段开销字节的处理,此外还完成再生段、复用段和高阶通道的告警处理和维护功能。

②SDH板发送故障;③SDH板接收模块。

→检测方法:自环法、光功率测试法。

线路板上的告警:S16、SL4、SD4、SQ1、SL1、SQE、SE2的板件等1.R-LOS告警:接收端数据信号丢失。

检测的是电信号,不是光信号。

2.R-LOF告警:在接收端检测到定帧字节A1≠f6H、A2≠28H,说明接收端帧同步丢失。

B2误码过量。

检测到B2误码个数超过规定值。

4.MS-REI告警:线路板所连的对端站检测到有B2误码,向本站传回M1字节。

5.MS-AIS告警:检测接收到的复用段开销字节K2(bit6,7,8)=111时,上报此告警。

告警含义是整个STM-N帧内除RSOH外全部为“1”。

VS-622DT Quick Start (P/N: 2900-301025QS REV 3)P/N:Scan for full manualVS-622DT Quick Start GuideThis guide helps you install and use your VS-622DT for the first time.Go to /downloads/VS-622DT to download the latest user manual and check if firmware upgrades are available.Step 1: Check w hat’s in the boxVS-622DT6x2 HDMI / HDBT Audio Matrix Switcher 1 Quick start guide1 Set of rack ears1 Power cord4 Rubber feetStep 2: Get to know your VS-622DTStep 3: Install VS-622DTInstall VS-622DT using one of the following methods:•Remove the three screws from each side of the unit, reinsert those screws through therack ears and mount on a 19" rack.•Attach the rubber feet and place the unit on a flat surface.Step 4: Connect the inputs and outputsAlways switch OFF the power on each device before connecting it to your VS-622DT. For best results, we recommend that you always use Kramer high-performance cables to connect AV equipment to the VS-622DT.RJ-45 Pinout:Audio output pinout:For the Ethernet connector, see the wiring diagram below:To a balanced stereo audio acceptor:To an unbalanced stereo audio acceptor:PIN EIA /TIA 568B PIN Wire Color 1 Orange / White 2 Orange 3 Green / White 4Blue5 Blue / White6 Green 7Brown / White8BrownFor optimum range and performance use the recommended Kramer cables available at /product/VS-622DT . DIP-switch setupA switch that is down is on; a switch that is up is off. By default, all the switches are up (off). #FeatureDescription1 HDCP support on inputs On (down)—Disable HDCP support on all inputs.Off (up)—Enable HDCP support which is defined by P3000 commands. 2 Video mode switching Output 1On (down)—Auto. Off (up)—Manual.3Last connected/Priority mode Output 1When DIP-switch 2 is set to Auto (ON): On (down)—Enable Last Connected mode.Off (up)—Enable Priority mode where the priority of each input is defined by the input number, (1 is the highest priority). 4 Video mode switching Output 2On (down)—Auto. Off —Manual.5Last connected/Priority mode Output 2When DIP-switch 4 is set to Auto (ON): On (down)—Enable Last-connected mode.Off (up)—Enable Priority mode where the priority of each input is defined by the input number, (1 is the highest priority). 6 N/AN/A7Range mode for HDBT IN 1 On (down) – HDBaseT Ultra-long range (provides increased range at a reduced bandwidth). Off (up) – Normal range (default).8Range mode for HDBT IN 2On (down) – HDBaseT Ultra-long range (provides increased range at a reduced bandwidth). Off (up) – Normal range (default).Step 5: Connect the powerConnect the power cord to VS-622DT and plug it into the mains electricity.Safety InstructionsCaution: There are no operator serviceable parts inside the unit. Warning: Use only the power cord that is supplied with the unit.Warning: Do not open the unit. High voltages can cause electrical shock! Servicing by qualified personnel only. Warning: Disconnect the power and unplug the unit from the wall before installing. See for updated safety information.Step 6: Operate the VS-622DTWeb pages: .1 RS-232 and Ethernet:Technical Specifications。