P4C187-35CC中文资料

- 格式:pdf

- 大小:321.09 KB

- 文档页数:12

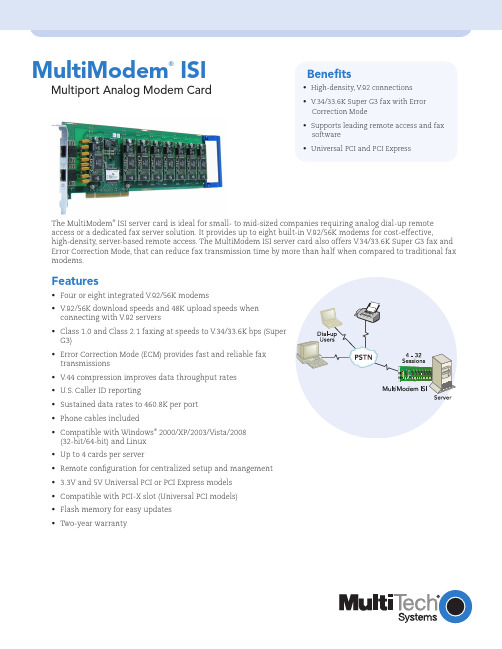

Multiport Analog Modem CardBenefits• High-density , V .92 connections • V .34/33.6K Super G3 fax with Error Correction Mode • Supports leading remote access and fax software • Universal PCI and PCI ExpressThe MultiModem ® ISI server card is ideal for small- to mid-sized companies requiring analog dial-up remote access or a dedicated fax server solution. It provides up to eight built-in V .92/56K modems for cost-effective,high-density , server-based remote access. The MultiModem ISI server card also offers V .34/33.6K Super G3 fax and Error Correction Mode, that can reduce fax transmission time by more than half when compared to traditional fax modems.Features• Four or eight integrated V .92/56K modems• V .92/56K download speeds and 48K upload speeds when connecting with V .92 servers • Class 1.0 and Class 2.1 faxing at speeds to V .34/33.6K bps (Super G3)• Error Correction Mode (ECM) provides fast and reliable fax transmissions • V .44 compression improves data throughput rates • U.S. Caller ID reporting• Sustained data rates to 460.8K per port • Phone cables included• Compatible with Windows ® 2000/XP/2003/Vista/2008 (32-bit/64-bit) and Linux • Up to 4 cards per server• Remote configuration for centralized setup and mangement • 3.3V and 5V Universal PCI or PCI Express models • Compatible with PCI-X slot (Universal PCI models)• Flash memory for easy updates • T wo-year warrantyMultiModem ®ISIWorld Headquarters Tel: (763) 785-3500 (800) EMEA Headquarters Multi-Tech Systems (EMEA)United KingdomTel: +(44) 118-959 7774Multi-Tech Systems (EMEA) FranceTel: +(33) 1 49 19 22 06HighlightsCost-Effective & Scalable. The MultiModem ISI server card provides four or eight dial-up sessions using only one server slot. When demand exceeds one modem card, you can simply add up to three additional cards.V.92 Dial-out Connections. The MultiModem ISI server card supports V .92/56K dial-out and V .34/33.6K dial-inconnections. With V .92 dial-out, you can achieve an upload speed of 48K bps (30% increase over V .90 modems).Enhanced Fax Features. The MultiModem ISI server card supports V .34 fax and Error Correction Mode providingsignificant performance and reliability enhancements over previous fax standards. V .34 sends and receives faxes at speeds up to 33.6K, more than double the speed of the V .17/14.4K fax standard. Error Correction Mode adds reliablility while increasing performance of faxtransmissions. Together these enhancements increase the performance of the MultiModem ISI server card to levels previously only found in more expensive dedicated fax boards and machines.V.44 Compression. V .44 compression standard improves V .42bis data compression anywhere from 20 to 60%, up to as much as 200% for certain types of highly compressible data. This compression technique enables data throughput rates of higher than 300K bps.Simplify Remote Access. The fully-integrated MultiModem ISI server card is easy to set up and manage. You only have to connect the phone lines. There are no external modems and power cords to hassle with; plus it saves back office space since the modems are on the prehensive Service and Support. The Multi-Techcommitment to service means we provide a two-year product warranty and service that includes free telephone technical support, 24-hour web site and ftp support.Ordering InformationProductDescriptionRegion ISI5634UPCI/8 V .92, 8-Modem Card - Universal PCI Global ISI5634UPCI/4 V .92, 4-Modem Card - Universal PCI Global ISI9234PCIE/8 V .92, 8-Modem Card - PCI Express Global ISI9234PCIE/4V .92, 4-Modem Card - PCI ExpressGlobalSpecificationsModemData: V .92, V .90, enhanced V .34, V .32bis, V .22bis Error Correction: V .42, MNP Class 3 & 4Data Compression: V .44, V .42bis, MNP Class 5FaxStandards: V .34, V .17, V .29, V .27ter, V .21, T.30, T.30Annex A, T.30 Annex F , T.31, T.31 Annex B, T.32 Annex C, TR29.2 Class 2 RecommendationRates: 33.6K, 31.2K, 28.8K, 26.4K, 24K, 21.6K, 19.2K, 16.8K, 14.4K, 12K, 9600, 7200, 4800, 2400, 300 bps Error Correction: ECMCompression: MH (T.4), MR (T.4), & MMR (T.6)Conversion: Real time (on-the-fly) compression conversionCommands: Class 1, 2, 1.0, 2.0, 2.1Bus Type3.3V & 5V Universal PCI or PCI Express (x1)Operating System SupportWindows 2000/XP/2003/Vista/2008 (32-bit/64-bit) & LinuxCablingFan out cable with 1 or 2 RJ45 connectors & 4 or 8 RJ11 connectorsPhysical DescriptionUniversal PCI Models:13.87" L × 4.97" W; 8.7 oz (35.2 cm × 12.6 cm; 247 g)PCI Express Models:13.87" L × 4.97" W; 8.5 oz (35.2 cm × 12.6 cm; 241 g)Operating EnvironmentTemperature Range: +23° to +140° F (-5° to +60° C)ApprovalsCE MarkEMC: FCC Part 15 Class B, EN 55022, EN 55024Safety: UL/cUL 60950-1, EN 60950-1, AS/NZS 60950:2000, CCCTelecom: 47CFR Part 68, CS03, TBR21Other countries also includedCopyright © 2008 by Multi-Tech Systems, Inc. All rights reserved.6/08 86000323Made in Mounds View, MN, U.S.A.Features and specifications are subject to change without notice.Trademarks / Registered Trademarks: MultiModem, Multi-Tech, and theMulti-Tech logo: Multi-Tech Systems, Inc. / All other products and technologies are the trademarks or registered trademarks of their respective holders.。

AccessoriesAC line cable (2.4m long) ······························································································1High voltage output cable (1.5m long) terminated with SHV-P plugs E1168-19 ···········1Spare fuses ···················································································································2Subject to local technical requirements and regulations, availability of products included in this promotional material may vary. Please consult with our sales rmation furnished by HAMAMATSU is believed to be reliable. However, no responsibility is assumed for possible inaccuracies or omissions. Specifications are subject to change without notice No patent right are granted to any of the circuits described herein. © 1998 Hamamatsu Photonics K.K.±3kV Output Regulated DC Power SupplyFor Photomultiplier Tube, Proportional Counter Tube, etc.Hamamatsu C3350 is a highly regulated bench-top power supply with ±3kV, 10mA output. The LED panel meter on the front panel allows easy andprecise voltage monitoring. It is especially suited for laboratory uses including photomultiplier and proportional counter tube operations.TACCF0075SpecificationsNOTEAt maximum output voltage and current.At maximum output voltage.Without moisture condensation.±3kV REGULATED HIGH VOLTAGE POWER SUPPLY C3350HAMAMATSU PHOTONICS K.K., Electoron Tube Center314-5, Shimokanzo, Toyooka-village, Iwata-gun, Shizuoka-ken, 438-0193, Japan, Telephone: (81)539/62-5248, Fax: (81)539/62-2205U.S.A.: Hamamatsu Corporation: 360 Foothill Road, Bridgewater. N.J. 08807-0910, U.S.A., Telephone: (1)908-231-0960, Fax: (1)908-231-1218Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49)8152-375-0, Fax: (49)8152-2658France: Hamamatsu Photonics France S.A.R.L.: 8, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: (33)1 69 53 71 00, Fax: (33)1 69 53 71 10United Kingdom: Hamamatsu Photonics UK Limted: Lough Point, 2 Gladbeck Way, Windmill Hill, Enfield, Middlesex EN2 7JA, United Kingdom, Telephone: (44)181-367-3560, Fax: (44)181-367-6384North Europe: Hamamatsu Photonics Norden AB: Färögatan 7, S-164-40 Kista Sweden, Telephone: (46)8-703-29-50, Fax: (46)8-750-58-95Italy: Hamamatsu Photonics Italia: S.R.L.: Via Della Moia, 1/E, 20020 Arese, (Milano), Italy, Telephone: (39)2-935 81 733, Fax: (39)2-935 81 741TACC1017E01JUN. 1998 SYDimensional Outline (Unit : mm)TACCA0126EA。

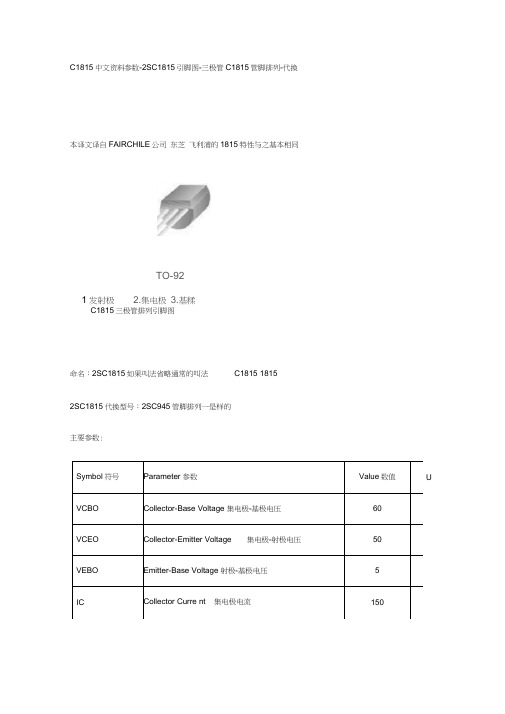

C1815中文资料参数-2SC1815引脚图-三极管C1815管脚排列-代换本译文译自FAIRCHILE 公司 东芝 飞利浦的1815特性与之基本相同C1815三极管排列引脚图命名:2SC1815如果叫法省略通常的叫法 C1815 18152SC1815代换型号:2SC945管脚排列一是样的Symbol符号 Parameter 参数 Value 数值VCBO Collector-Base Voltage 集电极-基极电压 60VCEO Collector-Emitter Voltage 集电极-射极电压 50VEBO Emitter-Base Voltage 射极-基极电压 5IC Collector Curre nt 集电极电流 150主要参数:U1发射极 TO-922.集电极3.基糅C1815特性曲线:V CE[V]. COLLECTOR-EMITTER VOLTAGE静态特性曲线V e 4Vl ? BASE-EMITTER VOLTAGE传输特性曲线J-J1Q.1 0.00.6 0 8IO1 2101 10 100o4—N -v o lN UJ M H n o a c J 也woo直流电流增益曲线基极-发射饱和电压曲线 集电极-射极饱和电压曲线[c [mAl. COLLECTOR CURRENT山0<n o > N O _L <cr r u 吒 -f J100f=1MHzI E二01 10 100 1000V CB FVI COLLECTOR-BASEVOLTAGE输出电容曲线00100.-1电流增益带宽曲线0 46 10 10J---------- 「■'/,,.\ 1M p I\ (R2.29)o 百g --—14-58 U JBTO-921 27TYP [1.27 ±J 20] 1.27TYP[1.27±£].231(K3E+C.-C-3上E。

1NOVEMBER 1997 - REVISED MARCH 1999Copyright © 1999, Power Innovations Limited, UKInformation is current as of publication date. Products conform to specifications in accordance with the terms of Power Innovations standard warranty. Production processing does notnecessarily include testing of all parameters.TELECOMMUNICATION SYSTEM 100A 10/1000 OVERVOLTAGE PROTECTORSq 8kV 10/700, 200A 5/310 ITU-T K20/21 rating qIon-Implanted Breakdown Region Precise and Stable VoltageLow Voltage Overshoot under Surgeq Rated for International Surge Wave Shapesq Low Differential Capacitance . . . 67pF max.qUL Recognized, E132482DEVICE V DRM V V (BO)V ‘40705870‘40806580‘40957595‘4125100125‘4145120145‘4165135165‘4180145180‘4200155200‘4240180240‘4265200265‘4300230300‘4350275350‘4400300400WAVE SHAPESTANDARD I TSP A 2/10µs GR-1089-CORE5008/20µs IEC 61000-4-530010/160µs FCC Part 6825010/700µs ITU-T K20/2120010/560µs FCC Part 6816010/1000µsGR-1089-CORE100descriptionThese devices are designed to limit overvoltages on the telephone line. Overvoltages are normally caused by a.c. power system or lightning flash disturbances which are induced or conducted on to the telephone line. A single device provides 2-point protection and is typically used for the protection of 2-wire telecommunication equipment (e.g. between the Ring and Tip wires for telephones and modems). Combinations of devices can be used for multi-point protection (e.g. 3-point protection between Ring, Tip and Ground).The protector consists of a symmetrical voltage-triggered bidirectional thyristor. Overvoltages are initially clipped by breakdown clamping until the voltage rises to the breakover level, which causes the device to crowbar into a low-voltage on state. This low-voltage on state causes the current resulting from the overvoltage to be safely diverted through the device. The high crowbar holding current prevents d.c. latchup as the diverted current subsides.2NOVEMBER 1997 - REVISED MARCH 1999This TISP4xxxH3BJ range consists of thirteen voltage variants to meet various maximum system voltage levels (58V to 275V). They are guaranteed to voltage limit and withstand the listed international lightning surges in both polarities. These high (H) current protection devices are in a plastic package SMBJ (JEDEC DO-214AA with J-bend leads) and supplied in embossed carrier reel pack. For alternative voltage and holding current values, consult the factory. For lower rated impulse currents in the SMB package, the 50A 10/1000TISP4xxxM3BJ series is available.absolute maximum ratings, T A = 25°C (unless otherwise noted)RATINGSYMBOLVALUE UNITRepetitive peak off-state voltage, (see Note 1)‘4070‘4080‘4095‘4125‘4145‘4165‘4180‘4200‘4240‘4265‘4300‘4350‘4400V DRM ± 58± 65± 75±100±120±135±145±155±180±200±230±275±300V Non-repetitive peak on-state pulse current (see Notes 2, 3 and 4)I TSPA2/10µs (GR-1089-CORE, 2/10µs voltage wave shape)5008/20µs (IEC 61000-4-5, 1.2/50µs voltage, 8/20 current combination wave generator)30010/160µs (FCC Part 68, 10/160µs voltage wave shape)2505/200µs (VDE 0433, 10/700µs voltage wave shape)2200.2/310µs (I3124, 0.5/700µs voltage wave shape)2005/310µs (ITU-T K20/21, 10/700µs voltage wave shape)2005/310µs (FTZ R12, 10/700µs voltage wave shape)20010/560µs (FCC Part 68, 10/560µs voltage wave shape)16010/1000µs (GR-1089-CORE, 10/1000µs voltage wave shape)100Non-repetitive peak on-state current (see Notes 2, 3 and 5)I TSM55602.1A20ms (50Hz) full sine wave 16.7ms (60Hz) full sine wave 1000s 50Hz/60Hz a.c.Initial rate of rise of on-state current,Exponential current ramp, Maximum ramp value <200 Adi T /dt 400A/µs Junction temperature T J -40 to +150°C Storage temperature range T stg -65 to +150°C NOTES:1.See Applications Information and Figure 10 for voltage values at lower temperatures.2.Initially the TISP4xxxH3BJ must be in thermal equilibrium with T J =25°C.3.The surge may be repeated after the TISP4xxxH3BJ returns to its initial conditions.4.See Applications Information and Figure 11 for current ratings at other temperatures.5.EIA/JESD51-2 environment and EIA/JESD51-3 PCB with standard footprint dimensions connected with 5A rated printed wiring track widths. See Figure 8 for the current ratings at other durations. Derate current values at -0.61%/°C for ambient temperatures above 25°C3NOVEMBER 1997 - REVISED MARCH 1999electrical characteristics for the T and R terminals, T A = 25°C (unless otherwise noted)P ARAMETERTEST CONDITIONSMINTYPMAX UNIT I DRMRepetitive peak off-state currentV D = V DRMT A = 25°C T A = 85°C±5±10µAV (BO)Breakover voltagedv/dt =±750V/ms,R SOURCE =300Ω‘4070‘4080‘4095‘4125‘4145‘4165‘4180‘4200‘4240‘4265‘4300‘4350‘4400±70±80±95±125±145±165±180±200±240±265±300±350±400V V (BO)Impulse breakover voltagedv/dt ≤±1000V/µs, Linear voltage ramp,Maximum ramp value =±500V di/dt =±20A/µs, Linear current ramp, Maximum ramp value =±10A‘4070‘4080‘4095‘4125‘4145‘4165‘4180‘4200‘4240‘4265‘4300‘4350‘4400±78±88±103±134±154±174±189±210±250±276±311±362±413V I (BO)Breakover current dv/dt =±750V/ms,R SOURCE =300Ω±0.15±0.6A V T On-state voltage I T =±5A,t W =100µs ±3V I H Holding current I T =±5A, di/dt =+/-30mA/ms±0.15±0.6A dv/dt Critical rate of rise of off-state voltage Linear voltage ramp, Maximum ramp value <0.85V DRM ±5kV/µs I DOff-state currentV D =±50V T A = 85°C±10µA C offOff-state capacitancef =100kHz,V d =1V rms,V D =0,f =100kHz,V d =1V rms,V D =-1Vf =100kHz,V d =1V rms,V D =-2Vf =100kHz,V d =1V rms,V D =-50Vf =100kHz,V d =1V rms,V D =-100V(see Note 6)‘4070 thru ‘4095‘4125 thru ‘4200‘4240 thru ‘4400‘4070 thru ‘4095‘4125 thru ‘4200‘4240 thru ‘4400‘4070 thru ‘4095‘4125 thru ‘4200‘4240 thru ‘4400‘4070 thru ‘4095‘4125 thru ‘4200‘4240 thru ‘4400‘4125 thru ‘4200‘4240 thru ‘440014580701307160120655562302428221709084150796714074627335283326pFNOTE6:T o avoid possible voltage clipping, the ‘4125 is tested with V D =-98V .4NOVEMBER 1997 - REVISED MARCH 1999thermal characteristicsPARAMETERTEST CONDITIONSMINTYPMAX UNITR θJAJunction to free air thermal resistanceEIA/JESD51-3 PCB, I T = I TSM(1000),T A = 25°C, (see Note 7)113°C/W 265mm x 210mm populated line card, 4-layer PCB, I T = I TSM(1000), T A = 25°C50NOTE7: EIA/JESD51-2 environment and PCB has standard footprint dimensions connected with 5A rated printed wiring track widths.PARAMETER MEASUREMENT INFORMATIONFigure 1. VOLTAGE-CURRENT CHARACTERISTIC FOR T AND R TERMINALSALL MEASUREMENTS ARE REFERENCED TO THE R TERMINAL-vV DRM I DRMV D I HI T V TI TSMI TSPV (BO)I (BO)I DQuadrant ISwitching Characteristic+v+i V (BO)I (BO)V DI DI HI TV TI TSMI TSP-iQuadrant IIISwitching CharacteristicPMXXAABV DRMI DRM56NOVEMBER 1997 - REVISED MARCH 1999 RATING AND THERMAL INFORMATION78NOVEMBER 1997 - REVISED MARCH 1999APPLICATIONS INFORMATIONdeploymentThese devices are two terminal overvoltage protectors. They may be used either singly to limit the voltage between two conductors (Figure 12) or in multiples to limit the voltage at several points in a circuit (Figure 13).In Figure 12, protector Th1 limits the maximum voltage between the two conductors to ±V (BO). This configuration is normally used to protect circuits without a ground reference, such as modems. In Figure 13,protectors Th2 and Th3 limit the maximum voltage between each conductor and ground to the ±V (BO) of the individual protector. Protector Th1 limits the maximum voltage between the two conductors to its ±V (BO)value. If the equipment being protected has all its vulnerable components connected between the conductors and ground, then protector Th1 is not required.impulse testingT o verify the withstand capability and safety of the equipment, standards require that the equipment is tested with various impulse wave forms. The table below shows some common values.If the impulse generator current exceeds the protectors current rating then a series resistance can be used to reduce the current to the protectors rated value and so prevent possible failure. The required value of series resistance for a given waveform is given by the following calculations. First, the minimum total circuit impedance is found by dividing the impulse generators peak voltage by the protectors rated current. The impulse generators fictive impedance (generators peak voltage divided by peak short circuit current) is then subtracted from the minimum total circuit impedance to give the required value of series resistance. In some cases the equipment will require verification over a temperature range. By using the rated waveform values from Figure 11, the appropriate series resistor value can be calculated for ambient temperatures in the range of -40°C to 85°C.Figure 12. TWO POINT PROTECTION Figure 13. MULTI-POINT PROTECTIONSTANDARDPEAK VOLTAGESETTINGVVOLTAGE WAVE FORMµs PEAK CURRENTVALUE A CURRENT WAVE FORMµs TISP4xxxH325°C RATINGA SERIES RESISTANCEΩGR-1089-CORE25002/105002/105000100010/100010010/1000100FCC Part 68(March 1998)150010/16020010/160250080010/56010010/560160015009/720†37.55/320†200010009/720†255/320†2000I312415000.5/70037.50.2/3102000ITU-T K20/K211500400010/70037.51005/310200† FCC Part 68 terminology for the waveforms produced by the ITU-T recommendation K21 10/700 impulse generatorTh1Th3Th2Th19NOVEMBER 1997 - REVISED MARCH 1999a.c. power testingThe protector can withstand currents applied for times not exceeding those shown in Figure 8. Currents that exceed these times must be terminated or reduced to avoid protector failure. Fuses, PTC (Positive T emperature Coefficient) resistors and fusible resistors are overcurrent protection devices which can be used to reduce the current flow. Protective fuses may range from a few hundred milliamperes to one ampere. In some cases it may be necessary to add some extra series resistance to prevent the fuse opening during impulse testing. The current versus time characteristic of the overcurrent protector must be below the line shown in Figure 8. In some cases there may be a further time limit imposed by the test standard (e.g. UL 1459 wiring simulator failure).capacitanceThe protector characteristic off-state capacitance values are given for d.c. bias voltage, V D , values of 0, -1V , -2V and -50V . Where possible values are also given for -100V . Values for other voltages may be calculated by multiplying the V D =0 capacitance value by the factor given in Figure 6. Up to 10MHz the capacitance is essentially independent of frequency. Above 10MHz the effective capacitance is strongly dependent on connection inductance. In many applications, such as Figure 15 and Figure 17, the typical conductor bias voltages will be about -2V and -50V . Figure 7 shows the differential (line unbalance) capacitance caused by biasing one protector at -2V and the other at -50V .normal system voltage levelsThe protector should not clip or limit the voltages that occur in normal system operation. For unusual conditions, such as ringing without the line connected, some degree of clipping is permissible. Under this condition about 10V of clipping is normally possible without activating the ring trip circuit.Figure 10 allows the calculation of the protector V DRM value at temperatures below 25°C. The calculated value should not be less than the maximum normal system voltages. The TISP4265H3BJ, with a V DRM of 200V , can be used for the protection of ring generators producing 100V rms of ring on a battery voltage of -58V (Th2 and Th3 in Figure 17). The peak ring voltage will be 58+1.414*100 = 199.4V . However, this is the open circuit voltage and the connection of the line and its equipment will reduce the peak voltage. In the extreme case of an unconnected line, clipping the peak voltage to 190V should not activate the ring trip. This level of clipping would occur at the temperature when the V DRM has reduced to 190/200 = 0.95 of its 25°C value. Figure 10 shows that this condition will occur at an ambient temperature of -22°C. In this example, the TISP4265H3BJ will allow normal equipment operation provided that the minimum expected ambient temperature does not fall below -22°C.JESD51 thermal measurement methodT o standardise thermal measurements, the EIA (Electronic Industries Alliance) has created the JESD51standard. Part 2 of the standard (JESD51-2, 1995) describes the test environment. This is a 0.0283m 3 (1ft 3)cube which contains the test PCB (Printed Circuit Board) horizontally mounted at the centre. Part 3 of the standard (JESD51-3, 1996) defines two test PCBs for surface mount components; one for packages smaller than 27mm on a side and the other for packages up to 48mm. The SMBJ measurements used the smaller 76.2mm x 114.3mm (3.0“x 4.5“) PCB. The JESD51-3 PCBs are designed to have low effective thermal conductivity (high thermal resistance) and represent a worse case condition. The PCBs used in the majority of applications will achieve lower values of thermal resistance and so can dissipate higher power levels than indicated by the JESD51 values.10NOVEMBER 1997 - REVISED MARCH 1999typical circuitsFigure 14. MODEM INTER-WIRE PROTECTION Figure 15. PROTECTION MODULEFigure 16. ISDN PROTECTIONFigure 17. LINE CARD RING/TEST PROTECTIONFUSETISP4350AI6XBMA RING DETECTOR HOOK SWITCHD.C. SINK SIGNALMODEMRINGTIPR1aR1bRING WIRETIP WIRETh3Th2Th1PROTECTED EQUIPMENT E.G. LINE CARDAI6XBKR1aR1bTh3Th2Th1AI6XBLSIGNALD.C.MECHANICAL DATASMBJ (DO-214AA)plastic surface mount diode packageThis surface mount package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.MECHANICAL DATAdevice symbolization codeDevices will be coded as below. As the device parameters are symmetrical, terminal 1 is not identified.carrier informationDevices are shipped in one of the carriers below. Unless a specific method of shipment is specified by the customer, devices will be shipped in the most practical carrier. For production quantities the carrier will be embossed tape reel pack. Evaluation quantities may be shipped in bulk pack or embossed tape.DEVICE SYMOBLIZATIONCODE TISP4070H3BJ 4070H3TISP4080H3BJ 4080H3TISP4095H3BJ 4095H3TISP4125H3BJ 4125H3TISP4145H3BJ 4145H3TISP4165H3BJ 4165H3TISP4180H3BJ 4180H3TISP4200H3BJ 4200H3TISP4240H3BJ 4240H3TISP4265H3BJ 4265H3TISP4300H3BJ 4300H3TISP4350H3BJ 4350H3TISP4400H3BJ4400H3CARRIERORDER #Embossed T ape Reel PackTISP4xxxH3BJR Bulk PackTISP4xxxH3BJMECHANICAL DATAIMPORTANT NOTICEPower Innovations Limited (PI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to verify, before placing orders, that the information being relied on is current.PI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with PI's standard warranty. T esting and other quality control techniques are utilized to the extent PI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.PI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor is any license, either express or implied, granted under any patent right, copyright, design right, or other intellectual property right of PI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.PI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORISED, OR WARRANTED TO BE SUIT ABLE FOR USE IN LIFE-SUPPORT APPLICA TIONS, DEVICES OR SYSTEMS.Copyright © 1999, Power Innovations Limited。

proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes couldDIFFERENTIAL PHASEFigure 3. Multiburst (CCIR 18) Test Pattern (PAL) Figure 4. Multipulse Test Pattern (PAL)Figure 5. CCIR 17 Test Pattern (PAL)Gain errors most commonly appear as attenuation or peaking of the chrominance information. This shows up in the picture as incorrect color saturation. Delay distortion will cause color smearing or bleeding, particularly at the edges of objects in the picture. It may also cause poor reproduction of sharp luminence transitions.All waveforms in Figure 3 through Figure 5 were taken using the sag correction feature of OPA360. Figure 3 through Figure 5 show that the OPA360 causes no visible distortion or change in gain throughout the entire video frequency range.INTERNAL LEVEL SHIFTMany common video DACs embedded in digital media processors like TI’s TMS320DM270 and the new OMAP2420 processors operate on a single supply (no negative supply). Typically, the lowest point of the sync pulse output by these Video DACs corresponds to 0V. With a 0V input, the output of common single-supply op amps saturates at a voltage > 0V. This effect would clip the tip of the sync pulse and therefore degrade the video signal integity. The OPA360 employs an internal level shift circuit to avoid clipping. The input signal is typically shifted byFigure 6. Internal Level Shifter, Shifts Input Signal by Approximately 60mV to Prevent SyncTip ClippingThe level shift function is particularly useful when the output of the OPA360 is DC-coupled to the video load. However, it is also helpful when sag correction is employed. The offset helps to shift the video signal closer to the positive rail, so that with even a small 33µF coupling capacitor, the output is well outside the saturation limits of the OPA360. Figure 7 shows the output swing of the OPA360, operated on 3.0V supplies, with a 22µF sag correction capacitor and a 33µF output coupling capacitor. The test signal is a 50Hz signal constructed to generate a 1/2 black, 1/2 white screen. This video pattern is one of the most difficult patterns to display because it is the worst case signal regarding signal swing. A worst case signal such as this is highly unlikely in normal operation. Any other signal has a lower swing range. Note in Figure 7 that neither the white nor the black portion of the video signal is clipped.Figure 7. Output Swing with 33m F on 3V Supply OUTPUT SWING TO GND (SYNC PULSE)Figure 8 shows the true output swing capability of the OPA360 by taking the tip of the input sync pulse to a slightly negative voltage. Even when the output sync tip is at 8mV, the output shows no clipping of the sync pulse.Figure 8. Input Sync Tip at −30mV (Output ShowsNo Sign of Clipping)Figure 10. Standard Video Circuit with 220m F Capacitor (top trace) vs OPA360 with 22m F and47m F CapacitorsA field tilt equivalent to that achieved using the standard 220µF coupling capacitor can be achieved with a 22µF/67µF combination − see Figure 11. These capacitor values are optimized—sag correction capacitors larger than 22µF do not provide significant improvement. Smaller sag correction capacitors will lead to higher tilt.Figure 11. 220m F Standard Video Circuit (top trace) vs OPA360 with 22m F/67m FFigure 12. Output Swing with 47m F on 3V Supply Figure 13. Output Swing with 67m F on 3V SupplyC OUT 47µF R OUT 75ΩGND75Ω++OUT2−Pole Filter(1)SAGC SAG 22µF AC Gain =2DC Gain =2.8Television or VCROPA360Video DACNOTE:(1)Optional 200Ωfor use with TI’s Digital Media Processors.Level ShifterV+V+=2.7V to 3.3VFigure 14. DC-Coupled Input/AC-Coupled OutputFigure 16. DC-Coupled OutputPACKAGING INFORMATIONORDERABLE DEVICE STATUS(1)PACKAGE TYPEPACKAGE DRAWINGPINS PACKAGE QTYOPA360AIDCKR ACTIVE SOP DCK 63000OPA360AIDCKTACTIVESOPDCK6250(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,butTI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.PACKAGE OPTION ADDENDUM20-Jul-2004元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2004, Texas Instruments Incorporated。

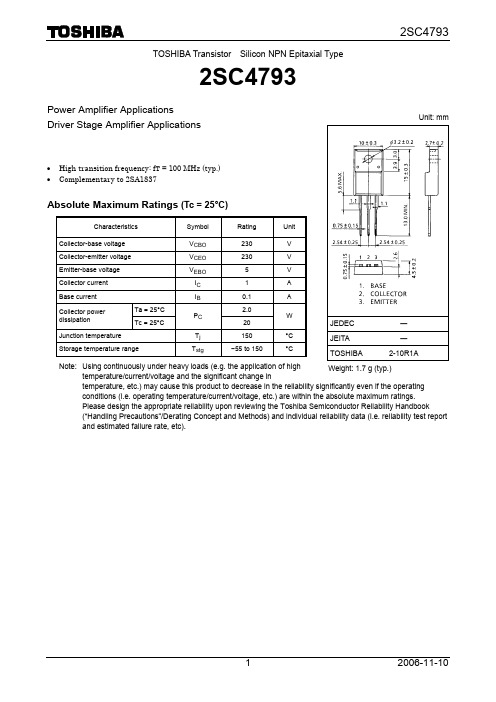

TOSHIBA Transistor Silicon NPN Epitaxial Type2SC4793Power Amplifier ApplicationsDriver Stage Amplifier Applications• High transition frequency: f T = 100 MHz (typ.) • Complementary to 2SA1837Absolute Maximum Ratings (Tc = 25°C)Characteristics Symbol Rating UnitCollector-base voltage V CBO 230 V Collector-emitter voltage V CEO 230 V Emitter-base voltage V EBO 5 V Collector current I C 1 A Base current I B 0.1 A Ta = 25°C 2.0 Collector powerdissipationTc = 25°CP C20WJunction temperature T j 150 °C Storage temperature rangeT stg−55 to 150°CNote: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change intemperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings. Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook(“Handling Precautions”/Derating Concept and Methods) and individual reliability data (i.e. reliability test report and estimated failure rate, etc).Unit: mmJEDEC― JEITA ―TOSHIBA 2-10R1AWeight: 1.7 g (typ.)Electrical Characteristics (Tc = 25°C)Typ.Max UnitCondition Min Characteristics Symbol TestCollector cut-off current I CBO V CB = 230 V, I E = 0 ―― 1.0 μA Emitter cut-off current I EBO V EB = 5 V, I C = 0 ―― 1.0 μA Collector-emitter breakdown voltage V (BR) CEO I C = 10 mA, I B = 0 230 ―― V DC current gain h FE V CE = 5 V, I C = 100 mA 100 ― 320Collector-emitter saturation voltage V CE (sat)I C = 500 mA, I B = 50 mA ―― 1.5 V Base-emitter voltage V BE V CE = 5 V, I C = 500 mA ―― 1.0 V Transition frequency f T V CE = 10 V, I C = 100 mA ― 100 ― MHz Collector output capacitance C ob V CB = 10 V, I E = 0, f = 1 MHz ― 20 ― pF MarkingC4793lead (Pb)-free package orlead (Pb)-free finish.Collector-emitter voltage V CE (V) I C – V CEC ol le c t o r c u r r e n tI C (A )Base-emitter voltage V BE (V)I C – V BEC o l l ec t o r c u r r e n t I C(A )Collector current I C (A)V CE (sat) – I CD C c u r r e n t g a i nh F ECollector current I C (A)V CE (sat) – I CC o l l e c t o r -e m i t t e r s a t u r a t io n vo l t a g e V C E (s a t )(V )Collector current I C (mA) f T – I CT r a n s it i on f r e q u e n c yf T (M H z )Collector-emitter voltage V CE (V)Safe Operating AreaC o l l e c t o r c u r r e n t I C (A )131030 100 300RESTRICTIONS ON PRODUCT USE20070701-EN •The information contained herein is subject to change without notice.•TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the “Handling Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc.• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer’s own risk.•The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.• Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.。

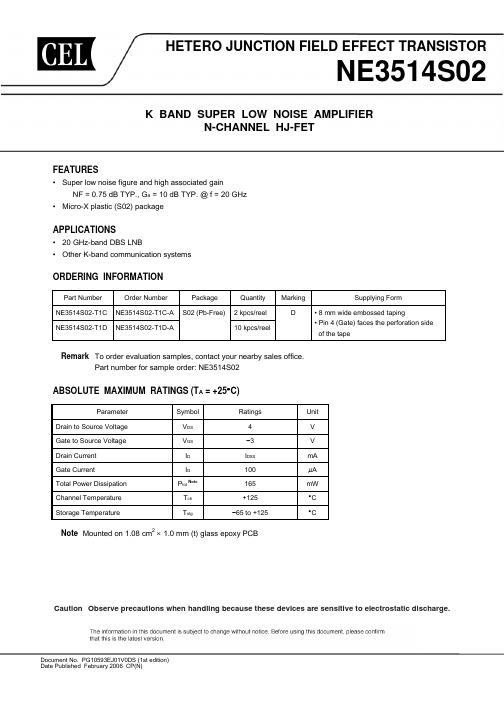

Caution Observe precautions when handling because these devices are sensitive to electrostatic discharge.HETERO JUNCTION FIELD EFFECT TRANSISTORNE3514S02K BAND SUPER LOW NOISE AMPLIFIERN-CHANNEL HJ-FETFEATURES• Super low noise figure and high associated gain NF = 0.75 dB TYP., G a = 10 dB TYP. @ f = 20 GHz • Micro-X plastic (S02) packageAPPLICATIONS• 20 GHz-band DBS LNB• Other K-band communication systemsORDERING INFORMATIONPart NumberOrder NumberPackageQuantity Marking Supplying FormNE3514S02-T1C NE3514S02-T1C-A 2 kpcs/reel DNE3514S02-T1D NE3514S02-T1D-AS02 (Pb-Free) 10 kpcs/reel• 8 mm wide embossed taping• Pin 4 (Gate) faces the perforation side of the tapeRemark To order evaluation samples, contact your nearby sales office.Part number for sample order: NE3514S02ABSOLUTE MAXIMUM RATINGS (T A = +25°C)Parameter Symbol Ratings UnitDrain to Source Voltage V DS 4 V Gate to Source Voltage V GS −3 V Drain Current I DI DSS mAGate CurrentI G 100 µA Total Power Dissipation P totNote165 mWChannel Temperature T ch +125 °C Storage TemperatureT stg−65 to +125°CNote Mounted on 1.08 cm 2 × 1.0 mm (t) glass epoxy PCBDocument No. PG10593EJ01V0DS (1st edition) Date Published February 2006 CP(N)RECOMMENDED OPERATING CONDITIONS (T A = +25°C)MAX.TYP.UnitMIN.Parameter SymbolDrain to Source Voltage V DS 1 2 3 VDrain Current I D 5 10 15 mAInput Power P in−−0 dBmELECTRICAL CHARACTERISTICS (T A = +25°C, unless otherwise specified)MAX.UnitConditions MIN.TYP.Parameter Symbol TestGate to Source Leak Current I GSO V GS = −3 V −0.5 10 µASaturated Drain Current I DSS V DS = 2 V, V GS = 0 V 15 40 70 mAGate to Source Cutoff Voltage V GS (off)V DS = 2 V, I D = 100 µA −0.2 −0.7 −2.0 V Transconductance g m V DS = 2 V, I D = 10 mA 40 55 −mSNoise Figure NF V DS = 2 V, I D = 10 mA, f = 20 GHz −0.75 1.0 dB Associated Gain G a8 10 −dB2Data Sheet PG10593EJ01V0DSTYPICAL CHARACTERISTICS (T A = +25°C, unless otherwise specified)T o t a l P o w e r D i s s i p a t i o n P t o t (m W )Ambient Temperature T A (˚C)vs. AMBIENT TEMPERATURETOTAL POWER DISSIPATION25020015010050050100150200250806040200–2.0–1.0D r a i n C u r r e n t I D (m A )Gate to Source Voltage V GS (V)DRAIN CURRENT vs.GATE TO SOURCE VOLTAGEV DS = 2 VD r a i n C u r r e n t I D (m A )Drain to Source Voltage V DS (V)DRAIN TO SOURCE VOLTAGEDRAIN CURRENT vs.Mounted on Glass Epoxy PCB (1.08 cm 2 × 1.0 mm (t) )Frequency f (GHz)M i n i m u m N o i s e F i g u r e N F m i n (d B )A s s o c i a t e d G a i n G a (dB )ASSOCIATED GAIN vs. FREQUENCYMINIMUM NOISE FIGURE,Remark The graphs indicate nominal characteristics.Data Sheet PG10593EJ01V0DS3S-PARAMETERSS-parameters/Noise parameters are provided on the NEC Compound Semiconductor Devices Web site in a form (S2P) that enables direct import to a microwave circuit simulator without keyboard input.Click here to download S-parameters.[RF and Microwave] → [Device Parameters]URL /4Data Sheet PG10593EJ01V0DSRF MEASURING LAYOUT PATTERN (REFERENCE ONLY) (UNIT: mm)RT/duroid 5880/ROGERSt = 0.254 mmεr = 2.20tan delta = 0.0009 @10 GHzData Sheet PG10593EJ01V0DS 5PACKAGE DIMENSIONSS02 (UNIT: mm)PIN CONNECTIONS1. Source2. Drain3. Source4. Gate(Top View)(Side View)(Bottom View)Data Sheet PG10593EJ01V0DS6RECOMMENDED SOLDERING CONDITIONSThis product should be soldered and mounted under the following recommended conditions. For solderingmethods and conditions other than those recommended below, contact your nearby sales office.Symbol Soldering Method Soldering Conditions Condition Infrared Reflow Peak temperature (package surface temperature) : 260°C or belowIR260Time at peak temperature : 10 seconds or lessTime at temperature of 220°C or higher : 60 seconds or less120±30 secondsPreheating time at 120 to 180°C :Maximum number of reflow processes : 3 timesMaximum chlorine content of rosin flux (% mass) : 0.2%(Wt.) or belowPartial Heating Peak temperature (terminal temperature) : 350°C or belowHS350Soldering time (per side of device) : 3 seconds or lessMaximum chlorine content of rosin flux (% mass) : 0.2%(Wt.) or belowCaution Do not use different soldering methods together (except for partial heating).Data Sheet PG10593EJ01V0DS 74590 Patrick Henry DriveSanta Clara, CA 95054-1817Telephone: (408) 919-2500Facsimile: (408) 988-0279Subject: Compliance with EU DirectivesCEL certifies, to its knowledge, that semiconductor and laser products detailed below are compliant with the requirements of European Union (EU) Directive 2002/95/EC Restriction on Use of Hazardous Substances in electrical and electronic equipment (RoHS) and the requirements of EU Directive 2003/11/EC Restriction on Penta and Octa BDE.CEL Pb-free products have the same base part number with a suffix added. The suffix –A indicates that the device is Pb-free. The –AZ suffix is used to designate devices containing Pb which are exempted from the requirement of RoHS directive (*). In all cases the devices have Pb-free terminals. All devices with these suffixes meet the requirements of the RoHS directive.This status is based on CEL’s understanding of the EU Directives and knowledge of the materials that go into its products as of the date of disclosure of this information.Restricted Substanceper RoHS Concentration Limit per RoHS(values are not yet fixed)Concentration containedin CEL devices-A -AZLead (Pb) < 1000 PPMNot Detected (*) Mercury < 1000 PPM Not DetectedCadmium < 100 PPM Not Detected Hexavalent Chromium < 1000 PPM Not DetectedPBB < 1000 PPM Not DetectedPBDE < 1000 PPM Not DetectedIf you should have any additional questions regarding our devices and compliance to environmental standards, please do not hesitate to contact your local representative.Important Information and Disclaimer: Information provided by CEL on its website or in other communications concerting the substance content of its products represents knowledge and belief as of the date that it is provided. CEL bases its knowledge and belief on information provided by third parties and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. CEL has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. CEL and CEL suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall CEL’s liability arising out of such information exceed the total purchase price of the CEL part(s) at issue sold by CEL to customer on an annual basis.See CEL Terms and Conditions for additional clarification of warranties and liability.。

2SC3503/KSC3503 — NPN Epitaxial Silicon Transistor2SC3503/KSC3503 — NPN Epitaxial Silicon TransistorElectrical Characteristics* T a =25°C unless otherwise noted* Pulse Test: Pulse Width ≤300µs, Duty Cycle ≤2%Ordering Information* 1. Affix “-S-” means the standard TO126 Package.(see package dimensions). If the affix is ”-STS-” instead of “-S-”, that mean the short-lead TO126 package. 2. Suffix “-TU” means the tube packing, The Suffix “TU” could be replaced to other suffix character as packing method.SymbolParameterTest ConditionMin.Typ.Max.UnitsBV CBO Collector-Base Breakdown Voltage I C = 10µA, I E = 0300V BV CEO Collecto- Emitter Breakdown Voltage I C = 1mA, I B = 0300V BV EBO Emitter-Base Breakdown Voltage I E = 10µA, I C = 05VI CBO Collector Cut-off Current V CB = 200V, I E = 00.1µA I EBO Emitter Cut-off Current V EB = 4V, I C = 00.1µAh FE DC Current GainV CE = 10V, I C = 10mA 40320 V CE (sat) Collector-Emitter Saturation Voltage I C = 20mA, I B = 2mA 0.6V V BE (sat) Base-Emitter Saturation Voltage I C = 20mA, I B = 2mA 1V f TCurrent Gain Bandwidth Product V CE = 30V, I C = 10mA 150MHz C ob Output CapacitanceV CB = 30V, f = 1MHz 2.6pF C reReverse Transfer CapacitanceV CB = 30V, f = 1MHz1.8pFPart Number*MarkingPackagePacking MethodRemarks2SC3503CSTU 2SC3503C TO-126TUBE hFE1 C grade 2SC3503DSTU 2SC3503D TO-126TUBE hFE1 D grade 2SC3503ESTU 2SC3503E TO-126TUBE hFE1 E grade 2SC3503FSTU 2SC3503F TO-126TUBE hFE1 F grade KSC3503CSTU C3503C TO-126TUBE hFE1 C grade KSC3503DSTU C3503D TO-126TUBE hFE1 D grade KSC3503ESTU C3503E TO-126TUBE hFE1 E grade KSC3503FSTUC3503FTO-126TUBEhFE1 F grade2SC3503/KSC3503 — NPN Epitaxial Silicon Transistor2SC3503/KSC3503 NPN Epitaxial Silicon Transistor2SC3503/KSC3503Rev. I31TRADEMARKSThe following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use andis not intended to be an exhaustive list of all such trademarks.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms ACEx ®Build it Now™CorePLUS™CROSSVOLT ™CTL™Current Transfer Logic™EcoSPARK ®Fairchild ®Fairchild Semiconductor ®FACT Quiet Series™FACT ®FAST ®FastvCore™FPS™FRFET ®Global Power Resource SMGreen FPS™Green FPS™ e-Series™GTO™i-Lo ™IntelliMAX™ISOPLANAR™MegaBuck™MICROCOUPLER™MicroFET™MicroPak™MillerDrive™Motion-SPM™OPTOLOGIC ®OPTOPLANAR ®®PDP-SPM™Power220®Power247®POWEREDGE ®Power-SPM™PowerTrench ®Programmable Active Droop™QFET ®QS™QT Optoelectronics™Quiet Series™RapidConfigure™SMART START™SPM ®STEALTH™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™The Power Franchise ®TinyBoost™TinyBuck™TinyLogic ®TINYOPTO™TinyPower™TinyPWM™TinyWire™µSerDes™UHC ®UniFET™VCX™Datasheet Identification Product Status DefinitionAdvance InformationFormative or In DesignThis datasheet contains the design specifications for product development. Specifications may change in any manner without notice.Preliminary First ProductionThis datasheet contains preliminary data; supplementary data will be pub-lished at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.No Identification Needed Full ProductionThis datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. Obsolete Not In ProductionThis datasheet contains specifications on a product that has been discontin-ued by Fairchild semiconductor. The datasheet is printed for reference infor-mation only.。

Document # SRAM112 REV ADESCRIPTIONThe P4C188 and P4C188L are 65,536-bit ultra high speed static RAMs organized as 16K x 4. The CMOS memories require no clocks or refreshing and have equal access and cycle times. Inputs and outputs are fully TTL-compatible.The RAMs operate from a single 5V±10% tolerance power supply. With battery backup, data integrity is maintained for supply voltages down to 2.0V. Current drain is typically 10µA from a 2.0V supply.Single 5V±10% Power Supply Data Retention with 2.0V Supply (P4C188L Military)Three-State OutputsTTL/CMOS Compatible Outputs Fully TTL Compatible InputsStandard Pinout (JEDEC Approved)– 22-Pin 300 mil DIP – 24-Pin 300 mil SOJ– 22-Pin 290 x 490 mil LCCFEATURESFull CMOS, 6T CellHigh Speed (Equal Access and Cycle Times)– 10/12/15/20/25 ns (Commercial)– 12/15/20/25/35 (Industrial)– 15/20/25/35/45 ns (Military)Low Power (Commercial/Military)– 715 mW Active – 12/15– 550/660 mW Active – 20/25/35/45– 193/220 mW Standby (TTL Input)– 83/110 mW Standby (CMOS Input) P4C188– 15 mW Standby (CMOS Input) (P4C188L Military)FUNCTIONAL BLOCK DIAGRAM PIN CONFIGURATIONSP4C188/P4C188LULTRA HIGH SPEED 16K x 4STATIC CMOS RAMSDIP (P3, D3, C3)LCC (L3)For SOJ pin configuration, please see end of datasheet.Access times as fast as 10 nanoseconds are available,permitting greatly enhanced system speeds. CMOS is utilized to reduce power consumption to a low 715mW active, 193mW standby and only 5mW in the P4C188L version.The P4C188 and P4C188L are available in 22-pin 300 mil DIP, 24-pin 300 mil SOJ and 22-pin LCC packages provid-ing excellent board level densities.P4C188/188LMAXIMUM RATINGS (1)Symbol Parameter Value Unit V CCPower Supply Pin with –0.5 to +7VRespect to GND Terminal Voltage with –0.5 to V TERM Respect to GND V CC +0.5V (up to 7.0V)T AOperating Temperature–55 to +125°CSymbol Parameter Value Unit T BIAS Temperature Under –55 to +125°C BiasT STG Storage Temperature –65 to +150°C P T Power Dissipation 1.0W I OUTDC Output Current50mARECOMMENDED OPERATINGTEMPERATURE AND SUPPLY VOLTAGEIndustrialCommercialGrade(2)Ambient TemperatureGND V CC–40°C to +85°C 0°C to +70°C 0V 0V5.0V ± 10%5.0V ± 10%0V 5.0V ± 10%–55°C to +125°C MilitarySymbol C IN C OUTParameter Input Capacitance Output CapacitanceConditions V IN = 0V V OUT = 0V57Unit pF pFCAPACITANCES (4)V CC = 5.0V, T A = 25°C, f = 1.0MHz n/a = Not ApplicableDC ELECTRICAL CHARACTERISTICSOver recommended operating temperature and supply voltage (2)Notes:1.Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.2.Extended temperature operation guaranteed with 400 linear feet per minute of air flow.3.Transient inputs with V IL and I IL not more negative than –3.0V and –100mA, respectively, are permissible for pulse widths up to 20 ns.4.This parameter is sampled and not 100% tested.Typ. I SBStandby Power Supply Current (TTL Input Levels)CE ≥ V IH Mil.V CC = Max ., Ind./Com’l.f = Max., Outputs Open ______4035____________201540n/a 2.7n/amAmA______CE ≥ V HC Mil.V CC = Max., Ind./Com’l.f = 0, Outputs Open V IN ≤ V LC or V IN ≥ V HCStandby Power Supply Current(CMOS Input Levels)I SB1Symbol V IH V IL V HC V LC V CD V OL V OH I LI I LO ParameterInput High Voltage Input Low Voltage CMOS Input High Voltage CMOS Input Low VoltageInput Clamp Diode Voltage Output Low Voltage (TTL Load)Output High Voltage (TTL Load)Input Leakage Current Output Leakage CurrentTest ConditionsV CC = Min., I IN = 18 mA I OL = +8 mA, V CC = Min.I OH = –4 mA, V CC = Min.V CC = Max. Mil.V IN = GND to V CC Com’l.V CC = Max., CE = V IH , Mil.V OUT = GND to V CC Com’l.P4C188Min 2.2–0.5(3)V CC –0.2–0.5(3)2.4–10–5–10–5Max V CC +0.50.8V CC +0.50.2–1.20.4+10+5+10+5P4C188LMin Max 2.2–0.5(3)V CC –0.2–0.5(3)2.4–5n/a –5n/a V CC +0.50.8V CC +0.50.20.4–1.2+5n/a +5n/a UnitV V V V V V V µA µA 元器件交易网*V CC = 5.5V. Tested with outputs open. f = Max. Switching inputs are 0V and 3V. CE = V ILDATA RETENTION CHARACTERISTICS (P4C188L Military Temperature Only)Symbol V DR I CCDR t CDR t R †ParameterV CC for Data Retention Data Retention Current Chip Deselect to Data Retention Time Operation Recovery TimeTest ConditionsCE ≥ V CC –0.2V,V IN ≥ V CC –0.2V or V IN ≤ 0.2V Min 2.00t RC §Typ.*V CC =2.0V3.0V1015Max V CC = 2.0V 3.0V600900Unit V µA ns nsDATA RETENTION WAVEFORM*T A = +125°C§t RC = Read Cycle Time†This parameter is guaranteed but not tested.I CCSymbolParameterTemperatureRange Dynamic Operating Current*CommercialIndustrial Military–10N/A–12–15–20–25–35–45Unit N/A mA mA mAPOWER DISSIPATION CHARACTERISTICS VS. SPEEDN/A 150155160170180N/A170160155150145180170160155150N/A N/AP4C188/188LAC CHARACTERISTICS—READ CYCLE(V CC = 5V ± 10%, All Temperature Ranges)(2)Notes:5.CE is LOW and WE is HIGH for READ cycle.6.WE is HIGH, and address must be valid prior to or coincident with CE transition LOW.7.Transition is measured ±200mV from steady state voltage prior to change with specified loading in Figure 1. This parameter is sampled and not 100% tested.8.Read Cycle Time is measured from the last valid address to the first transitioning address.TIMING WAVEFORM OF READ CYCLE NO. 2(6)TIMING WAVEFORM OF READ CYCLE NO. 1(5)Sym.t RC t AA t AC t OH t LZ t HZ t PU t PDParameterRead Cycle Time Address Access Time Chip Enable Access Time Output Hold from Address Change Chip Enable to Output in Low Z Chip Disable to Output in High Z Chip Enable to Power Up Time Chip Disable to Power Down Time-10Min 1022Max 1010510-12Min 12220Max 1212612-15Min 15220Max 1515615-20Min 20230Max 2020820-25Min 25230Max 25251025-35Min 35230Max 35352035-45Min 4523Max45452545Unit ns ns ns ns nsns nsns12.Transition is measured ±200mV from steady state voltage prior tochange with specified loading in Figure 1. This parameter is sampled and not 100% tested.Notes:9.CE and WE must be LOW for WRITE cycle.10.If CE goes HIGH simultaneously with WE HIGH, the output remainsin a high impedance state.11.Write Cycle Time is measured from the last valid address to the firsttransition address.TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED) (9)AC CHARACTERISTICS - WRITE CYCLE(V CC = 5V ± 10%, All Temperature Ranges)(2)Sym.Parameter -10-12-15-20-25-35-45Unit Min Min Min Min Min Min Min Max Max Max Max Max Max Maxt WC t CWt AW t AS t WP t AHt DW t DH t WZt DWWrite Cycle Time Chip Enable Time toEnd of Write Address Valid to End of Write Address Set-up Time Write Pulse Width Address Hold Time from End of Write Data Valid to End of Write Data Hold Time Write Enable to Output in High Z Output Active from End of Write107708050251288090602613101001007026201315013080282515200150100235252502501503154535350350205320ns nsns ns ns nsns ns nsns10元器件交易网P4C188/188LTIMING WAVEFORM OF WRITE CYCLE NO. 2 (CE CONTROLLED)(9)Input Pulse Levels GND to 3.0VInput Rise and Fall Times 3ns Input Timing Reference Level 1.5V Output Timing Reference Level 1.5VOutput LoadSee Figures 1 and 2Mode CE WE Output Power Standby H X High Z Standby Read L H D OUT Active WriteLLD INActive* including scope and test fixture.Note:Because of the ultra-high speed of the P4C188/L, care must be taken when testing this device; an inadequate setup can cause a normal functioning part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the V CC and ground planes directly up to the contactor fingers. A 0.01 µF high frequencycapacitor is also required between V CC and ground. To avoid signal reflections, proper termination must be used; for example, a 50Ω test environment should be terminated into a 50Ω load with 1.73V (Thevenin Voltage) at the comparator input, and a 116Ω resistor must be used in series with D OUT to match 166Ω (Thevenin Resistance).Figure 1. Output LoadFigure 2. Thevenin EquivalentAC TEST CONDITIONSTRUTH TABLE元器件交易网ORDERING INFORMATION1513 10 SELECTION GUIDEThe P4C188/L is available in the following temperature, speed and package options. The P4C188L is only available over the Military Temperature range.* Military temperature range with MIL-STD-883, Class B processing.N/A = Not AvailableP4C188/188LSOJ PIN CONFIGURATIONSOJ (J4)SIDE BRAZED DUAL IN-LINE PACKAGEP4C188/188LSOJ SMALL OUTLINE IC PACKAGEPLASTIC DUAL IN-LINE PACKAGEP4C188/188LREVISIONSDOCUMENT NUMBER:SRAM112DOCUMENT TITLE:P4C188 / P4C188L ULTRA HIGH SPEED 16K x 4 STATIC CMOS RAMSREV.ISSUEDATEORIG. OFCHANGEDESCRIPTION OF CHANGEOR1997DAB New Data SheetA Oct-05JDB Change logo to Pyramid 元器件交易网。

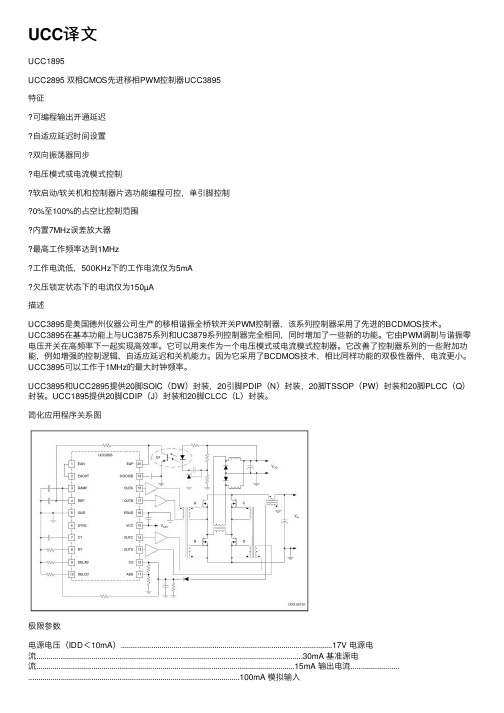

UCC译⽂UCC1895UCC2895 双相CMOS先进移相PWM控制器UCC3895特征可编程输出开通延迟⾃适应延迟时间设置双向振荡器同步电压模式或电流模式控制软启动/软关机和控制器⽚选功能编程可控,单引脚控制0%⾄100%的占空⽐控制范围内置7MHz误差放⼤器最⾼⼯作频率达到1MHz⼯作电流低,500KHz下的⼯作电流仅为5mA⽋压锁定状态下的电流仅为150µA描述UCC3895是美国德州仪器公司⽣产的移相谐振全桥软开关PWM控制器,该系列控制器采⽤了先进的BCDMOS技术。

UCC3895在基本功能上与UC3875系列和UC3879系列控制器完全相同,同时增加了⼀些新的功能。

它由PWM调制与谐振零电压开关在⾼频率下⼀起实现⾼效率。

它可以⽤来作为⼀个电压模式或电流模式控制器。

它改善了控制器系列的⼀些附加功能,例如增强的控制逻辑、⾃适应延迟和关机能⼒。

因为它采⽤了BCDMOS技术,相⽐同样功能的双极性器件,电流更⼩。

UCC3895可以⼯作于1MHz的最⼤时钟频率。

UCC3895和UCC2895提供20脚SOIC(DW)封装,20引脚PDIP(N)封装,20脚TSSOP(PW)封装和20脚PLCC(Q)封装。

UCC1895提供20脚CDIP(J)封装和20脚CLCC(L)封装。

简化应⽤程序关系图极限参数电源电压(IDD<10mA)........................................................................................................17V 电源电流...................................................................................................................................30mA 基准源电流...............................................................................................................................15mA 输出电流........................ ........................................................................................................100mA 模拟输⼊(EAP,EAN,EAOUT,RAMP,SYNC,ADS,CS,SS /DISB).....–0.3V⾄REF +0.3V TA = +25℃的功耗(N封装)....................................................................................................1W TA = + 25℃的功耗(D封装)............................................................................................650mW 存储温度……………………………………………………………….................- 65℃~ +150℃结温.........................................................................................................................- 55℃~ +125℃引线温度(焊接,10秒)…………………………………………………………...........+ 300℃设计应考虑最⼤的输⼊电流和恶劣的输出环境,应参考数据⼿册中封装的热限制。

© 2002 Fairchild Semiconductor Corporation DS005961October 1987Revised April 2002CD4030C Quad EXCLUSIVE-OR GateCD4030CQuad EXCLUSIVE-OR GateGeneral DescriptionThe CD4030C EXCLUSIVE-OR gates are monolithic com-plementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. All inputs are protected against static discharge with diodes to V DD and V SS .Featuress Wide supply voltage range: 3.0V to 15Vs Low power:100 nW (typ.)s Medium speed operation:t PHL = t PLH = 40 ns (typ.) at C L = 15 pF, 10V supply s High noise immunity0.45 V CC (typ.)Applications•Automotive •Data terminals •Instrumentation •Medical electronics •Industrial controls •Remote metering •ComputersOrdering Code:Device also available in Tape and Reel. Specify by appending suffix letter “X ” to the ordering code.Connection Diagram Truth Table1 = HIGH Level 0 = LOW LevelOrder Number Package NumberPackage DescriptionCD4030CSJ M14D 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide CD4030CNN14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WideA B J 0 0 0 1 0 1 0 1 1 11 2C D 4030CLogic DiagramCD4030CAbsolute Maximum Ratings (Note 1)Note 1: “Absolute Maximum Ratings ” are those values beyond which the safety of the device cannot be guaranteed. Except for “Operating Tempera-ture Range ” they are not meant to imply that the devices should be oper-ated at these limits. The Electrical Characteristics tables provide conditions for actual device operation.Note 2: This device should not be connected to circuits with power on because high transient voltages may cause permanent damage.DC Electrical CharacteristicsNote 3: I D N and I D P are tested one output at a time.AC Electrical Characteristics (Note 4)Note 4: AC Parameters are guaranteed by DC correlated testing.Voltage at Any Pin (Note 2) V SS −0.3V to V SS +15.5VOperating Temperature Range −55°C to +125°C Storage Temperature Range −65°C to +150°CPower Dissipation (P D ) Dual-In-Line 700 mWSmall Outline500 mWOperating V DD Range V SS +3.0V to V SS +15VLead Temperature (Soldering, 10 seconds)260°CSymbol Parameter Conditions −55°C+25°C +125°C Units MinTypMax MinTyp Max MinTypMax I L Quiescent Device V DD = 5.0V 0.5 0.0050.5 30 µA CurrentV DD = 10V 1.0 0.01 1.0 60 P D Quiescent Device V DD = 5.0V 2.5 0.025 2.5 150 µW Dissipation Package V DD = 10V 100.1 10 600 V OL Output Voltage V DD = 5.0V 0.05 0 0.05 0.05 V LOW Level V DD = 10V 0.050 0.050.05V OH Output Voltage V DD = 5.0V 4.95 4.95 5.0 4.95 V HIGH Level V DD = 10V 9.95 9.95 10 9.95 V NL Noise Immunity V DD = 5.0V 1.5 1.5 2.25 1.4 V (All Inputs) V DD = 10V 3.0 3.0 4.5 2.9 V NH Noise Immunity V DD = 5.0V 1.4 1.5 2.25 1.5 V (All Inputs)V DD = 10V 2.9 3.0 4.5 3.0I D N Output Drive Current V DD = 5.0V 0.75 0.6 1.2 0.45 mA N-Channel (Note 3) V DD = 10V 1.5 1.2 2.4 0.9 I D P Output Drive Current V DD = 5.0V −0.45 −0.3 −0.6 −0.21 mA P-Channel (Note 3) V DD = 10 V −0.95−0.65 −1.3 −0.45 I IInput CurrentV I = 0V or V I = V DD10pASymbol ParameterConditionsLimitsUnits MinTyp Max t PHL Propagation Delay Time V DD = 5.0V 100 300 ns V DD = 10V 40 150 t PLH Propagation Delay Time V DD = 5.0V 100 300 ns V DD = 10V 40 150 t THL Transition Time V DD = 5.0V 70 300 ns HIGH-to-LOW Level V DD = 10V 25 150 t TLH Transition Time V DD = 5.0V 80 300 ns LOW-to-HIGH Level V DD = 10V 30 150C IInput CapacitanceV I = 0V or V I = V DD5.0pF 4C D 4030CPhysical Dimensionsinches (millimeters) unless otherwise noted14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M14D5CD4030C Quad EXCLUSIVE-OR GatePhysical Dimensions inches (millimeters) unless otherwise noted (Continued)14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePackage Number N14AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

Document # SRAM111 REV BFEATURESFull CMOS, 6T CellHigh Speed (Equal Access and Cycle Times)– 10/12/15/20/25/35/45 ns (Commercial)– 12/15/20/25/35 /45 ns (Industrial)– 15/20/25/35/45/55/70/85 ns (Military)Low Power Operation – 743 mW Active -10– 660/770 mW Active for -12/15– 550/660 mW Active for -20/25 /35– 193/220 mW Standby (TTL Input)– 83/110 mW Standby (CMOS Input) P4C187– 5.5 mW Standby (CMOS Input) P4C 187L (Military)Single 5V±10% Power SupplyP4C187/P4C187LULTRA HIGH SPEED 64K x 1STATIC CMOS RAMSPIN CONFIGURATIONSFUNCTIONAL BLOCK DIAGRAM DIP (P3, D3, C3)LCC Pin configurations at end of datasheet.Data Retention with 2.0V Supply (P4C187L Military)Separate Data I/O Three-State Output TTL Compatible Output Fully TTL Compatible Inputs Standard Pinout (JEDEC Approved)– 22-Pin 300 mil DIP – 24-Pin 300 mil SOJ– 22-Pin 290x490 mil LCC – 28-Pin 350x550 mil LCCDESCRIPTIONThe P4C187/P4C187L are 65, 536-bit ultra high speed static RAMs organized as 64K x 1. The CMOS memories require no clocks or refreshing and have equal access and cycle times. The RAMs operate from a single 5V ± 10%tolerance power supply. Data integrity is maintained for sup-ply voltages down to 2.0V, typically drawing 10µA.Access times as fast as 10 nanoseconds are available,greatly enhancing system speeds. CMOS reduces powerconsumption to a low 743mW active, 193/83mW standby for TTL/CMOS inputs and only 5.5 mW standby for the P4C187L.The P4C187/P4C187L are available in 22-pin 300 mil DIP,24-pin 300 mil SOJ, 22-pin and 28-pin LCC packages pro-viding excellent board level densities.P4C187/187LMAXIMUM RATINGS (1)Symbol Parameter Value Unit V CCPower Supply Pin with –0.5 to +7VRespect to GND Terminal Voltage with –0.5 to V TERM Respect to GND V CC +0.5V (up to 7.0V)T AOperating Temperature–55 to +125°CSymbol Parameter Value Unit T BIAS Temperature Under –55 to +125°C BiasT STG Storage Temperature –65 to +150°C P T Power Dissipation 1.0W I OUTDC Output Current50mARECOMMENDED OPERATINGTEMPERATURE AND SUPPLY VOLTAGEI SBStandby Power Supply Current (TTL Input Levels)CE ≥ V IH Mil.V CC = Max ., Ind./Com’l.f = Max., Outputs Open ______4035____________201540n/a 1.0n/amAmA______CE ≥ V HC Mil.V CC = Max., Ind./Com’l.f = 0, Outputs Open V IN ≤ V LC or V IN ≥ V HCStandby Power Supply Current(CMOS Input Levels)I SB1Grade(2)Ambient TemperatureGND V CC0V 0V5.0V ± 10%5.0V ± 10%0V 5.0V ± 10%–55°C to +125°C Symbol C IN C OUTParameter Input Capacitance Output CapacitanceConditions V IN = 0V V OUT = 0V57Unit pF pFCAPACITANCES (4)V CC = 5.0V, T A = 25°C, f = 1.0MHz n/a = Not ApplicableSymbol DC ELECTRICAL CHARACTERISTICSOver recommended operating temperature and supply voltage (2)V IH V IL V HC V LC V CD V OL V OH I LI I LO ParameterInput High Voltage Input Low Voltage CMOS Input High Voltage CMOS Input Low VoltageInput Clamp Diode Voltage Output Low Voltage (TTL Load)Output High Voltage (TTL Load)Input Leakage Current Output Leakage CurrentTest ConditionsV CC = Min., I IN = 18 mA I OL = +8 mA, V CC = Min.I OH = –4 mA, V CC = Min.V CC = Max. Mil.V IN = GND to V CC Com’l.V CC = Max., CE = V IH , Mil.V OUT = GND to V CC Com’l.P4C187Min 2.2–0.5(3)V CC –0.2–0.5(3)2.4–10–5–10–5Max V CC +0.50.8V CC +0.50.2–1.20.4+10+5+10+5P4C187LMin Max 2.2–0.5(3)V CC –0.2–0.5(3)2.4–5n/a –5n/a V CC +0.50.8V CC +0.50.20.4–1.2+5n/a +5n/a UnitV V V V V V V µA µA Notes:1.Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.2.Extended temperature operation guaranteed with 400 linear feet per minute of air flow.3.Transient inputs with V IL and I IL not more negative than –3.0V and –100mA, respectively, are permissible for pulse widths up to 20 ns.4.This parameter is sampled and not 100% tested.itaryIndustrial–40°C to +85°C 0°C to +70°C Commercial*V CC = 5.5V. Tested with outputs open. f = Max. Switching inputs are 0V and 3V. CE = V IL .DATA RETENTION CHARACTERISTICS (P4C187L Military Temperature Only)Symbol V DR I CCDR t CDR t R †ParameterV CC for Data Retention Data Retention Current Chip Deselect to Data Retention Time Operation Recovery TimeTest Conditons CE ≥ V CC –0.2V,V IN ≥ V CC –0.2V or V IN ≤ 0.2VMin 2.00t RC §Typ.*V CC = 2.0V 3.0V Max V CC = 2.0V 3.0VUnit 1015600900VµA ns ns*T A = +25°C§t RC = Read Cycle Time†This parameter is guaranteed but not tested.DATA RETENTION WAVEFORMI CCSymbol ParameterTemperature RangeDynamic Operating Current*Commercial Industrial Military–10N/A–12–15–20–25–35–45Unit N/A mA mA mAPOWER DISSIPATION CHARACTERISTICS VS. SPEEDN/A 150155160170180N/A170160155150145180170160155150N/A N/A –85N/A 145N/A –70N/A 145N/A –55N/A 145N/AP4C187/187LNotes:5.CE is LOW and WE is HIGH for READ cycle.6.WE is HIGH, and address must be valid prior to or coincident with CE transition LOW.7.Transition is measured ±200mV from steady state voltage prior to change with specified loading in Figure 1. This parameter is sampled and not 100% tested.8.Read Cycle Time is measured from the last valid address to the first transitioning address.TIMING WAVEFORM OF READ CYCLE NO. 2(6)TIMING WAVEFORM OF READ CYCLE NO. 1(5)AC CHARACTERISTICS—READ CYCLE(V CC = 5V ± 10%, All Temperature Ranges)(2)Notes:9.CE and WE must be LOW for WRITE cycle.10.If CE goes HIGH simultaneously with WE HIGH, the output remainsin a high impedance state.11.Write Cycle Time is measured from the last valid address to the firsttransition address.TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED)(9)AC CHARACTERISTICS - WRITE CYCLE(V CC = 5V ± 10%, All Temperature Ranges)(2)P4C187/187LTIMING WAVEFORM OF WRITE CYCLE NO. 2 (CE CONTROLLED)(9)Figure 1. Output LoadFigure 2. Thevenin Equivalent* including scope and test fixture.Note:Due to the ultra-high speed of the P4C187/L, care must be taken when testing this device; an inadequate setup can cause a normal functioning part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the V CC and ground planes directly up to the contactor fingers. A 0.01 µF high frequency capacitor is also required between V CCand ground. To avoid signal reflections,proper termination must be used; for example, a 50Ω test environment should be terminated into a 50Ω load with 1.73V (Thevenin Voltage) at the comparator input, and a 116Ω resistor must be used in series with D OUT to match 166Ω (Thevenin Resistance).AC TEST CONDITIONSTRUTH TABLEInput Pulse Levels GND to 3.0VInput Rise and Fall Times 3ns Input Timing Reference Level 1.5V Output Timing Reference Level 1.5VOutput LoadSee Figures 1 and 2Mode CE WE Output Power Standby H X High Z Standby Read L H D OUT Active WriteLLHigh ZActiveP4C187/187LORDERING INFORMATIONSELECTION GUIDEThe P4C187 is available in the following temperature, speed and package options. The P4C187L is only available over the military temperature range.* Military temperature range with MIL-STD-883, Class B processing.N/A = Not AvailableCERDIP DUAL IN-LINE PACKAGEP4C187/187LSOJ SMALL OUTLINE IC PACKAGERECTANGULAR LEADLESS CHIP CARRIER PLASTIC DUAL IN-LINE PACKAGEP4C187/187LREVISIONSDOCUMENT NUMBER:SRAM111DOCUMENT TITLE:P4C187 / P4C187L ULTRA HIGH SPEED 64K x 1 STATIC CMOS RAMSREV.ISSUEDATEORIG. OFCHANGEDESCRIPTION OF CHANGEOR1997DAB New Data SheetA Oct-05JDB Change logo to PyramidB Apr-07JDB Added 55, 70, and 85 ns speeds 元器件交易网。