实验四 触发器实验

- 格式:pdf

- 大小:559.96 KB

- 文档页数:5

触发器功能实验报告触发器功能实验报告引言:触发器是数字电路中常见的重要元件,它能够在特定的输入条件下产生稳定的输出信号。

本实验旨在通过构建不同类型的触发器电路,探究触发器的基本原理和功能。

实验一:RS触发器RS触发器是最简单的一种触发器,由两个交叉连接的非门组成。

实验中我们使用了两个与非门来构建RS触发器电路,其中一个与非门的输出连接到另一个与非门的输入,反之亦然。

通过设置不同的输入状态,我们可以观察到RS触发器的两种稳定状态:置位和复位。

实验二:D触发器D触发器是一种常用的触发器,它具有单一输入和双输出。

实验中我们使用了两个与非门和一个或非门来构建D触发器电路。

通过输入信号的变化,我们可以观察到D触发器的工作原理:当输入信号为高电平时,输出保持之前的状态,当输入信号为低电平时,输出根据之前的状态进行切换。

实验三:JK触发器JK触发器是一种多功能的触发器,它具有两个输入和两个输出。

实验中我们使用了两个与非门和一个或非门来构建JK触发器电路。

通过设置不同的输入状态,我们可以观察到JK触发器的四种工作模式:置位、复位、切换和禁用。

实验四:T触发器T触发器是一种特殊的JK触发器,它只有一个输入和两个输出。

实验中我们使用了两个与非门和一个或非门来构建T触发器电路。

通过输入信号的变化,我们可以观察到T触发器的工作原理:当输入信号为高电平时,输出状态翻转,当输入信号为低电平时,输出保持不变。

实验五:应用实例在实验的最后,我们通过一个简单的应用实例来展示触发器的实际应用。

我们构建了一个二进制计数器电路,使用了多个D触发器和与非门。

通过输入脉冲信号,我们可以观察到计数器的工作原理:每次接收到脉冲信号,计数器的输出状态按照二进制规律进行变化。

结论:通过本次实验,我们深入了解了不同类型的触发器的功能和工作原理。

触发器在数字电路中具有重要的应用价值,能够实现各种逻辑功能和时序控制。

进一步的研究和实践将有助于我们更好地理解和应用触发器,提高数字电路设计的能力。

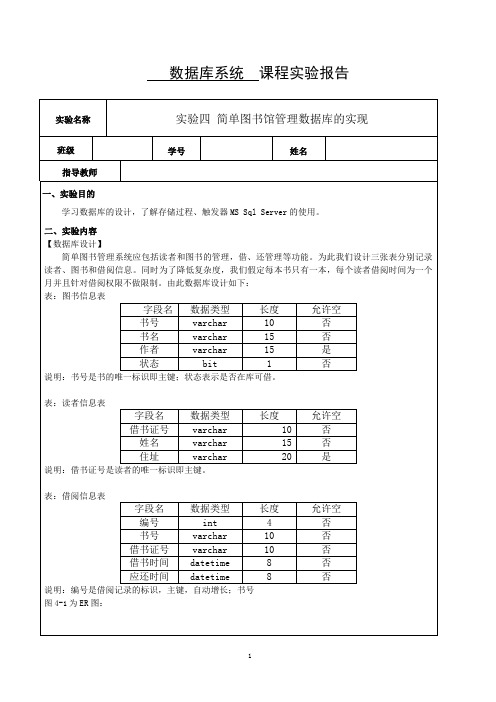

数字电路实验报告姓名:张珂班级:10级8班学号:2010302540224实验一:组合逻辑电路分析一.实验用集成电路引脚图1.74LS00集成电路2.74LS20集成电路二、实验内容1、组合逻辑电路分析逻辑原理图如下:U1A 74LS00NU2B74LS00NU3C74LS00N X12.5 VJ1Key = Space J2Key = Space J3Key = Space J4Key = SpaceVCC5VGND图1.1组合逻辑电路分析电路图说明:ABCD 按逻辑开关“1”表示高电平,“0”表示低电平; 逻辑指示灯:灯亮表示“1”,灯不亮表示“0”。

真值表如下: A B C D Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1表1.1 组合逻辑电路分析真值表实验分析:由实验逻辑电路图可知:输出X1=AB CD =AB+CD ,同样,由真值表也能推出此方程,说明此逻辑电路具有与或功能。

2、密码锁问题:密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开;否则,报警信号为“1”,则接通警铃。

试分析下图中密码锁的密码ABCD 是什么? 密码锁逻辑原理图如下:U1A74LS00NU2B74LS00NU3C 74LS00NU4D 74LS00NU5D 74LS00NU6A74LS00N U7A74LS00NU8A74LS20D GNDVCC5VJ1Key = SpaceJ2Key = SpaceJ3Key = SpaceJ4Key = SpaceVCC5VX12.5 VX22.5 V图 2 密码锁电路分析实验真值表记录如下:实验真值表 A B CD X1 X2 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 0 1 1 11 10 1表1.2 密码锁电路分析真值表实验分析:由真值表(表1.2)可知:当ABCD 为1001时,灯X1亮,灯X2灭;其他情况下,灯X1灭,灯X2亮。

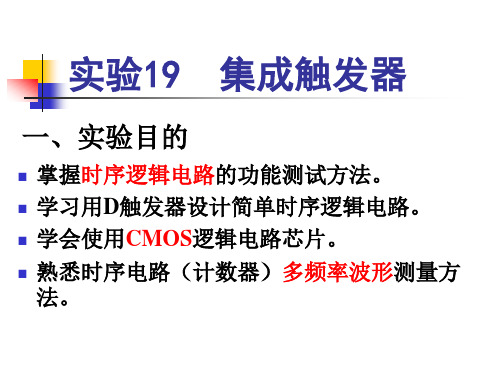

实验四双稳态触发器一、实验目的1.熟悉并验证触发器的逻辑功能和触发方式。

2.掌握集成JK 和D 触发器的使用方法和逻辑功能的测试方法。

3.掌握用JK 或D 触发器组成分频器的方法。

二、实验原理及实验资科触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元。

触发器具有两个稳定状态,即"0"和"1",在适当触发信号作用下,触发器的状态发生翻转,即触发器可由一个稳态转换到另一个稳态.当输入触发信号消失后,触发器翻转后的状态保持不变(记忆功能)。

根据电路结构的不同,触发器的触发方式不同,有电平触发,主从触发和边沿触发。

根据功能的不同,触发器有RS 触发器,JK 触发器,D 触发器,T 触发器,T ′触发器等类型。

集成触发器的主要产品是JK 触发器和D 触发器,其他功能的触发器可由JK,D 触发器进行转换。

电路结构和触发方式与功能无必然联系。

比如JK 触发器既有主从式的,又有边沿式的,而主从触发器和边沿触发器都有RS 、JK 、D 触发器。

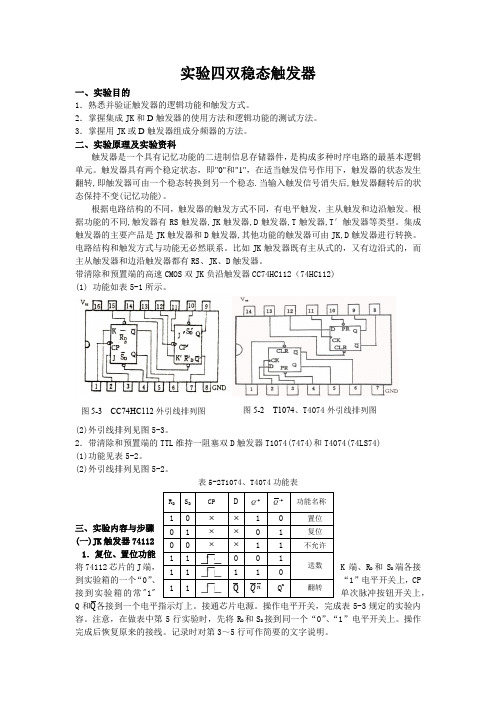

带清除和预置端的高速CMOS 双JK 负沿触发器CC74HC112(74HC112) (1) 功能如表5-1所示。

(2)外引线排列见图5-3。

2.带清除和预置端的TTL 维持一阻塞双D 触发器T1074(7474)和T4074(74LS74) (1)功能见表5-2。

(2)外引线排列见图5-2。

表5-2T1074、T4074功能表三、实验内容与步骤 (一)JK 触发器74112 1.复位、置位功能将74112芯片的J 端,K 端、R D 和S D 端各接到实验箱的一个“0”、“1”电平开关上,CP 接到实验箱的常"1"单次脉冲按钮开关上,Q 和各接到一个电平指示灯上。

接通芯片电源。

操作电平开关,完成表5-3规定的实验内容。

注意,在做表中第5行实验时,先将R D 和S D 接到同一个“0”、“1”电平开关上。

实验四基本RS触发器和D触发器一、实验目的1.熟悉并验证触发器的逻辑功能;2.掌握RS和D触发器的使用方法和逻辑功能的测试方法。

二、实验预习要求1.预习触发器的相关内容;2.熟悉触发器功能测试表格。

三、实验原理触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元。

触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

1.基本RS触发器图实验4.1为由两个与非门交叉耦合构成的基本RS触发器。

基本RS触发器具有置“0”、置“1”和“保持”三种功能。

通常称S为置“1”端,因为S=0时触发器被置“1”;R端为置“0”端,因为R=0时触发器被置“0”;当S =R =1时,触发器状态保持。

基本RS触发器也可图实验4.1 基本RS触发器以用两个“或非门”组成,此时为高电平有效置位触发器。

2. D触发器D触发器的状态方程为:Q n+1=D。

其状态的更新发生在CP脉冲的边沿,74LS74(CC4013)、74LS175(CC4042)等均为上升沿触发,故又称之为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前D端的状态。

D触发器应用很广,可用做数字信号的寄存、移位寄存、分频和波形发生器等。

四、实验仪器设备1、TPE-AD数字实验箱1台2、双D触发器74LS74 2片3、四两输入集成与非门74LS00 1片4、双通道示波器 1台五、实验内容及方法1.测试基本RS 触发器的逻辑功能按图实验4.1连接电路,用两个与非门组成基本RS 触发器,输入端S 、R 接逻辑开关的输出口,输出端Q 、Q 接逻辑电平显示灯输入接口,按表实验4.1的要求测试并记录。

表实验4.1 RS 触发器的逻辑功能2.测试D(1)测试D R 、D S 的复位、置位功能。

在D R =0,D S =1作用期间,改变D 与CP 的状态,观察 Q 、Q 状态。

在D R =1,D S =0作用期间,改变D 与CP 的状态,观察Q 、Q 状态。

SQL实验报告(优秀范文5篇)第一篇:SQL实验报告实验四触发器实验(一)after触发器(1 1)在l l i neitem 表上定义一个 after 触发器, , 当修改列项目e e xtendedprice d i scountx tax 时, , 要把 s orders 表得to o tal pri ce e 一起修改, , 以保证数据一致性C RE ATE T RIGGERtrig _line ite m_ pr ice_ update on line it em fo rupda teaasbegin i f(UPDATE(ex tend edprice)o r UPDATE(tax)or UPD AT E(di scou nt))begin-—声明游标变量指向 inserted 表d eclarecursor_inserted c urs orrea d_onlyofor select order key,linenu mber,exte nd edpr ice, dis coun t, taxfromin ser ted—-息信找查取获量变明声ﻩ声明变量获取查找信息de clare order key in t, @linenumb erint,exte nd edpricereal,disscount real,tax real—-打开游标epoﻩen cursor_i ns ert ed—-标游取读ﻩ读取游标fe tchnextfrom cur sor _i ns erte dint o@o rderkey, @lin enumber,eext ende dprice, @di scount,t axwwhi le FETC H_S TATUS =0 nigebﻩnﻩ—-声明一个变量保存重新计算得新价格cedﻩﻩecl are @n ew_tota lpri cer ealﻩ select @n ew_t otal price= @ext en dedpr ice *(1 -@di scou nt)*(1 +@tax)—-用新得总价格变量更新 orders 表得 t ot alprice puﻩﻩupdate orde rsse t tot alpri ce= new_totalprice where or derkey=orde rkeyen hctefﻩext f ro m cur sor_i nser ted int o@order ke y, @li nenum ber, @ex tende dp rice,discoun t, @taxdneﻩllaedﻩlocate c ur sor_i nser te deend end ﻩ(2)在在 linei tem表上定义一个 aftr er 触发器, , 当增加一项订单明细时, ,自动修改 s orders 表得 total p rice, 以保证数据一致性CREATE TR IGGER tri g_ lineit em_price_ in sert on l ine item ffor inse rta sbegin ——向指量变标游明声ﻩ声明游标变量指向ins erted 表de clarec ursor_inse rtedcursorread_ onl yﻩ for s ele ct orderkey,linenumbe r,ex te ndedp ric e,di scou nt,t axfrom insserte d--声明变量获取查找信息edﻩeclare @orde rk eyint, @lin enumber int,e xten dedp ricereal, @discountreal, @ta xreal -—ﻩ-打开游标open cursor_i ns erte d--ﻩ-读取游标fe tc hnex tf romcu rsor_ins ertedinto@o rd erkey,li nen umbeerr, ex ten ded pric e,dis count,tax ihwﻩile @@FE TCH_ STATU S=0 ebﻩegin-—格价新得算计新重存保量变个一明声ﻩﻩ声明一个变量保存重新计算得新价格cedﻩclare @n ew_tot alprice realcelesﻩct new _to ta lprice= @extend edp rice *(1-d is count)*(1+tax)—-新更量变格价总得新用ﻩﻩ用新得总价格变量更新orders 表得totalpri ceﻩ u pda teor ders s ett ota lpric e=total pric e+ @new_ tota lpr ice wwhhe re o rderke y=orderkeytefﻩetch next from cursor_ ins erte dinto o rder key, @l inen umber,e xtendeddp ric e, @disc ou nt, @t axeend aedﻩdeall oca te cu rsor_in serted en d(3)在l in e ite m表上定义一个a ft er触发器, , 当删除一项订单明细记录时, ,自动修改 orders 表得 tot a lprice, 以保证数据一致性CREATE TRI GG ER trig _line item_price_de let eon line item fo r de let eAAS begin--声明游标变量指向delet ed 表de clar e curso r_d eleted cursorre ad _on lyesrofﻩﻩele ctord erk ey,line numbe r,extende dp rice,discoun t, taxfromdel eted-ﻩ--声明变量获取查找信息declare ord erkey int,linenum be rint,extendedp ri ce r eal,discou nt real,ta xreal -—ﻩ-打开游标epoﻩen c urso r_ deleted——标游取读ﻩ读取游标efﻩetch next fr om cur sor_delete d in toorder ke y,l inenumb er,ext enddedprice, @di scoun t,taxwh ile@FETCH_STATUS=0begi n-—声明一个变量保存重新计算得新价格ﻩ declare @ne w_ to talpric erealﻩsselec t@new_t otalpr ice= @exte nde dpri ce*(1-@disco unt)*(1+ tax)-ﻩ-—用新得总价格变量更新orders 表得tot alp rice uﻩﻩupd ateorders set t otalpri ce=to talpr ice-@new _totalp rice wh er e order key= @ord erkeyfetchn ext f rom cursor_inse rt ed in to orderkey, @line numbe r,extendeeddprice, @d iscou nt,t ax dneﻩndddeal lo cat e cur sor_inse rted eend((4 4))验证 up d at e触发器—-查瞧号订单得 to ta a l pr i ceselec t*fro o mo o r ders whereorde r key=1 8 30;—-查瞧明细表得相关信息se l ect *f ro mlin ei i te e mw here or de e r key=183 0and l ine num m be e r =1;——验证 e update 触发器updat elineitem set t ax=tax+0、05whe re orderkey=1830;(二)i i n steadof触发器((1))在在 lineit em 表上定义一个ins tead o fupda te触发器, 当修改明细表中得数量量quan ti ty 时, 应先检查供应表par tsupp 得av ai lqty 就是否足够, 不足够则拒绝执行, 否则执行并修改相应数值以保证数据一致性于由于 in steadof 触发器更新某个表会使得该表上其她不满足更新列不能更新,因因用此逆向思维使用 a fter 触发器实现相同效果即先更新 qu antity, 再比较av ailqqtty, 如果满足更新数量, 就修改partsupp 得表得 a vailqty, 如果不满足, 则把lineitem得quantity 更新之后得数据重新修改回来ccreate trigge r trig_lin eit em_quanti ty_ upda teonli neit em f or upda teas begin if UPDATE(qu ant ity)bbegin ——向指别分量变标游明声ﻩ声明游标变量分别指向 i nserted 表与 d el eted 表edﻩdeclare c urso r_inser tedcur sorr ead_on lyfortcelesﻩﻩtorde rkey, partk ey,s uppkey,lin enum ber, quantit yfr om i nserteddecl arecursor_de leted c urs orrea d_ onl yf or select quantityfr om deleted-—息信找查取获量变明声ﻩ声明变量获取查找信息decl are@qu an tity _dif f_lineitem i nt,q uanti ty_pa rtsup p i nt cedﻩclare suppkey int, @par tke y in t,o rd erkey i nt,unenilﻩﻩum ber int ,qty _inserted in t , @qty_deleted int--打开游标ruc nepoﻩrsor_in sert ed poﻩopen cur sor_d eleted-—量变给赋值数标游取读ﻩ读取游标数值赋给变量fﻩfet chnext fromcu rsor_ insert edﻩiinto or de rk ey,pa rtkey, @suppk ey, @line nu mber, @qty _ins erte df et chnext fromcursor _d eletedint o q ty _de lete dwhi le fe tch_st atus=0 gebﻩegin--计算订单明细修改时, 订购数量得变化值inserte d表项-d elet ed表项ssel ect quantity_d if f_ li neit em= @q ty _in se rte d—@@q ty_deleteedﻩ--从parts upp 表获取ava ilq ty值, 注意partsupp 表得主键为(partk ey,suppkeey)tcelesﻩﻩt@quanti ty_p ar tsupp =av ailq ty fro m pa rtsu ppwﻩﻩwh er e suppkey= suppke yand part key= @par tk ey-—断判始开ﻩﻩ开始判断gebﻩbegi nfiﻩf quant ity _d iff_ lin eite m=0ﻩﻩ p rin t“ 更新得数量与原表中得值相同, 不需要更新”e ls eif @quantit y_d iff_lin eitem 〈=q uantity_partsuppﻩbe ginﻩpuﻩﻩpd ate partsupps et avail qty= availqty-@qua ntit y_d iff_li ne item ﻩpus erehwﻩppkey=suppkeyandp artkey= @par tke yﻩﻩ p rint “ 两个表都更新成功’ ﻩﻩﻩneﻩndels eigebﻩﻩinﻩuﻩﻩupdate li nei temsetquantit y=quantity+ @quanti ty_diff_linei temwhe re o rd erke y=@orde rke y and li nenu mber= @liine numberﻩp ri nt '更新失败”ﻩﻩendﻩ e nd efﻩﻩetch ne xtfr om c urso r_i nsertedi nto @ord erke y, @partkey,s upp key, @linenumb er, @qt y_ ins ert edf etch ne xt from curso r_de leted into @qt y_d elet ed dneﻩndd eallocat e cur sor _i nserte ddealloc at e cursor_de le ted eend eend(2)在在 l ineite m表上定义一个 instea d of in sert 触发器, 当插入明细表中一条记录时时, 应先检查供应表par tsupp 得得 ava il qt y就是否足够qu anti ty 得数量c rea te t rig ger tri g_lineitem_q ua nti ty_ insertonline item iinstead of inser t as bbegin-—声明游标变量指向 inserte d表d eclar e cur sor_inserte dcur sorrea d_ only f orsﻩﻩselect or derk ey,pa rtkey,sup pk ey, lin en umber,q uantityf rom ins er ted-—声明变量获取查找信息dec lare quantity int, @av ailq ty i nt, @suppkeyin t, @partkeyinntt, @o rderkey int, @linenu mber int-—标游开打ﻩ打开游标c nepoﻩcurs or_ins erted -ﻩ-—读取游标f etc hnext fro mcursor_insert edint o@orde rkey,partkey,@@ssuppkey, @linenumber,qu antity wh ile @@FETCH_S TATUS= 0igebﻩin--为变量赋值a tcelesﻩavailqtyy==av ai lqt y fr ompartsuppwﻩwhe re suppkey =@su ppk ey and part ke y= partke yﻩ if @quant ity 〈= @avail qt y-—如果可以更新bﻩbegin /ﻩﻩﻩ/*将将 insert ed 表中得记录插入到明细表*/ ﻩsniﻩserti nto l ineite m select *from i nsertedro=yekredroerehwﻩﻩrderk ey andlinenumb er = @linenumber */ﻩﻩ新更时同ﻩ*同时更新 part supp 表得数量*/ﻩﻩuupd ate pa rtsup pset a vailqty=availqty-@quanti tyﻩerehwﻩe sup pke y= @sup pkey and partkey=part key ppr int ’paarts upp 表有足够得货物可以满足 lin eitem 得quan tityy, 插入成功’endelsebeginﻩﻩ p rintt''pa rt sup p表没有足够得货物可以满足 l ineitem 得得q uantity,插入失败’dneﻩfﻩﻩfetc h next from curso r_ins ert ed in to@ord erkey, partkey, suppkey, @liinenumbe r, qu antity eﻩen ddeall ocat ecursor_ inserted end(3)在在 line ite m表上定义一个 inste ad of del ete 触发器,当当删除明细表中记录时时, 同时改变表供应表 partsupp 得ava il qtyy数值 c re ate trigge r tri g_ lin eit em_quanti ty_ del ete o n line item inste ad of del ete as be gin—-声明游标变量指向deleted 表de cla re curs or_ del eted c ursorread _only forlesﻩﻩelect or derke y, par tkey,sup pkey, linenumbe r,quan tity fr om deleted -ﻩ--声明变量decl are s upp key i nt, par tke yint, @orde rkey int,linen umb erint, @quaant it y int—-标游开打ﻩ打开游标opencursor_deleted-—标游取读ﻩ读取游标ffetch next fr omcurs or _del et edin to @ord erkey , @partkey,s uppkeey, @lin en umber,q ua ntitywhi leFFET CH_ STATUS=0 igebﻩin*/*除删ﻩ*删除*/ﻩ de let e fromlineite m where linenu mber= line number and o rde rkey =ordder key*/新更时同ﻩ同时更新 pa rt supp 表得数量*/u pdateparts uppse tavailqt y=a vai lq ty+quant ityﻩ where s uppke y= @s uppkey a nd par tk ey= @p ar tkeyﻩ p rin t’ 删除成功, 并且已经把货物数量归还到 p ar tsup p里“ fﻩﻩfetc h ne xt fr omcurso r_del etedinto @ord er ke y,p ar tkey,@@suppkey, @lin enu mber,quanti ty neﻩnd edﻩea lloc ate cursor_ delete dend(4)验证 update 触发器--查瞧li neit em 得quan tit y select*fr omlin eit em whe re or derk ey =1830and li nenum ber=1;——查询partsupp 表得ava ilqt y se lect * from part supp w here suppk ey =(selectsupp key fr omlin eitem w here ord erkey=18 30)and partk ey=(s elec t part key from lin eite mwh er eorder key =18 30 a nd linenu mber=1)---更新数量过大——更新得值与原值相同---更新到+ + 2 00 数量, , 成功updateli neitem setquant ity=q uanti ty+ 200where order key=1830and lin en umber =1;--更新 +2 00成功后l ineite m得 quanti ty y 变化——更新+200 成功后par ts upp 表得a va ilqty 变化实验到此。

实验四计数器及其应用一、实验目的l、学习用集成触发器构成计数器的方法2、掌握中规模集成计数器的使用及功能测试方法3、运用集成计数计构成l位分频器二、实验原理计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。

根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

l、用D触发器构成异步二进制加/减计数器图4-1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D 触发器接成T’触发器,再由低位触发器的Q端和高—位的CP端相连接。

图4-1 四位二进制异步加法计数器若将图4-l稍加改动,即将低位触发器的Q端与高一位的CP端相连接,即构成了一个4位二进制减法计数器。

2、中规模十进制计数器CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,具引脚排列及逻辑符号如图4-2所示。

图4-2 CC40192引脚排列及逻辑符号图中LD一置数端CP L一加计数端CP D一减计数端CO一非同步进位输出端BO一非同步借位输出端D0、D1、D2、D3一计数器输入端Q0、Q1、Q2、Q3一数据输出端CR一清除端CC40192(同74LS192,二者可互换使用)的功能如表4-1,说明如下:表4-1当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3置入计数器。

数字电子技术实验指导书电气与电子工程学院实验一门电路逻辑功能及测试一、实验目的1. 熟悉门电路逻辑功能2. 熟悉数字电路实验仪及示波器使用方法二、实验仪器及材料1. 双踪示波器2. 器件74LS00 二输入端四与非门 2片74LS20 四输入端双与非门 1片74LS86 二输入端四异或门 1 片三、实验内容1.测试门电路逻辑功能(1).选用双四输入与非门74LS20一只,插入14P锁& 紧插座上按图1.1接线、输入端接K1-K16(电平开关输出插口),输出端接电平显示发光二极管(L1-L16任意一个)(2).将电平开关按表1.1置位,分别测输出电压及逻辑状态。

表 1.1输出输出1 2 4 5 Y 电压(V)H H H HL H H HL L H HL L L HL L L L2.异或门逻辑功能测试(1).选二输入四异或门电路74LS86,按图1.2接线,输入端1、2、4、5接电平开关,输出端A、B、Y接电平显示发光二极管。

(2).将电平开关按表1.2置位拨动,将输出结果填入表中。

表 1.2输入输出A B Y Y电压L L L LH L L LH H L LH H H LH H H HL H L H3、逻辑电路的逻辑关系(1).用74LS00、按图1.3,1.4接线,将输入输出逻辑关系分别填入表1.3、表1.4中,表1.3输入输出A B YL LL HH LH H表1.4输入输出A B Y ZL LL HH LH H(2).写出上面两个电路逻辑表达式。

五、实验报告1.按各步骤要求填表并画逻辑图。

2.回答问题:(1)怎样判断门电路逻辑功能是否正常?(2)与非门一个输入接连续脉冲,其余端什么状态时允许脉冲通过?什么状态时禁止脉冲通过?(3)异或门又称可控反相门,为什么?实验二组合逻辑电路(半加器、全加器)一、实验目的1.掌握组合逻辑电路的功能测试。

2.验证半加器和全加器的逻辑功能。

3.学会二进制数的运算规律。

触发器功能测试实验报告触发器功能测试实验报告一、引言触发器是数字电路中常见的重要元件之一,其具有存储和放大信号的功能。

触发器的功能测试是电子工程师在设计和制造数字电路时必不可少的一项工作。

本实验旨在通过对不同类型的触发器进行功能测试,验证其在不同工作模式下的正确性和稳定性。

二、实验目的1. 了解触发器的基本原理和工作模式;2. 掌握触发器的功能测试方法;3. 验证不同类型触发器的工作特性。

三、实验器材和材料1. 实验板;2. 电源供应器;3. 逻辑分析仪;4. 电压表;5. 连接线。

四、实验步骤1. 准备工作:将实验板连接好电源供应器和逻辑分析仪,并确保连接正确;2. 功能测试:依次测试RS触发器、D触发器、JK触发器和T触发器的工作特性。

五、实验结果与分析1. RS触发器测试:a. 将RS触发器的S端和R端分别接入逻辑分析仪的输入端,CLK端接入逻辑分析仪的时钟信号输出端;b. 通过逻辑分析仪观察输入信号和输出信号的波形,并记录下来;c. 分析波形,验证RS触发器在不同输入情况下的工作特性。

2. D触发器测试:a. 将D触发器的D端接入逻辑分析仪的输入端,CLK端接入逻辑分析仪的时钟信号输出端;b. 通过逻辑分析仪观察输入信号和输出信号的波形,并记录下来;c. 分析波形,验证D触发器在不同输入情况下的工作特性。

3. JK触发器测试:a. 将JK触发器的J端和K端分别接入逻辑分析仪的输入端,CLK端接入逻辑分析仪的时钟信号输出端;b. 通过逻辑分析仪观察输入信号和输出信号的波形,并记录下来;c. 分析波形,验证JK触发器在不同输入情况下的工作特性。

4. T触发器测试:a. 将T触发器的T端接入逻辑分析仪的输入端,CLK端接入逻辑分析仪的时钟信号输出端;b. 通过逻辑分析仪观察输入信号和输出信号的波形,并记录下来;c. 分析波形,验证T触发器在不同输入情况下的工作特性。

六、实验结论通过对RS触发器、D触发器、JK触发器和T触发器的功能测试,我们可以得出以下结论:1. RS触发器具有存储和放大信号的功能,可以用于实现简单的存储器和时序电路;2. D触发器可以将输入信号在时钟脉冲到来时存储,并在下一个时钟脉冲到来时输出;3. JK触发器是一种带有异步清零和置位功能的触发器,可以用于实现频率分割和计数器等电路;4. T触发器是一种特殊的JK触发器,其输入端和输出端相连,可以实现频率分割和频率加倍等功能。

multisim实验四实验报告仲恺农业⼯程学院实验报告纸__⾃动化学院_(院、系)__⼯业⾃动化__专业__144_班_电⼦线路计算机仿真课程实验四:触发器及其应⽤仿真实验⼀、实验⽬的1.掌握集成JK触发器和D触发器的逻辑功能及其使⽤⽅法。

2.熟悉触发器之间相互转换的设计⽅法。

3.熟悉Multisim中逻辑分析仪的使⽤⽅法。

⼆、实验设备PC机、Multisim仿真软件。

三、实验内容1.双JK触发器74LS112逻辑功能测试(1)创建电路创建如下图所⽰电路,并设置电路参数。

图4-1 74LS112逻辑功能测试(2)仿真测试①J1和J5分别74LS112的异步复位端输⼊,J2和J4分别为J、K数据端输⼊,J3为时钟端输⼊,X1和X2指⽰74LS112的输出端Q和Q_的状态。

②异步置位和异步复位功能测试。

闭合仿真开关拨动J1为“0”、J5为“1”,其他开关⽆论为何值,则74LS112被异步置“1”,指⽰灯X1亮,X2灭。

理解异步置位的功能。

拨动J1为“1”、J5为“0”,其他开关⽆论为何值,则74LS112被异步清“0”,指⽰灯X1灭,X2灭,理解异步复位的功能。

③74LS112逻辑功能测试⾸先拨动J1和J5,设定触发器的初态。

接着,拨动J1和J5均为“1”,使74LS112处于触发器⼯作状态。

然后,拨动J2-J4,观察指⽰灯X1和X2亮灭的变化,尤其注意观察指⽰灯令亮灭变化发⽣的时刻,即J3由“1”到“0”变化的时刻,从⽽掌握下降沿触发的集成边沿JK触发器的逻辑功能。

如下图所⽰:图4-2 JK触发器逻辑功能测试设定触发器的初态为Q = 1。

将J2置1后,再将J3置1,可以观察到此时触发器状态并⽆改变。

将J3清0,观察到输出Q = 1。

同样的,将J2清0,同时将J4置1,在J3由1->0的时刻,可以观察到Q = 0。

2.JK触发器构成T触发器(1)创建电路创建如图所⽰电路,并设置电路参数。

图4-3 74LS112构成T触发器(2)仿真测试①闭合仿真开关。

福建农林大学计算机与信息学院信息工程类实验报告系:计算机系专业:计算机科学与技术年级: 07级姓名:学号:实验课程:数字电子技术基础实验室号:___田实验设备号: 9 实验时间: 2008-12-16 指导教师签字:成绩:实验四触发器R-S 、J-K、T、D一、实验目的和要求1、掌握基本RS、JK、T和D触发器的逻辑功能。

2、掌握集成触发器的功能和使用方法。

3、熟悉触发器之间相互转换的方法。

二、实验原理触发器是能够存储1位二进制码的逻辑电路,它有两个互补输出端,其输出状态不仅与输入有关,而且还与原先的输出状态有关。

触发器有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存储器件,是构成各种时序电路的最基本逻辑单元。

1、基本RS触发器图4-1为由两个与非门交叉耦合构成的基本RS触发器,它是无时钟控制低电平直接触发的触发器。

基本RS触发器具有置“0”,置“1”和保持三种功能。

通常称S为置“1”端,因为S=0时触发器被置“1”;R为置“0”端,因为R=0时触发器被置“0”。

当S=R=1时状态保持,当S=R=0时为不定状态,应当避免这种状态。

基本RS触发器的逻辑符号见图4-1(b),二输入端的边框外侧都画有小圆圈,这是因为置1与置0都是低电平有效。

基本RS触发器也可以用两个“或非门”组成,此时置位为高电平有效。

2、JK触发器在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。

本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。

引脚逻辑图如图4-2所示:图4-2 JK触发器的引脚逻辑图JK触发器的状态方程为:+1nn QnQ+=KQJ其中,J和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成“与”的关系。

Q和Q为两个互补输出端。

通常把Q=0、Q=1的状态定为触发器“0”状态;而把Q=1,Q=0定为“1”状态。

jk触发器实验报告总结及体会

一、实验介绍

本次实验是关于JK触发器的实验,JK触发器是由两个NAND门或两个NOR门构成的,可以在电路中起到存储和控制信号的作用。

二、实验步骤

1. 首先按照电路图连接电路,将电源接入电路中。

2. 使用示波器观察输入端和输出端的波形变化。

3. 通过手动调节开关,改变输入端的信号,观察输出端的响应。

三、实验结果

通过实验可以得到以下结果:

1. 当J=0,K=0时,输出保持不变。

2. 当J=0,K=1时,输出为低电平。

3. 当J=1,K=0时,输出为高电平。

4. 当J=1,K=1时,输出会翻转。

四、实验分析

通过对结果的分析可以得知:

1. 当J和K都为0时,表示保持原状态。

这是因为无论前一状态是什么,在这种情况下都不会有任何变化。

2. 当J为0而K为1时,表示清零。

这是因为当K为1时,在上升沿时会强制Q为低电平。

3. 当J为1而K为0时,表示置位。

这是因为当J为1时,在上升沿时会强制Q为高电平。

4. 当J和K都为1时,表示翻转。

这是因为当J和K都为1时,在上升沿时会将Q的状态翻转。

五、实验体会

通过本次实验,我对JK触发器有了更深入的了解。

在实验中,我不仅学习了电路的连接方法,还学习了如何使用示波器观察波形变化。

此外,我也发现了电路中一些微小的变化对于输出结果所产生的影响。

通过这次实验,我加深了对数字电路的理解,并且提高了自己动手实践的能力。

篇一:触发器及其应用实验报告学生实验报告篇二:数据库实验3 触发器报告数据库专题训练------触发器实验报告系别:计算机科学与技术班级:计11-3班姓名:黄娟娟学号:11101020324成绩:评语:指导教师签字:日期:实验二触发器一、实验环境及要求触发器是一种特殊的存储过程,不能被用户直接调用。

可以包含复杂的 sql语句。

在特定事件发生时自动触发执行,通常用于实现强制业务规则和数据完整性。

dml触发器分为两种类型:after 触发器和 instead of触发器。

通过本次实验掌握触发器的创建方法以及使用方法。

二、实验步骤及结果1) 创建一个名为tri_insert_s的触发器,测试改触发器的执行情况,并给出实验结果。

当插入的新记录中sage 的值不是18至25之间的数值时,就激活该触发器,撤销该插入操作,并给出错误提示。

use sxcjgocreate trigger tri_insert_s on safter insertasif exists (select * from insertedwheresage>=18 and sage<=25)print添加成功! elsebeginprint无法添加! rollbacktransactionendgoinsert into s values(s8,黄丽,女,26,计算机)insert into s values(s8,黄丽,女,20,计算机)select *from sgo显示如下:insert into s values(s8,黄丽,女,26,计算机)insert into s values(s8,黄丽,女,20,计算机)2)创建一个名为tri_update_sc的触发器,要求:(1)首先判断数据库中是否已经存在名为tri_update_sc的触发器,如果存在,首先删除,再创建。

(2)当试图修改sc表中的学生成绩时,给出不能随便修改成绩的信息提示。

实验四项目名称:触发器及其应用一、实验目的1、了解基本RS、JK和D触发器的逻辑功能2、了解时钟对触发器的触发作用3、能用触发器设计基本的时序逻辑电路二、实验设备1、数字电路实验箱2、74LS112 74LS00 74LS74三、实验内容及步骤1、测试基本RS触发器的逻辑功能本实验是选取74LS00芯片(引脚如图4-7所示)中两个与非门交叉耦合而成,如图4-8所示。

根据图4-8连线,d S、d R端分别接在实验箱上的逻辑电平选择开关上,输出Q和Q分别接在实验箱上的LED电平指示上。

按表4-5选择输入状态,测试并记录结果。

图4-7 74LS00引脚图图4-8 基本RS触发器表4-5d S d R Q Q011110112、JK触发器(1) 测试置位端S D和复位端R D 的功能按表4-6,将74LS112芯片(引脚如图4-9所示)的R D、S D、J、K端分别接逻辑电平选择开关,CP 接实验箱中的单脉冲下降沿触发输出端,Q、Q端分别接至实验箱的LED电平指示上。

根据表4-6,确定R D,S D、J、K端状态,按下单脉冲触发按钮,测试并记录实验结果(表中“×”表示无关项,即可置于任意状态)。

图4-9 74LS112引脚图表4-6(2) 测试JK触发器的逻辑功能按表4-7,测试JK触发器的逻辑功能。

将CP接单脉冲下降沿触发输出端,J、K、R D、S D端分别接逻辑电平选择开关,Q端接在实验箱的LED电平指示上。

利用置位端S D和复位端R D的功能,根据表4-6预置现态Q n ,然后R D 、S D 端同时置“1”,J 、K 状态按表4-7设定。

按下单脉冲触发按钮,测试并记录结果。

表4-73、D 触发器(1) 测试置位端S D 、复位端R D 的功能。

将74LS74芯片(引脚如图4-10所示)的D 、S D 、R D 端分别接逻辑电平选择开关,CP 接实验箱中的单脉冲上升沿触发端输出端,Q 、Q 分别接在实验箱的LED 电平指示上。

数字电路与逻辑设计实验

——触发器实验

姓名:李文科

学号:20131060044

学院:信息学院

专业:计算机科学与技术

指导教师:陈志坚

2014年11月22日

一、 实验目的

1. 熟悉并掌握RS 、D 、JK 触发器的构成,工作原理和功能测试方法。

2. 学会正确使用触发器集成芯片。

3. 了解不同逻辑功能触发器FF 相互转换的方法。

二、 实验仪器及材料

1. 双踪示波器

2. 器件:

74LS00 二输入端四“与非”门 1片 74LS74 双D 触发器 1片 74LS112 双JK 触发器 1片

三、 实验内容

1. 基本RS 触发器(RS-FF )功能测试

两个TTL 与非门首尾相接构成的基本RS-FF 的电路如图4.1所示。

(1) 试按下面的顺序在S d ̅̅̅、R d ̅̅̅̅端加信号:

S d ̅̅̅=0 R d ̅̅̅̅=1

S d ̅̅̅=1 R d ̅̅̅̅=1 S d ̅̅̅=1 R d ̅̅̅̅=0 S d ̅̅̅=1 R d ̅̅̅̅=1

观察并记录FF 的Q 、Q

̅端的状态,将结果填入表4.1中,并说明在上述各种输入状态下,FF 执行的是什么功能?

(2) S d ̅̅̅端接低电平,R d ̅̅̅̅端加脉冲。

Q =1, Q ̅=R d

̅̅̅̅ (3) S d ̅̅̅端接高电平,R d ̅̅̅̅端加脉冲。

Q =0,Q ̅=1 (4) 连接S d ̅̅̅、R d ̅̅̅̅,并加脉冲。

图4.1:基本RS-FF 电路

表4.1

Q= Q

̅=1 记录并观察(2)、(3)、(4)三种状态下,Q ,Q

̅,端的状态。

从中你能否总结出RS-FF 的Q 或Q ̅端的状态改变和输入端S d ̅̅̅、R d ̅̅̅̅的关系。

S d ̅̅̅=0 R d ̅̅̅̅=1 置Q=1

S d ̅̅̅=1 R d ̅̅̅̅=1 保持

S d ̅̅̅=1 R d ̅̅̅̅=0 置Q=0 (5) 当S d ̅̅̅、R d ̅̅̅̅都接低电平时,观察Q ,Q ̅端的状态。

当S d ̅̅̅、R d ̅̅̅̅同时由低电平跳为高电平时,注意观察Q ,Q ̅端的状态,重复3-5次看Q ,Q ̅端的状态是否相同,以正确理解“不定”状态的含义。

2. 维持阻塞型D-FF 功能测试

双D 型正边沿维持阻塞型触发器74LS74的逻辑符号如图4.2所示。

图中S d ̅̅̅、R d ̅̅̅̅端为异步置1端、置0端(或称异步置位复位端)。

CP 为时钟脉冲。

试按下面的步骤做实验:

(1) 分别在S d ̅̅̅、R d ̅̅̅̅端加低电平,观察并记录Q ,

Q ̅端的状态。

(2) 令S d ̅̅̅、R d ̅̅̅̅端为高电平,D 端分别加高、低电平,用单脉冲作为CP ,观察并记录当CP 为L 、↑、H 、↓时,Q 端状态的变化。

(3) 当S d ̅̅̅=R d ̅̅̅̅=H 、CP=0(或CP=1),改变D 端信号,观察Q 端的状态是否变化?

整理上述的实验数据,将结果填土表4.2中。

(4) 令S d ̅̅̅=R d ̅̅̅̅=H ,将D 和端相连,CP 加连续脉冲,用双踪示波器观察并在图4.3中记录Q 相对于CP 的波形。

图4.2:D-FF 符号 表4.2

3. 负边沿JK 触发器功能测试

双JK 负边沿触发器74LS112的逻辑符合如图4.4所示。

(1) 自拟实验步骤,测试其功能,并将结果填入表4.3中。

(2) 若令J=K=1时,CP 端加连续脉冲,用双踪示波器观察Q-CP 波

形,并记录在图4.3中。

JK-FF 这个Q-CP 波形和D-FF 的D 和Q

̅端相连时观察到的Q 端的波形相比较(即第2中的第(4)步实验结果),有何异同?

D-FF 在上升沿时翻转 JK-KK 在下降沿时翻转

4. 触发器功能转换

(1) 将D-FF 和JK-FF 分别转换成T`触发器,列出表达式,画出实验电

路图。

D-FF →T`-FF :

D :Q n+1=D

T`:Q n+1=Q ̅ ⟹ D=Q

̅ CP D-FF JK-FF

JK-FF→T`-FF :

JK :Q n+1=J Q ̅+K ̅Q T`:Q n+1=Q

̅ ⟹ J=K=1

(2) 接入连续脉冲,观察各触发器CP 及Q 端波形,比较两者关系。

四、 实验总结

D-FF 触发方式为上升沿触发,JK-FF 触发方式为下降沿触发,两者的S d ̅̅̅、

R d ̅̅̅̅均分别为清零、置1端。

CP

Q

1CP

Q

CP D-FF JK-FF。