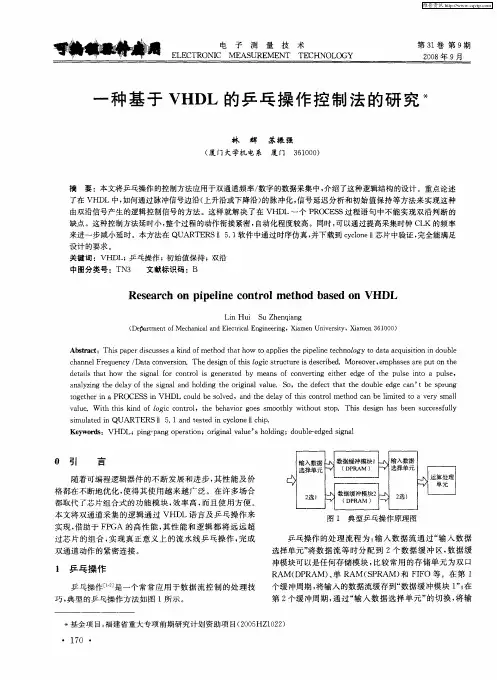

一种基于VHDL的乒乓操作控制法的研究

- 格式:pdf

- 大小:589.12 KB

- 文档页数:4

最新基于VHDL的乒乓球游戏机设计--课程设计说明书

doc

一、乒乓球游戏机简介

乒乓球游戏机是一款集休闲娱乐和智力结合于一体的游戏机,它模拟

了非常真实的乒乓球比赛,采用VHDL语言实现了游戏机本身的控制系统,用户可以通过操作杆来控制屏幕上的球拍,体验乒乓球比赛的激烈对抗。

二、课程设计目标

1.了解VHDL语言的基本原理

2.掌握系统的基本结构

3.基于VHDL语言实现乒乓球游戏机的控制系统

4.通过操作杆实现游戏控制

三、课程设计内容

1.基本原理

可编程逻辑基础:必须掌握VHDL的基本原理,以及基本的数字电路

原理,包括可编程逻辑器件,基本的逻辑门,运算器,状态机等的基本知识,能够熟练编写VHDL程序,并理解其原理。

2.基本结构

设计开发PCB:根据设计需要,设计开发PCB外型,可以实现PCB组装,板载电源,实现游戏机基本功能。

3.实现控制系统

编写VHDL程序:基于VHDL语言,实现乒乓球游戏机的控制系统,主要包括实现芯片内部部件的交互,实现模拟屏幕的更新,以及实现外设的控制,如操作杆的输入。

4.游戏控制。

大学EDA课程设计:学号:班级:专业:学院:目录0 引言............................................................................................................................. - 1 -1 设计要求..................................................................................................................... -2 -2 设计思路..................................................................................................................... - 2 -3 Verilog程序 ................................................................................................................ - 3 -4 功能仿真..................................................................................................................... - 3 -5 总结........................................................................................................................... - 11 -致...............................................................................................................................- 11 -参考文献.......................................................................................................................- 11 -基于Verilog的乒乓球游戏电路设计0 引言可编程器件的广泛应用,为数字系统的设计带来了极大的灵活性。

基于VHDL的乒乓球游戏设计与仿真乒乓球是一款经典的电子游戏,也是计算机工程师常用于设计和仿真的一个项目。

基于VHDL(Very High Speed Integrated Circuit Hardware Description Language)的乒乓球游戏设计与仿真是一个相对复杂的项目,但也是一个非常有挑战性和有趣的任务。

在开始设计和仿真乒乓球游戏之前,我们需要明确游戏的基本原理和规则。

乒乓球游戏是一个双人游戏,游戏界面通常划分为两个区域,每个区域都有一个球拍,玩家需要使用球拍将乒乓球击回对方的区域。

乒乓球可以在游戏界面的墙壁上反弹,玩家需要控制球拍的移动来接住乒乓球,以防止乒乓球碰到墙壁并反弹到自己的区域。

当乒乓球成功穿过对方区域的墙壁时,玩家得分一分。

1.乒乓球移动模块:这个模块需要确定乒乓球的初始位置和速度,并在游戏过程中控制乒乓球的移动。

可以使用VHDL语言实现一个简单的有限状态机来处理乒乓球的移动逻辑。

2.球拍移动模块:这个模块需要处理玩家对球拍的控制操作,根据玩家的输入移动球拍。

可以使用VHDL语言实现一个简单的有限状态机来处理球拍的移动逻辑。

3.碰撞检测模块:这个模块需要检测乒乓球和球拍以及墙壁之间的碰撞,根据碰撞的结果调整乒乓球的移动方向和球拍的状态。

可以使用VHDL语言实现一个简单的逻辑电路来处理碰撞检测。

4.得分计数模块:这个模块需要在乒乓球穿过对方区域的墙壁时更新玩家的得分。

可以使用VHDL语言实现一个简单的计数器来处理玩家的得分计算。

在完成以上模块的设计之后,可以使用VHDL工具对整个乒乓球游戏进行仿真。

仿真可以用来验证设计的正确性和性能,并调试任何潜在的问题。

在仿真过程中,可以模拟玩家的输入和游戏界面的变化,以验证游戏逻辑的正确性。

经过设计和仿真,可以进一步将乒乓球游戏实现到硬件平台上,例如FPGA(Field Programmable Gate Array)或ASIC(ApplicationSpecific Integrated Circuit)。

基于VHDL的乒乓球游戏机设计--课程设计说明书

一、背景介绍

游戏是世界上最受欢迎的娱乐形式之一,它能够激发人们的学习兴趣,增强他们的积极性和自信心。

此外,游戏能够让用户有趣地获得知识和乐趣,从而增进了他们的思维能力。

在促进个人发展和社会发展的同时,乒

乓球游戏也是一个有趣的游戏,游戏机可以随时随地为用户提供游戏,满

足用户的需求。

二、设计目标

本课程设计的目标在于使用VHDL设计一个基于乒乓球游戏的游戏机,游戏双方的玩家可以分别操作乒乓球机器人,以得分。

该游戏机必须具备

实时检测玩家输入的功能,当玩家输入指令时,游戏机钟能够及时响应,

从而实现玩家的要求,从而达到实现游戏功能的目的。

三、VHDL设计内容

1.乒乓球机器人控制系统:此系统使用VHDL编程,对乒乓球机器人

的运动进行控制,控制机器人的移动方向、速度等,使乒乓球机器人能够

按照玩家的输入运动。

2.控制芯片:主控芯片采用VHDL语言编程,实现控制乒乓球机器人

的运动方向和速度的控制,使乒乓球机器人按照玩家的输入运动,从而实

现游戏机功能的实现。

基于VHDL的乒乓球设计乒乓球是一种非常受欢迎的体育项目,可以单独进行,也可以进行团体比赛。

这篇文章将介绍使用VHDL(VHSIC硬件描述语言)设计一个基于FPGA(可编程逻辑器件)的乒乓球游戏。

在设计之前,我们需要了解游戏的基本规则和要求。

乒乓球游戏是一个简单的游戏,需要两个玩家和一个球。

游戏开始时,球从一个玩家开始发球,并通过轮流击球来继续游戏。

每个玩家需要使用球拍击打球,并试图将球打过对方的网,并使对方无法接到球。

如果一方无法接到球,则对手得分,并且游戏继续进行,直到达到一定分数或者决定胜负。

在设计中,我们需要考虑以下几个方面:1.游戏界面:我们需要设计一个显示器来显示游戏界面,包括玩家1和玩家2的得分、游戏中间的网、以及球的位置。

我们可以使用FPGA内部的RAM来存储得分,并使用VHDL代码来控制显示器的显示。

2.玩家控制:每个玩家需要使用一个球拍来击打球。

我们可以设计两个按钮来控制球拍的上下移动,通过读取按钮的状态来实现控制。

3.球的移动:球需要在游戏界面中移动,并与球拍和网进行碰撞。

我们可以使用VHDL代码来控制球的移动,检测碰撞,并确定球的反弹方向。

4.得分系统:当球无法被对方接到时,对手将得分。

我们可以设计一个计数器来记录每个玩家的得分,并在达到一定分数时决定胜负。

基于上述要求,我们可以开始设计基于VHDL的乒乓球游戏。

首先,我们需要确定FPGA的架构,包括使用的逻辑单元、存储单元和输入/输出接口。

然后,我们可以使用VHDL编写对应的模块,包括游戏界面显示、玩家控制、球的移动和得分系统。

对于游戏界面的显示,我们可以使用两个数码管来显示玩家1和玩家2的得分,并使用一块LCD屏幕来显示游戏界面。

在VHDL代码中,我们可以使用RAM来存储得分,并使用计数器来更新得分。

然后,我们可以使用VHDL代码来控制LCD屏幕的显示,包括绘制游戏界面和更新球的位置。

对于玩家控制,我们可以使用两个按钮来控制球拍的移动。

基于VHDL的乒乓球游戏机设计乒乓球游戏机是一种基于硬件设计的电子游戏机,它模拟了乒乓球比赛的规则和玩法。

本文将介绍一个基于VHDL(Very High Speed Integrated Circuit Hardware Description Language)的乒乓球游戏机设计。

首先,我们需要确定游戏机的硬件组成和功能。

一个基本的乒乓球游戏机包括以下组件:1.显示屏:用于显示游戏画面和分数。

2.键盘:用于输入玩家控制信号,例如乒乓球拍的移动方向和发球。

3.乒乓球拍:控制球的移动方向。

4.乒乓球:游戏的主要元素,通过球拍反弹到对手的场地。

5.游戏逻辑控制:用于判断球拍和球的移动逻辑,以及计分和游戏结束的判定。

在VHDL中,我们可以将这些组件抽象为各种信号和实体(entity)。

下面是一个乒乓球游戏机的VHDL设计示例:```vhdl--乒乓球游戏机VHDL设计entity PongGame isportclk : in std_logic; -- 时钟信号reset : in std_logic; -- 复位信号ball_x : out std_logic_vector(7 downto 0); -- 球的X坐标ball_y : out std_logic_vector(7 downto 0); -- 球的Y坐标paddle_left_y : in std_logic_vector(7 downto 0); -- 左边乒乓球拍的Y坐标paddle_right_y : in std_logic_vector(7 downto 0); -- 右边乒乓球拍的Y坐标score_left : out std_logic_vector(7 downto 0); -- 左边玩家的分数score_right : out std_logic_vector(7 downto 0) -- 右边玩家的分数end entity PongGame;architecture rtl of PongGame is--在这里定义各种信号和内部变量begin--在这里编写游戏逻辑和硬件连接end architecture rtl;```在architecture部分,我们可以编写游戏逻辑和硬件连接的代码。

基于VHDL的乒乓球游戏设计与仿真乒乓球是一种受欢迎的体育项目,也是一种常见的电子游戏。

在这个项目中,我们将使用VHDL(Very High Speed Integrated Circuit Hardware Description Language)来设计和仿真一个基于FPGA(Field Programmable Gate Array)的乒乓球游戏。

首先,我们需要确定游戏的功能和特性。

乒乓球游戏包括两个玩家,每个玩家控制一个球拍,目标是在不让球通过自己的一侧的情况下将球打过对方。

游戏区域可以通过显示器来实现,并且需要考虑到球和球拍的移动、碰撞和得分计算等功能。

接下来,我们将通过VHDL来实现这个游戏。

首先,我们需要定义并设计游戏区域的尺寸。

可以使用一个框架来表示球拍、球和边界。

然后,我们需要定义球拍和球的移动方式,以及碰撞检测功能。

游戏的得分计算可以通过计算球与边界的碰撞实现,并根据球在球拍上的碰撞情况来更新得分。

在VHDL中,我们可以使用状态机来实现游戏的不同功能。

状态机是一种有限状态机,在每一个时钟周期中会根据当前状态和输入信号确定下一个状态和输出信号。

我们可以根据不同的游戏功能来定义不同的状态和输入信号,并根据需要修改输出信号。

完成VHDL设计后,我们需要进行仿真以测试设计的正确性和性能。

我们可以使用模拟器来进行仿真,并根据不同的输入信号来观察输出信号的变化。

通过仿真,我们可以检测到可能存在的错误和问题,并进行修复和优化。

最后,我们将设计的VHDL代码烧录到FPGA芯片中,并将显示器和输入设备连接到FPGA上。

这样,我们就可以在显示器上实时显示游戏区域,并通过输入设备来控制球拍的移动。

通过这种方式,我们可以在FPGA上实现一个乒乓球游戏,使其成为一个真正的电子游戏。

总结来说,通过VHDL,我们可以很容易地设计和仿真一个乒乓球游戏。

通过合适的状态机定义和输入输出信号,我们可以实现游戏的各种功能和特性。

基于VHDL的乒乓球设计乒乓球是一项经典的球类运动,以其快速的反应和激烈的比赛而闻名。

在本篇文章中,我们将介绍一个基于VHDL的乒乓球设计。

首先,让我们来了解一下乒乓球的基本规则和游戏原理。

乒乓球比赛中有两个选手,分别位于乒乓球桌的两端。

他们需要使用乒乓球拍击乒乓球并将其反弹到对手的一侧。

游戏的目标是使对手无法返回乒乓球,从而获得分数。

在我们的设计中,我们将使用VHDL编程语言来实现乒乓球游戏的模拟。

VHDL是一种硬件描述语言,用于描述和设计数字电路。

通过使用VHDL,我们可以描述乒乓球游戏的各个组件和它们之间的交互。

首先,我们需要定义乒乓球桌和乒乓球拍的尺寸和位置。

我们可以使用VHDL的变量和常数来表示这些参数。

例如,我们可以定义一个表示乒乓球桌宽度的变量为“table_width”,并将其值设置为固定的像素数。

接下来,我们需要定义乒乓球的轨迹和速度。

由于乒乓球在游戏中会以不同的速度移动,我们可以使用一个变量来表示乒乓球的速度,并使用另一个变量来表示它的位置。

通过使用这些变量,我们可以模拟乒乓球在桌面上的移动。

然后,我们需要模拟乒乓球拍的移动和反弹。

在游戏中,玩家可以使用乒乓球拍将乒乓球击中,并改变乒乓球的方向。

我们可以通过使用VHDL设计一个乒乓球拍的模块来实现这一功能。

该模块可以接收来自玩家的输入信号,并根据玩家的操作来改变乒乓球的方向。

最后,我们需要设计一个计分系统来跟踪每个选手的得分。

我们可以使用VHDL的计数器来实现这一功能。

计数器可以根据乒乓球的位置和移动方向来自动计算得分。

综上所述,基于VHDL的乒乓球设计主要涉及乒乓球桌、乒乓球、乒乓球拍和计分系统的模拟。

通过使用VHDL,我们可以实现乒乓球游戏的各个组件并描述它们之间的交互。

这个设计可以帮助我们更好地理解乒乓球游戏的原理,并可以作为一个有趣的项目来应用VHDL编程的知识。

在实施这个设计时,可以将VHDL代码烧录在FPGA芯片上,并将其与显示屏等外设连接起来,以实现实时的乒乓球游戏体验。

基于VHDL的乒乓球游戏机的设计与实现2348292基于VHDL的乒乓球游戏机的设计与实现摘要:本文介绍了乒乓球游戏机的设计,并进行了程序仿真,实现一个乒乓球游戏机的规定功能。

设计的乒乓球游戏机能够正确判断与显示乒乓球的位置,并能自动裁判和记分的装置,可应用于实际的乒乓球游戏比赛中。

程序通过调试运行,实现了设计目标。

本论文对系统的功能设计、实现流程及正确使用都做了详细的描述。

系统开发平台为MAX+PLUSII,程序设计语言为VHDL。

关键词:乒乓球游戏机;设计;实现;VHDL;MAX+PLUSⅡ;Design and realization of table tennis game playerAbstract:This article introduces the design of the table tennis game player, and carried out simulation procedures, implementation of the provisions of a table tennis game features. Designed to be able to correctly judge the table tennis game table and display the location, and can automatically appear and scoring devices, can be applied to the actual game of Table Tennis Game. Procedure debugging operations, implementation of the design objectives. This thesis describes in detail the function of the system design, implementation and proper use of flow are described in detail to do. System development platform for the MAX + PLUSII, programming language for VHDL..Keywords:table tennis game player; design; realization; VHDL; MAX + PLUS Ⅱ目录1 引言 (1)1.1 课题设计的目的 (1)1.2 课题设计的内容 (2)2 EDA、VHDA简介 (3)2.1 EDA的发展概况 (3)2.2 硬件描述语言---VHDL (3)3 乒乓球游戏机设计过程 (5)3.1设计规划 (5)3.2乒乓球实体的设计 (6)3.3 状态机编程实现 (7)3.4 记分译器的设计 (10)3.5 构造体的设计 (12)4 系统仿真 (14)4.1系统编译 (14)4.2系统有关波形的仿真 (14)结束语 (17)致谢 (18)参考文献 (19)附录 (20)《乒乓球游戏机的设计与实现》第 1 页共 30 页1 引言08年奥运,在电视机前欢腾了半个晚上。

最新基于VHDL课程设计乒乓球游戏

主要内容有:

一、引言

乒乓球游戏是一款常见的电子娱乐游戏,通过控制乒乓球板上的乒乓球可以获得不同的游戏效果。

本文以VHDL课程设计为基础,设计并实现了一款乒乓球游戏,实现了乒乓球的运动,并设计了界面以及积分系统,使得用户能够享受到不同的娱乐效果。

二、游戏功能及实现

(1)游戏界面设计

游戏界面由显示器提供,由竖直条以及水平条构成,其中竖直条为乒乓球的运动路径,水平条为乒乓球的控制条,以及上方的计分区。

(2)乒乓球运动

乒乓球运动由FPGA板按照用户的操作进行控制,采用VHDL语言编写控制代码,通过MyHDL模块将VHDL程序转换为可烧写的FPGA文件,实现乒乓球在显示器上的运动。

(3)积分系统

积分系统由LED灯圈模块提供,通过FPGA板进行数据的控制,乒乓球每落入一个洞,积分就会+1,当分数达到20分时,游戏结束。

三、设计评估

通过本次课程设计,我们用FPGA板搭建了乒乓球的电子游戏,对VHDL语言认识有了更深入的了解,同时,也锻炼了实践能力,增长了

FPGA设计经验。

而此次游戏设计的完成,也得到了良好的游戏效果,给用户带来了不同的娱乐体验。

四、结论。

最新基于VHDL课程设计乒乓球游戏乒乓球游戏是一款经典的电子游戏,也是很多学习VHDL的学生们所选择的课程设计主题之一、下面是一个最新基于VHDL的乒乓球游戏设计,详细介绍了其实现过程和功能。

设计概述:这个乒乓球游戏是基于VHDL语言设计的。

在这个设计中,我们将使用基本的VHDL模块来实现游戏中的各个功能,包括球的运动、板子的移动和得分计算等。

设计步骤:以下是设计乒乓球游戏的步骤:1.定义游戏界面:首先,我们需要定义游戏界面。

在这个设计中,我们将使用一个矩形框来表示整个游戏区域,包括球和板子的位置。

我们可以使用矩形框的坐标来确定球和板子的位置。

2.实现球的运动:接下来,我们需要实现球的运动。

我们可以使用一个计数器来控制球的速度和方向。

通过不断改变球的坐标,我们可以实现球的运动效果。

3.移动板子:我们还需要实现板子的移动功能。

我们可以使用按键或者鼠标来控制板子的位置。

通过改变板子的坐标,我们可以实现板子的移动效果。

4.碰撞检测:在乒乓球游戏中,当球碰到边界或者板子时,需要进行碰撞检测。

我们可以使用一个碰撞检测模块来判断球是否与边界或者板子发生碰撞,并根据不同的情况处理碰撞的效果。

5.得分计算:最后,我们需要实现得分计算功能。

当球与板子发生碰撞时,玩家得一分。

我们可以使用一个计分模块来统计得分,并在界面上显示。

实现细节:以下是乒乓球游戏设计的一些具体细节:1.游戏界面使用一个矩形框表示。

可以使用VHDL语言中的图形库来实现矩形框的绘制和显示。

2.实现球的运动可以使用一个计数器来控制。

根据不同的计数值,改变球的坐标,从而实现运动效果。

3.移动板子可以通过输入设备来实现。

可以使用VHDL语言中的输入模块来读取输入设备的状态,并根据不同的输入状态改变板子的坐标。

4.碰撞检测可以使用一个碰撞检测模块来实现。

该模块可以判断球与边界或者板子之间的碰撞,并根据碰撞情况改变球的运动方向和速度。

5.得分计算可以使用一个计分模块来实现。

基于VHDL的乒乓球游戏机设计--课程设计说明书课程设计说明书,基于VHDL的乒乓球游戏机设计1.引言本课程设计旨在通过使用VHDL(VHSIC Hardware Description Language)语言设计一个乒乓球游戏机,来帮助学生理解数字逻辑电路设计原理,并提高其在VHDL编程方面的能力。

乒乓球游戏机是一款经典的游戏,可以通过键盘控制两个玩家分别控制“球拍”进行游戏。

2.设计目标设计一个基于VHDL的乒乓球游戏机,具体要求如下:-采用VHDL语言进行设计和实现游戏机的硬件逻辑电路;-游戏机具有两个可控的玩家“球拍”,玩家通过键盘控制球拍;-游戏机有一个移动的“球”,玩家需要控制球拍以防止球离开游戏界面;-当球没有被接住时,游戏结束;-游戏机需要显示当前游戏得分;3.系统框图设计游戏机系统框图设计如下:```------------Keyboar-----------------------------------------------------Mai--------------------------------------------------------------------------------------Player 1 (Keyboard Control) ,, Player---------------------------------------------------VG------```4.系统模块设计本设计将由以下几个模块组成:- Keyboard模块:负责接收键盘输入,并将输入信号转换为玩家控制信号;- Main模块:负责整体的游戏逻辑,包括球和球拍的移动、得分的计算、游戏的判定等;- Player 1和Player 2模块:负责控制球拍的移动;-VGA模块:用于显示游戏界面和得分信息;5.实验步骤-确定游戏机的功能要求和硬件设计规格;-根据系统框图,设计每个模块的功能和接口;-使用VHDL语言编写每个模块的代码,并进行仿真和测试;-将各个模块进行综合,并生成比特流;-进行游戏机的调试和优化,确保其正常工作;6.课程设计要求-学生能够理解和掌握VHDL语言的基本语法和常用逻辑电路的设计原理;-学生能够根据需求设计出乒乓球游戏机的硬件逻辑电路,并使用VHDL语言实现;-学生能够使用VHDL仿真工具进行仿真和调试;-学生能够进行设计方案的调试和优化,并确保游戏机的正常运行;7.结束语。

基于VHDL的乒乓球游戏机的设计毕业设计摘要:本论文设计了一款基于VHDL的乒乓球游戏机,通过FPGA实现了游戏的核心逻辑和显示控制等功能。

论文首先介绍了游戏机的背景和研究意义,然后详细描述了游戏机的硬件设计和VHDL代码实现。

接着对游戏机进行功能测试和性能评估,结果表明游戏机能够流畅运行,并且具有良好的游戏体验。

最后,本文总结了设计过程中的经验教训,并对未来的改进方向进行了展望。

1.引言乒乓球游戏作为一种经典的游戏方式,深受大众喜爱。

本论文旨在设计一款基于VHDL的乒乓球游戏机,通过FPGA实现游戏的核心逻辑和显示控制等功能。

此游戏机可为玩家提供乒乓球对战的快感和挑战,同时也具备一定的娱乐价值。

2.游戏机硬件设计2.1总体设计思路本游戏机采用FPGA作为核心芯片,将乒乓球游戏的核心逻辑、显示控制等功能实现在FPGA上。

游戏机配备了合适的输入设备和输出设备,提供给玩家操作和显示。

2.2输入设备设计游戏机的输入设备采用了按键和手柄两种方式。

通过按键控制乒乓球的挡板移动,通过手柄控制乒乓球的上下移动。

2.3输出设备设计游戏机的输出设备采用了液晶显示屏和音响。

液晶显示屏用于显示游戏界面和提示信息,音响用于播放游戏音效和背景音乐。

3.VHDL代码实现3.1游戏核心逻辑设计游戏核心逻辑主要包括乒乓球的轨迹计算和碰撞判断等功能。

根据输入设备的操作,通过VHDL代码实现乒乓球的移动和碰撞检测等功能。

3.2显示控制设计游戏的显示控制主要包括游戏界面的绘制和显示更新等功能。

通过VHDL代码实现游戏界面的绘制和按需更新显示。

4.功能测试和性能评估通过将游戏机连接到计算机进行测试和评估,结果表明游戏机能够流畅运行,并且具有良好的游戏体验。

游戏机的输入和输出设备响应迅速,能够准确捕捉玩家的操作。

5.结论本论文设计了一款基于VHDL的乒乓球游戏机,通过FPGA实现了游戏的核心逻辑和显示控制等功能。

经过测试和评估,游戏机具备流畅运行和良好游戏体验的特点。