时序逻辑电路-数字电子技术

- 格式:ppt

- 大小:1021.00 KB

- 文档页数:2

数电知识点总结数电(数位电子)是一门研究数字电子技术的学科,涉及到数字电路、数字信号处理、数字系统等多个方面的知识。

数字电子技术已经成为现代电子工程技术的基础,并且在通信、计算机、控制、显示、测量等领域都有广泛的应用。

本文将从数字电路、数字信号处理和数字系统三个方面对数电的知识点进行总结。

1. 数字电路数字电路是将数字信号作为输入、输出,通过逻辑门、存储器等数字元器件完成逻辑运算和信息处理的电路。

数字电路是实现数字逻辑功能的基本组成单元,包括组合逻辑电路和时序逻辑电路两种类型。

1.1 组合逻辑电路组合逻辑电路是由若干逻辑门进行组合而成的电路,其输出仅取决于当前输入的组合,不受到电路内过去的状态的影响。

组合逻辑电路主要包括门电路(与门、或门、非门等)、编码器、译码器、多路选择器、加法器、减法器等。

常用的集成逻辑门有 TTL、CMOS、ECL、IIL 四种族类。

常见的集成逻辑门有 TTL、 CMOS、 ECL、 IIL 四种。

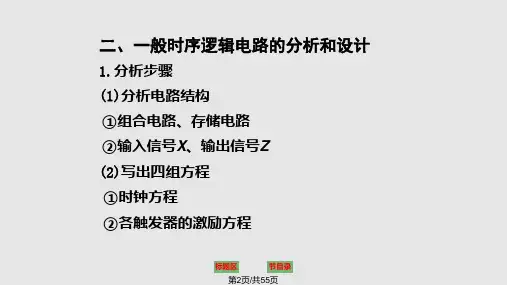

1.2 时序逻辑电路时序逻辑电路是组合电路与触发器相结合,结构复杂。

时序逻辑电路主要包括触发器、寄存器、计数器、移位寄存器等。

在传统的 TTL 集成电路中,触发器主要有 RS 触发器、 JK触发器、 D 触发器和 T 触发器四种。

在 CMOS 集成电路中一般用 T 触发器,D 触发器和 JK 触发器等。

2. 数字信号处理数字信号处理(DSP)是利用数字计算机或数字信号处理器对连续时间的信号进行数字化处理,包括信号的采样、量化和编码、数字滤波、谱分析、数字频率合成等基本处理方法。

数字信号处理已广泛应用于通信、音频、视频、雷达、医学影像等领域。

2.1 信号采样和量化信号采样是将连续时间信号转换为离散时间信号的过程,采样频率必须高于信号频率的两倍才能保证信号的完全重构。

信号量化是将采样得到的连续幅度信号转换为一个有限数目的离散的幅度值的过程,量化误差会引入信号失真。

2.2 数字滤波数字滤波是利用数字计算机对数字信号进行特定频率成分的增益或者衰减的处理过程。

数字电子技术(第5版)第6章时序逻辑电路1.(334)利用()可以把集成计数器设计成初态不为零的计数器。

答案.反馈置数法2.(318)时序逻辑电路由( ) 和( ) 两部分组成。

答案.组合电路存储电路3.(337)一个4位的扭环形计数器有()个状态。

答案. 84.(335)集成计数器的级联方式有()和()两种方式。

答案.异步同步5.(333)利用()和()可以改变集成计数器的计数长度。

答案.反馈归零法反馈置数法6.(332)一个模为24的计数器,能够记录到的最大计数值是()。

答案. 237.(331)计数器的模表示计数器的()计数长度。

答案.最大8.(329)构成时序电路的各触发器的时钟输入端都接在一起,这种时序电路称为()。

答案.同步时序电路9.(328)时序电路的输出不仅与电路的()有关,还与电路的()有关。

答案.现态输入信号10.(327)摩尔型时序电路的输出仅由电路的()决定,而与电路的( ) 无关。

(注:教材中没有讲述摩尔型电路的概念,故删去此题)答案.现态输入信号11.(326) 时序逻辑电路的功能描述有 ( ) 、 ( ) 、 ( ) 、 ( ) 。

答案. 逻辑方程式 状态表 状态图 时序图12.(330) 异步时序电路中的各触发器的状态转换 ( )同一时刻进行的。

答案. 不是在13.(336) 一个4位的环形计数器有( )个状态。

答案. 414.(325) 时序逻辑电路可分为 ( ) 和 ( ) 两大类。

答案. 同步时序电路 异步时序电路15.(354) 分析如图7307所示电路,说明其功能。

图7307输 入输 出CR LD T CT P CT CP 3D 2D 1D 0D 3Q 2Q 1Q 0QCO0 × × × × × × × × 000 10××↑3d 2d 1d 0d 3d 2d 1d 0d1111↑×××× 计数 110×××××× 保持 11××××××保持答案. 经分析知,采用了74LS160的同步置数功能。

电气工程师-专业基础(供配电)-数字电子技术-3.6时序逻辑电路[单选题]1.采用中规模加法计数器74LS161构成的计数器电路如图3-6-1所示,该电路的进制为()。

[2017年真(江南博哥)题]图3-6-1A.十一进制B.十二进制C.八进制D.七进制正确答案:B参考解析:74LS161为集成计数器,利用其异步清零功能(即CR=0时置零)实现十二进制计数功能,主循环过程如图3-6-2所示。

图3-6-2由图3-6-2可知,74LS161从0000状态(置零状态)开始计数,当输入第12个CP脉冲(上升沿)时,输出Q D Q C Q B Q A=1100,,此时异步清零低电平动作,计数器返回0000状态重新开始计数,因此为十二位进制计数器。

[单选题]2.如图3-6-3所示异步时序电路,该电路的逻辑功能为()。

[2018年真题]图3-6-3A.八进制加法计数器B.八进制减法计数器C.五进制加法计数器D.五进制减法计数器正确答案:C参考解析:JK触发器的特征方程为:可知:故可列真值表如表3-6-1。

由真值表可知,此电路完成了5种状态的循环转换,为五进制加法计数器。

表3-6-1[单选题]3.图3-6-4所示电路中,对于A、B、和D的波形,触发器FF0和FF1输出端Q0、Q1的波形是()。

[2018年真题]图3-6-4 A.B.C.D.正确答案:B参考解析:D触发器的特征方程为:Q n+1=D,则Q0np>=D,由A脉冲的上升沿触发。

JK触发器的特征方程为:则由B脉冲的下降沿触发,即为B项。

[单选题]4.图示3-6-5电路的逻辑功能为()。

[2014年真题]图3-6-5A.异步8进制计数器B.异步7进制计数器C.异步6进制计数器D.异步5进制计数器正确答案:D参考解析:解题步骤如下:①分析电路组成。

该电路是由三个下降沿触发的JK触发器组成的电路。

由于触发器1的时钟信号为触发器0的输出,故为异步时序逻辑电路。

第六章时序逻辑电路(选择、判断共30题)一、选择题1.同步计数器和异步计数器比较,同步计数器的显著优点是。

A.工作速度高B.触发器利用率高C.电路简单D.不受时钟C P控制。

2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。

A.4B.5C.9D.203.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器B.加法器C.数码寄存器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为的计数器。

A.NB.2NC.N2D.2N5.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N6.五个D触发器构成环形计数器,其计数长度为。

A.5B.10C.25D.327.同步时序电路和异步时序电路比较,其差异在于后者。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关8.一位8421B C D码计数器至少需要个触发器。

A.3B.4C.5D.109.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用级触发器。

A.2B.3C.4D.810.8位移位寄存器,串行输入时经个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.811.用二进制异步计数器从0做加法,计到十进制数178,则最少需要个触发器。

A.2B.6C.7D.8E.1012.某电视机水平-垂直扫描发生器需要一个分频器将31500H Z的脉冲转换为60H Z的脉冲,欲构成此分频器至少需要个触发器。

A.10B.60C.525D.3150013.某移位寄存器的时钟脉冲频率为100K H Z ,欲将存放在该寄存器中的数左移8位,完成该操作需要时间。

A.10μSB.80μSC.100μSD.800m s 14.若用J K 触发器来实现特性方程为,则J K 端的方程为 。

AB Q A Q n 1n +=+A.J =A B ,K = B.J =A B ,K = C.J =,K =A B D.J =,K =A B B A +B A B A +B A 15.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需要 片。