8 位串入、并出移位寄存器

1. 概述

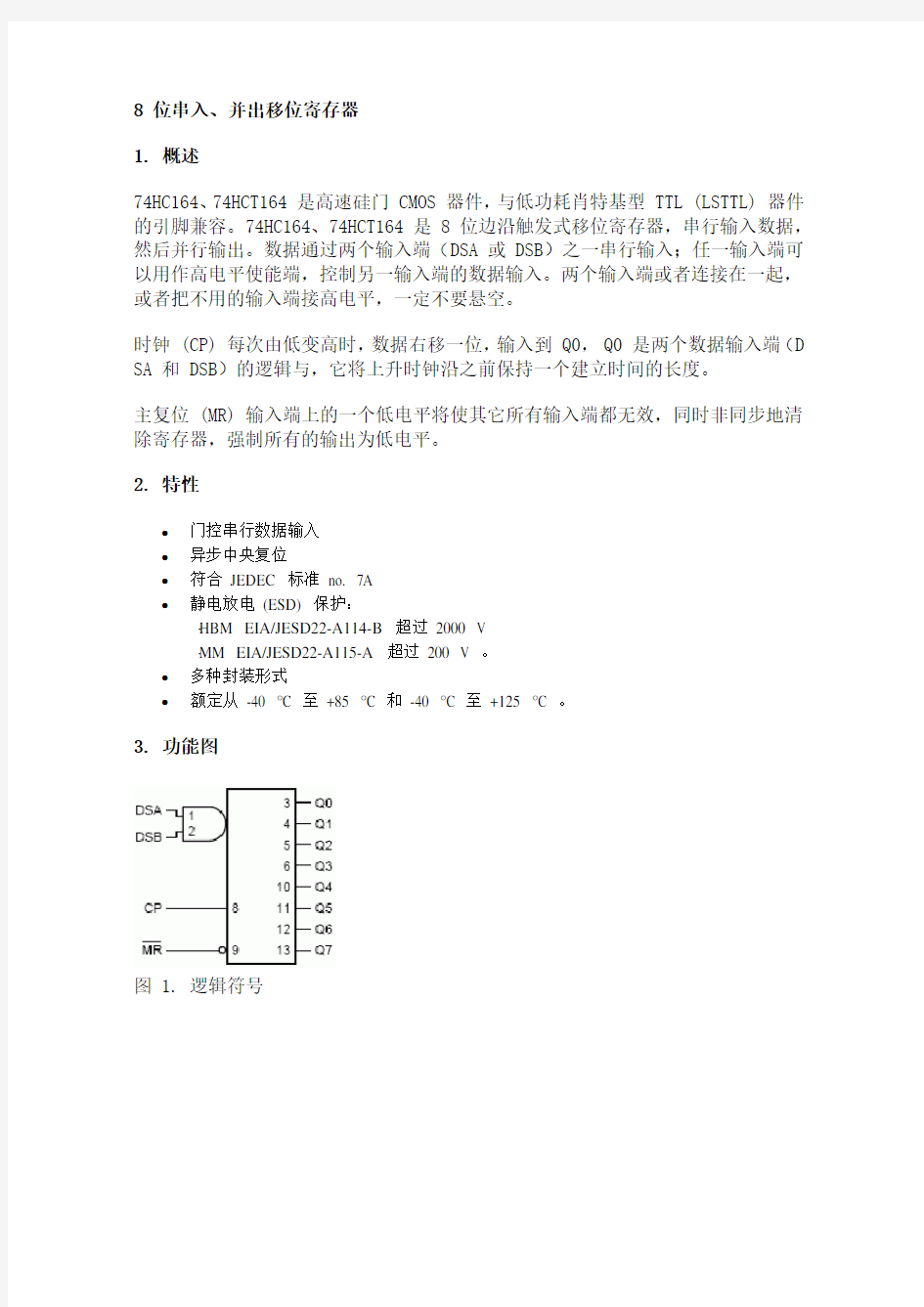

74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(D SA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性

?门控串行数据输入

?异步中央复位

?符合JEDEC 标准no. 7A

?静电放电(ESD) 保护:

·HBM EIA/JESD22-A114-B 超过2000 V

·MM EIA/JESD22-A115-A 超过200 V 。

?多种封装形式

?额定从-40 °C 至+85 °C 和-40 °C 至+125 °C 。

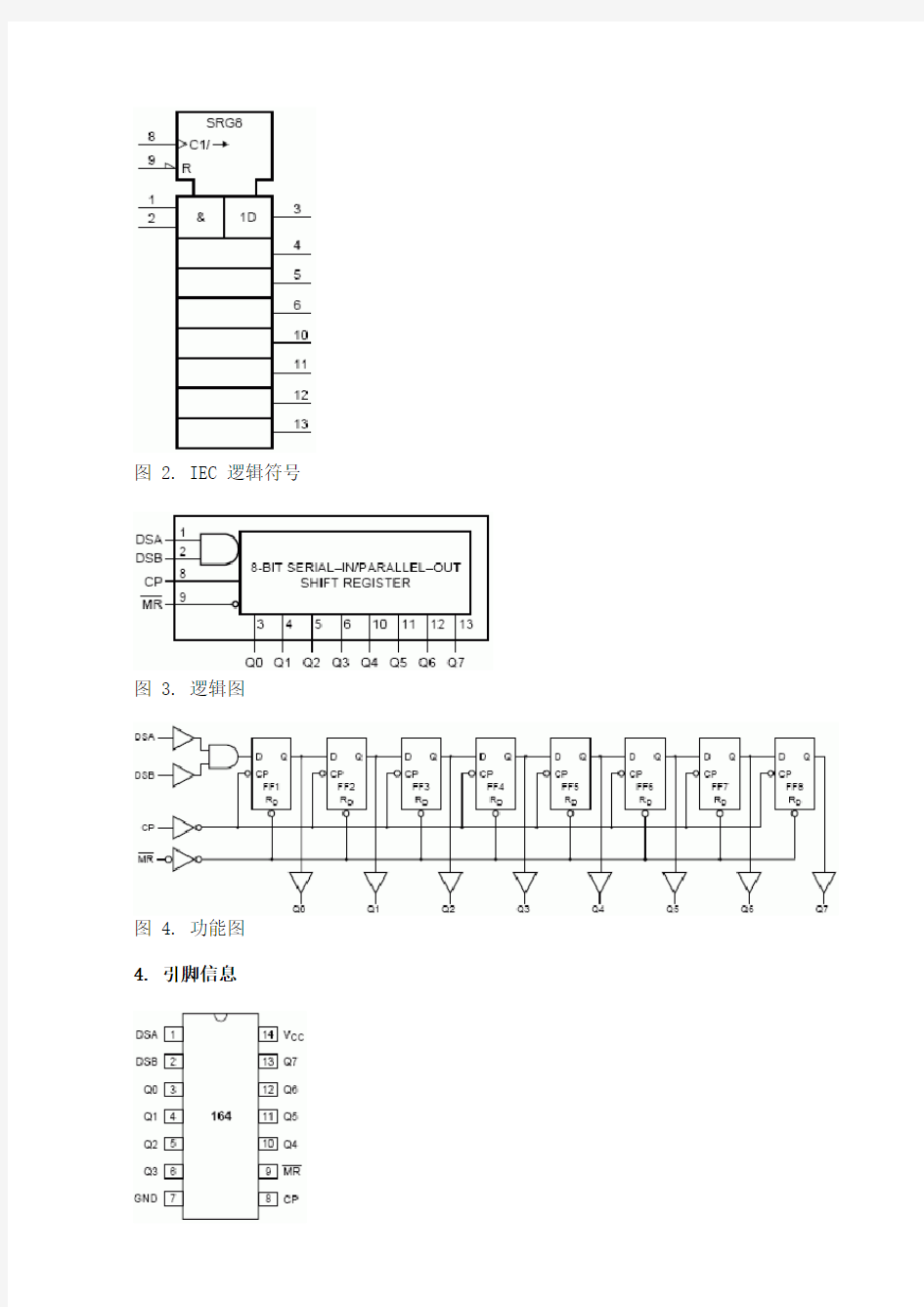

3. 功能图

图 1. 逻辑符号

图 2. IEC 逻辑符号

图 3. 逻辑图

图 4. 功能图

4. 引脚信息

图 5. DIP14、SO14、SSOP14 和 TSSOP14 封装的引脚配置

引脚说明

74HC164中文资料(功能,真值表,引脚图及电气参数介绍)

SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。一个高电平输入后就使另一个输入端赋能,这个输入就决定了第一个触发器的状态。虽然不管时钟处于高电平或低电平时,串行输入端的数据都可以被改变,但只有满足建立条件的信息才能被输入。时钟控制发生在时钟输入由低电平到高电平的跃变上。为了减小传输线效应,所有输入端均采用二极管钳位。

https://www.doczj.com/doc/234121722.html,/info/cmos/0083928.html

H=高电平(稳定态)L=低电平(稳定态)×=不定↑=从低电平转换到高电平

QA0…QH0=在稳定态输入条件建立前QA…QH 的相应电平

QAn…QHn=在最近的时钟输入条件(↑)建立前QA…QH 的相应电平,表示移位一位

74HC164典型工作时序图

我之前写的164扩展程序,参考一下吧!应该可以解决你问题。

其实你只要用到一片164就够了,作动态扫描,下面程序是两个数码管动态扫描,164并行输出口再接一片功率驱动芯片,如TD62083。

程序如下:

/**************************************/

/* 74LS164数码管动态显示*/

/**************************************/

//-------------------------------------库函数声明,管脚定义------------

#include

#define uchar unsigned char

sbit simuseri_CLK=P1^1; //用P1^1模拟串口时钟

sbit simuseri_DATA=P1^0; //用P1^0模拟串口数据

sbit a0=ACC^0;

unsigned char code dis_code[11]={0x28,0x7E,0xa2,0x62, //查表显示0, 1、、9 0x74,0x61,0x21,0x7A,0x20,0x60, 0x01};

uchar numer,temp;

uchar ge,shi;

//----------------------------------------------------------------------------

// 函数名称:out_simuseri

// 输入参数:data_buf

// 输出参数:无

// 功能说明:8位同步移位寄存器,将data_buf的数据逐位输出到simuseri_DATA //----------------------------------------------------------------------------

void out_simuseri(uchar data_buf)

{

uchar i;

i=8;

ACC=data_buf;

do

{

simuseri_CLK=0;

simuseri_DATA=a0;

simuseri_CLK=1;

ACC=ACC>>1;

}

while(--i!=0);

}

/************************************/

void delay(uchar ms) //延时程序

{

uchar i;

while(ms--)

{

for (i=0;i<125;i++);

}}

/***********************************/

void main()

{

uchar m;

while(1)

{

for(temp=0;temp<99;temp++)

{

ge=temp/10;

shi=temp%10;

for(m=0;m<20;m++) //显示频率200ms加1次

{

P2_0=0; //位段码

numer=dis_code[ge];

out_simuseri(numer); //个位移位显示

delay(5);

P2_0=1;

P2_1=0;

numer=dis_code[shi]; //十位移位

out_simuseri(numer);

delay(5);

P2_1=1;

}

m=0;

}

}

}

/****************************************/ ………………………………………………………………………………………………************************************************************************

74hc164可以用作LED数码管的驱动的c程序

74HC164是个移位寄存器,以下程序是我用过的,绝对没问题:

其中ShowData为164数据脚,ShowClck为164时钟脚;

void Show_164(unsigned char _ShowValue)

{

unsigned char Count0;

for(Count0=0;Count0<=7;Count0++)

{

if((_ShowValue&0x80)==0x80)

ShowData=1;

else

ShowData=0;

_ShowValue<<=1;

ShowClck=0;

_nop_();

_nop_();

ShowClck=1;

}

} xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

另一个C程序;

74HC164是个移位寄存器,以下程序是我用过的,绝对没问题:

其中ShowData为164数据脚,ShowClck为164时钟脚;

void Show_164(unsigned char _ShowValue)

{

unsigned char Count0;

for(Count0=0;Count0<=7;Count0++)

{

if((_ShowValue&0x80)==0x80)

ShowData=1;

else

ShowData=0;

_ShowValue<<=1;

ShowClck=0;

_nop_();

_nop_();

ShowClck=1;

}

} Xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

实验四 一、实验名称 32位并进/并出移位寄存器设计 二、实验原理 用一个8位移位寄存器,再增加一些电路,如4个8位锁存器等,设计成为一个能为32位二进制数进行不同方式移位的移位寄存器。 三、实验步骤 1、建立一个工程项目,设置路径,项目名和顶层实体名一致; 2、设计一个8位移位寄存器电路; 3、设计一个8位锁存器电路; 4、运用元件调用声明语句和元件例化语句完成顶层设计。 四、实验程序 1、八位移位寄存器程序 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY jicun IS PORT ( CLK,CO: IN STD_LOGIC; --时钟和进位输入 MD : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位模式控制字 D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); -- 待加载移位的数据 QB : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --移位数据输出 CN : OUT STD_LOGIC); --- 进位输出 END jicun; ARCHITECTURE behav OF jicun IS SIGNAL REG : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL CY : STD_LOGIC; BEGIN

PROCESS(CLK,CO,MD) BEGIN IF CLK'EVENT AND CLK='1' THEN CASE MD IS WHEN "001"=> REG(0)<=CO; ---带进位循环左移 REG(7 DOWNTO 1)<= REG(6 DOWNTO 0);CY<=REG(7); WHEN "010" => REG(0)<=REG(7); ---自循环左移 REG(7 DOWNTO 1)<= REG(6 DOWNTO 0); WHEN "011"=>REG(7)<=REG(0); ---自循环右移 REG(6 DOWNTO 0)<=REG(7 DOWNTO 1); WHEN "100" =>REG(7)<=CO; ---带进位循环右移 REG(6 DOWNTO 0)<=REG(7 DOWNTO 1);CY<=REG(0); WHEN "101" =>REG(7 DOWNTO 0)<=D(7 DOWNTO 0); --加载待移数 WHEN OTHERS=>REG<=REG;CY<=CY;--保持 END CASE; END IF; END PROCESS; QB(7 DOWNTO 0)<=REG(7 DOWNTO 0);CN<=CY; END behav; 2、锁存器程序 library ieee ; use ieee.std_logic_1164.all ; entity suocun is port(d : in std_logic_vector(7 downto 0) ; q: out std_logic_vector(7 downto 0); clk : in std_logic ); end suocun ; architecture one of suocun is signal q1: std_logic_vector(7 downto 0);

;*********************************** ;74hc164work ;*********************************** led_seg_in: movlf08h,led_rrf_cnt send_8bit: bcf pt1,1;74hc164cp上升沿动作 btfss led_data,0 goto sdab_set1 BSF PT1,0;将二进制数从PT1.0口输出 send_1bit_OK: rrf led_data,1 bsf pt1,1 decfsz led_rrf_cnt,1 goto send_8bit return sdab_set1: bcf pt1,0 GOTO send_1bit_OK ;;;////////////;;;从74HC164输出的数据直接点亮相应的数码管,从而达到移位显示的作用。

MOVFW RAM CALL disp;NO,则RAM-LED,送显 disp: movwf data movfw data CALL GETIN_DATA movwf led_data call led_seg_in CALL delay RETURN GETIN_DATA: ADDPCW RETLW00000011b;0 RETLW10011111b;1 RETLW00100101b;2 RETLW00001101b;3 RETLW10011001b;4 RETLW01001001b;5 RETLW01000001b;6 RETLW00011111b;7 RETLW00000001b;8 RETLW00001001b;9 RETLW11111111b;0FFH RETLW11111101b;- RETLW11110000b;K

移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、原理说明 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。按代码的移位方向可分为左移、右移和可逆移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同又可分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图8-3-3-1所示。 其中 D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入 C为直接无条件清零端; 端,S L为左移串行输入端;S1、S0为操作模式控制端;R CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0→Q3),左移(方向由Q3→Q0),保持及清零。 S1、S0和R C端的控制作用如表8-3-3-1。 图8-3-3-1 CC40194的逻辑符号及引脚功能 表8-3-3-1 CC40194功能表

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图8-3-3-2所示,把输出端 Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表10-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图8-3-3-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。其状态表如表8-3-3-2所示。 表8-3-3-2 环形计数器状态表 图 8-3-3-2 环形计数器 如果将输出Q O与左移串行输入端S L相连接,即可达左移循环移位。 (2)实现数据串、并行转换 ①串行/并行转换器 串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。 图8-3-3-3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。

中北大学

课 程 设 计 说 明 书

学生姓名: 学 专 题 院: 业:

XXXXXX

学 号:

1005xxxxx

信息与通信工程学院 电子信息科学与技术

目:74HC164级联实现四位数码管显示电路设计 程耀瑜 李文强 职称: 职称: 教授 讲师

指导教师:

2013

年

1

月

17

日

中北大学

课程设计任务书

2012/2013 学年第 一 学期

学 专

院: 业:

信息与通信工程学院 电子信息科学与技术 xxxxxxx 学 号: 100xxxxxxx

学 生 姓 名: 课程设计题目: 起 迄 日 期: 课程设计地点: 指 导 教 师: 系 主 任:

74HC164 级联实现四位数码管显示电路设计 1 月 4 日~1 月 15 日 中北大学 程耀瑜,李文强 程耀瑜

下达任务书日期:

2010 年 1 月 3 日

课 程 设 计 任 务 书

2

课 程 设 计 任 务 书

1.设计目的:

本课程设计主要针对模拟电子技术和数字电子技术课程要求,培养学生在查阅资料 的基础上,进行实用电路设计、计算、仿真、调试等多个环节的综合能力,同时培养学 生用课程中所学的理论独立地解决实际问题的能力。另外还培养学生用专业的、简洁的 文字,清晰的图表来表达自己设计思想的能力。

2.设计内容和要求(包括原始数据、技术参数、条件、设计要求等) :

(1)了解 74HC164 的工作原理,掌握其功能和引脚; (2)掌握 74HC164 级联电路的设计、仿真与调试; (3)掌握 74HC164 控制多只数码管电路的设计、仿真与调试; (4)掌握方案设计与论证;

3.设计工作任务及工作量的要求〔包括课程设计计算说明书(论文)、图纸、 实物样品等〕 :

(1)提供核心器件的工作原理与应用介绍; (2)提供用 Protel99 设计的电路原理图,也可给出印刷板电路图; (3)提供用 Multisim、MaxPluss、Proteus 等其他软件对电路的仿真结果与分析; (4)提供符合规定要求的课程设计说明书; (5)提供参考文献不少于三篇,且必须是相关的参考文献;

3

8位移位寄存器的电路设计与版图实现 摘要 电子设计自动化,缩写为EDA,主要是以计算机为主要工具,而Tanner EDA则是一种在计算机windows平台上完成集成电路设计的一种软件,基本包括S-Edit,T-Spice,W-Edit,L-Edit与LVS等子软件,其S-Edit以及L-Edit为常用软件,前者主要实现电路设计,后者主要针对的是已知电路的版图绘制,而T-Spice主要可实现电路图及版图的仿真,可以用Tanner EDA实现电路的设计布局以及版图实现等一系列完整过程。本文用Tanner EDA工具主要设计的是8位移位寄存器,移位寄存器主要是用来实现数据的并行和串行之间的转换以及对数据进行运算或专业处理的工具,主要结构构成是触发器,触发器是具有储存功能的,可以用来储存多进制代码,一般N 位寄存器就是由N个触发器构成,移位寄存器工作原理主要是数据在其脉冲的作用下实现左移或者右移的效果,输入输出的方式表现为串行及并行自由组合,本设计就是在Tanner EDA的软件平台上进行对8位移位寄存器的电路设计仿真,再根据电路图在专门的L-Edit 平台上完成此电路的版图实现,直至完成的结果和预期结果保持一致。 关键词:Tanner EDA;L-Edit;移位寄存器,S-Edit

8 bits shift register circuit design and layout Abstract Electronic design automation,referred to as EDA,it is based on computers as the main tool,and Tanner EDA is a kind of software that complete the integrated circuit design on Windows platforms.Its Sub-Softwares include S-Edit,T-Spice,W-Edit,L-Edit and LVS and so on.S-Edit and L-Edit are commonly used software,S-Edit is primarily designed to achieve circuit,the latter is aimed primarily known circuit layout drawing,T-Spice can achieve schematic and layout simulation.We can achieve layout of the circuit design and a series of complete process layout used Tanner EDA tools.In this paper, Tanner EDA tools are mainly designed an 8-bit shift register.The shift register is mainly used for data conversion between parallel and serial, and the data processing tool operation or professional,its main structure is the trigger composition,flip-flop is a storage function,it can be used to store more hexadecimal code,In general N-bits register is composed of N trigger.Working principle of the shift register data under the action of the pulse, mainly the effect of the shift to the left or right,input and output of the way of serial and parallel free combination.This design is in Tanner on the EDA software platform to 8 bits shift register circuit design and simulation,then according to the circuit diagram on special L - Edit platform to complete the circuit layout implementation,until the finish is consistent with the results and expected results. Keywords:Tanner EDA;L-Edit;Shift register,S-Edit

第三章习题参考答案 1.画出以1)(2 4 6 +++=x x x x f 为联接多项式的线性移位寄存器逻辑框图,及其对应的状态图。 解:由1)(2 46+++=x x x x f ,得反馈函数为531621),,,(x x x x x x f ++=Λ,故 (1)逻辑框图: (2)状态图: 状态圈-1: 状态圈-2: 状态圈-3: 状态圈-4: 状态圈-5: 状态圈-6: 状态圈-7: 状态圈-8:

状态圈-9: 状态圈-10: 状态圈-11: 状态圈-12: 2.已知图3-2所示的7级线性反馈移位寄存器: 图3-2 (1)绘出该移位寄存器的线性递推式,联接多项式及特征多项式。 (2)给出状态转移矩阵。 (3)设初态为(1 1 1 1 1 1 1),给出输出序列a 。 解:(1)由逻辑框图得,递推式为: k k k k a a a a ++=+++357 ()0≥k 。 联接多项式为:7 4 2 1)(x x x x f +++=。 特征多项式为:7531)(~ x x x x f +++=

(2)状态转移矩阵:? ? ???? ? ?? ? ? ??0100000 101000000010001000100 000001000000011000000。 (3)输出序列:)111111111(ΛΛ=- a 。 3.设5级线性反馈移位寄存器的联接多项式为1)(2 5 ++=x x x f ,初态为(10101)。求输出序列a 。 解:由联接多项式得,反馈函数为:41521),,,(x x x x x f +=Λ。故以)10101(为初态的状态转移图为: 10101 01010001010001000001100000100000100100100100110100110100110100110100111100111100111101111101111001110001110001110000110010110110111110101110101110101110101→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→ 由此可得,输出序列为:=a 44444443444444421一个周期 0110100100000011111001010111011…。 4.证明:n 级线性反馈移位寄存器的状态转移变换是n 维线性空间n F 2上的线性变换。 证明:设f T 为n 级线性移位寄存器的状态转移变换,对n F 2,∈?βα,令),,,(110-=n a a a Λα, ),,,(110-=n b b b Λβ,有: ),,,(),,,()(121110∑=--==n i i n i n f f a c a a a a a T T ΛΛα, ),,,(),,,()(1 21110∑=--==n i i n i n f f b c b b b b b T T ΛΛβ。 ) ()() ,,,(),,,() )(,,,() ,,,()(1 211 2112211111100βαβαf f i n n i i i n n i i n i i n i n i n n f f T T b c b b a c a a b a c b a b a b a b a b a T T +=+=+++=+++=+-=-==----∑∑∑ΛΛΛΛ 对 2F k ∈?, ))((),,,(),,,()(1 21110ααf i n n i i n f f T k a c k ka ka ka ka ka T k T ===-=-∑ΛΛ。 故n 级线性反馈移位寄存器的状态转移变换是n 为线性空间n F 2上的线性变换。

74LS164 1、器件功能作用 8 位串入,并出移位寄存器 2. 概述 74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。 时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(DSA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。 主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。 3. 特性 ?门控串行数据输入 ?异步中央复位 ?符合 JEDEC 标准 no. 7A ?静电放电 (ESD) 保护: ·HBM EIA/JESD22-A114-B 超过 2000 V ·MM EIA/JESD22-A115-A 超过 200 V 。 ?多种封装形式 ?额定从 -40 °C 至+85 °C 和 -40 °C 至+125 °C 。 4. 功能图

图 1. 逻辑符号 图 2. IEC 逻辑符号 图 3. 逻辑图

图 4. 功能图 5. 引脚信息 图 5. DIP14、SO14、SSOP14 和 TSSOP14 封装的引脚配置引脚说明 6. 功能表(真值表)

H = HIGH(高)电平 h = 先于低-至-高时钟跃变一个建立时间 (set-up time) 的 HIGH(高)电平L = LOW(低)电平 l = 先于低-至-高时钟跃变一个建立时间 (set-up time) 的 LOW(低)电平q = 小写字母代表先于低-至-高时钟跃变一个建立时间的参考输入(referenced input) 的状态 ↑ = 低-至-高时钟跃变 7. 电器特性

实验五移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图10-1所示。 图10-1 CC40194的逻辑符号及引脚功能 其中 D 0、D 1 、D 2 、D 3 为并行输入端;Q 、Q 1 、Q 2 、Q 3 为并行输出端;S R 为右 移串行输入端,S L 为左移串行输入端;S 1 、S 为操作模式控制端;R C为直接无 条件清零端;CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q 0→Q 3 ),左移 (方向由Q 3→Q ),保持及清零。 S 1、S 和R C端的控制作用如表10-1。

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图10-2所示,把输出端 Q 3和右移串行输入端S R 相连接,设初始状态Q Q 1 Q 2 Q 3 =1000,则在时钟脉冲作用下Q 0Q 1 Q 2 Q 3 将依次变为0100→0010→0001→1000 →……,如表10-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图10-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 图 10-2环形计数器 如果将输出Q O 与左移串行输入端S L 相连接,即可达左移循环移位。 (2)实现数据串、并行转换

怎样用单片机驱动LED数码管显示 驱动LED数码管有很多方法,按显示方式分,有静态显示和动态(扫描)显示,按译码方式可分硬件译码和软件译码之分。 静态显示就是显示驱动电路具有输出锁存功能,单片机将所要显示的数据,显示数据稳定,占用很少的CPU时间。动态显示需要CPU时刻对显示器件进行数据刷新,显示数据有闪烁感,占用的CPU时间多。 这两种显示方式各有利弊;静态显示虽然数据稳定,占用很少的CPU 时间,但每个显示单元都需要单独的显示驱动电路,使用的硬件较多; 动态显示虽然有闪烁感,占用的CPU时间多,但使用的硬件少,能节 省线路板空间。 硬件译码就是显示的段码完全由硬件完成,CPU只要送出标准的BCD 码即可,硬件接线有一定标准。软件译码是用软件来完成硬件的功能,硬件简单,接线灵活,显示段码完全由软件来处理,是目前常用的显示驱动方式。 比较常用的显示驱动芯片有:74LS164 , CD4094+ULN2003(2803) ,74HC595+ULN2003(2803) , TPIC6B595,AMT9095B, AMT9595等许多。 另外,市场上还有一些专用的LED扫描驱动显示模块如MAX7219等,功能很强,价格稍高一些。下面是一个用74LS164驱动显示的例子和一个用4094扫描驱动显示的例子: ? 上例图中加了一个PNP型的三极管来控制数码管的电源,是因为164没有数据锁存端,数据在传送过程中,对输出端来说是透明的,这样,数据在传送过程中,数码管上有闪动现象,驱动的位数越多,闪动现象越明显。为了消除这种现象,在数据传送过程中,关闭三极管使数码管没电不显示,数据传送

8 位串入、并出移位寄存器 1. 概述 74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。 时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(D SA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。 主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。 2. 特性 ?门控串行数据输入 ?异步中央复位 ?符合JEDEC 标准no. 7A ?静电放电(ESD) 保护: ·HBM EIA/JESD22-A114-B 超过2000 V ·MM EIA/JESD22-A115-A 超过200 V 。 ?多种封装形式 ?额定从-40 °C 至+85 °C 和-40 °C 至+125 °C 。 3. 功能图 图 1. 逻辑符号

图 2. IEC 逻辑符号 图 3. 逻辑图 图 4. 功能图 4. 引脚信息

图 5. DIP14、SO14、SSOP14 和 TSSOP14 封装的引脚配置 引脚说明 74HC164中文资料(功能,真值表,引脚图及电气参数介绍) SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。一个高电平输入后就使另一个输入端赋能,这个输入就决定了第一个触发器的状态。虽然不管时钟处于高电平或低电平时,串行输入端的数据都可以被改变,但只有满足建立条件的信息才能被输入。时钟控制发生在时钟输入由低电平到高电平的跃变上。为了减小传输线效应,所有输入端均采用二极管钳位。 https://www.doczj.com/doc/234121722.html,/info/cmos/0083928.html H=高电平(稳定态)L=低电平(稳定态)×=不定↑=从低电平转换到高电平 QA0…QH0=在稳定态输入条件建立前QA…QH 的相应电平 QAn…QHn=在最近的时钟输入条件(↑)建立前QA…QH 的相应电平,表示移位一位

实例1 74HC164是串行输入,并行输出接口器件,可用在单向的并行输出/并行地址锁存等. 74HC164因为价格便宜,容易使用特别适合使用在在需要用到数码管显示IO口又比较紧张的电子产品中,下面浅谈使用方法: 1. 首先先了解他的引脚功能和逻辑图,如下图: 图1 引脚名称和用途

图2 真值表 通过真值表我们可以了解到,A,B两个输入端是互锁的,CLK上升沿时数据移入移位寄存器中,CLEAR为清零用的,接低电平时所有端口都输出低电平,了解了真值表之后开始运用了,先给出如下原理图: 图3 原理图

图中,采用义隆的EM78P153作为控制芯片,P50作为CLK时钟信号,注意平时数据不传输时,时钟信号是不发送的应一直保持低电平或者高电平,数据需要传输的时候才输出时钟信号^_^ ,继续P51作为移位数据输出端,接到74HC164的B端,A端接高电平,当然也可以AB端短路,然后连接到DATA移位数据端,P52作为数码管的选通信号(也可以叫消隐^_^), 作用是使数据传输过程暂时关闭显示,以免显示出不需要的数据,原因是应为164不带锁存功能,数据传输过程是一位一位的向高位移位输出的,所以要等数据全部移入后才打开始点亮数码管. 注意了哦,通过查看164的规格书发现,164输出高电平电流比输出低电平电流要小,亦称灌电流大,扇出电流弱,所以适合选用共阳数码管,如图,本人偷懒没有画出那个数码管的8字 该介绍的介绍的差不多了,废话少说,该开始干活了,任务是: 显示0-9 每秒+1 ,到9后又返回0,一直循环显示,根据任务得到如下流程图: 1. 显示部分: 将需要显示的数值送入A ==>查表求得显示段码==>将段码逐位移入164==>8位移完后点亮数码管==>延时==>返回第一步执行 2. 中断部分: 进入中断==>保存现场(以备调查取证,送你入狱^_^)==>重置TCC==>够1秒钟将需要显示的数据+1,并重置,不够就退出; 根据以上要求就开始写代码调试了,要注意一点,数据移位时一定要记得高位在前哦,否则显示错误别怪我没有说清楚,我当年实验时就因为这个数据移位方向反了排查了半天,甚至以为是时钟频率不对,又以为时许不对.....搞了半天,NND后来重看DATASHEET才发现,原来是低级错误啊,呜呼哀哉.......,希望你不要重蹈我覆辙,哎哟!! 谁! 谁! 谁扔砖头上来? 啥? 你扔的? 我废话太多.........,那俺少来两句,继续上菜, 咦好像没啥可说的了,上源程序吧 1.;中断部分: 2. 3.;;;;;;;;;;中断;;;;;;;; 4.INTPUT: 5.MOV TEMPA, A;

目录 摘要 (1) 1 多功能双向移位寄存器 (2) 1.1 基本工作原理 (2) 1.2 基本实现方案 (2) 2 电路图设计 (4) 2.1 电路结构 (4) 2.2 真值表 (4) 3 Verilog描述8位双向移位寄存器 (6) 4 程序仿真 (8) 5 总结 (10) 参考文献 (11)

摘要 移位寄存器是基本的同步时序电路,基本的移位寄存器可以实现数据的串行/并行或并行/串行的转换、数值运算以及其他数据处理功能。在本设计中,使用硬件描述语言Verilog,在EDA工具QuartussII中,设计8位双向移位寄存器硬件电路,根据设计语言进行功能时序仿真,验证设计的正确性与可行性。 关键字:Verilog QuartusII 移位寄存器

8位双向移位寄存器电路设计 1 多功能双向移位寄存器 1.1 基本工作原理 移位寄存器是基本的同步时序电路,基本的移位寄存器可以实现数据的串行/并行或并行/串行的转换、数值运算以及其他数据处理功能。在本设计中定义移位寄存器中的数据从低位触发器移向高位为右移,移向低位为左移。 为了扩展逻辑功能和增加使用的灵活性,某些双向移位寄存器集成电路产品 又附加了并行输入、并行输出等功能。如图1所示是上述几种工作模式的简化示意图。 并行输入 并行输出 右移串行输入(D IR 左移串行输出(D OL 右移串行输出(D OR ) D IL ) 0123 图1 多功能移位寄存器工作模式简图 1.2 基本实现方案 图2所示是实现数据保持、右移、左移、并行置入和并行输出的一种电路方 案。图中的D 触发器m FF 是N 为移位寄存器中的第m 位触发器,在其数据输入端插入了一个4选1数据选择器m MUX ,用2位编码输入10S S 、控制m MUX ,来选择触发器输入信号m D 的来源。当100S S ==时,选择该触发器本身输出的m Q , 次态为1m n n m m Q D Q +==,使触发器保持状态不变;当100,1S S ==时,触发器1m FF -的输出1m Q -被选中,故CP 脉冲上升沿到来时,m FF 存入1m FF -此前的逻辑值,即 1m 1n n m Q Q +-=,而1m +1n n m Q Q +=, 从而实现右移功能;类似地,当101,0S S ==时,m MUX 选择1m Q +,实现左移功能;而当101S S ==时,则选中并行输入数据m DI ,其次 态1 n m m Q DI +=,从而完成并行数据的置入功能。上述四种操作概述于表1,此外,

74ls164 能否动态驱动多位数码管void display() //数码显示 { SCON=0; //初始化串行口方式SBUF=dispcode[ge]; while(!TI); TI=0; led4=0; delay(2); led4=1; SBUF=dispcode[shi]; while(!TI); TI=0; led3=0; delay(2); led3=1; SBUF=dispcode[bai]; while(!TI); TI=0; led2=0; delay(2);

SBUF=dispcode[qian]; while(!TI); TI=0; led1=0; delay(2); led1=1; SBUF=dispcode[wan]; while(!TI); TI=0; led0=0; delay(2); led0=1; } 74ls164数码管驱动(第二个程序) #define clock PORTD.1 #define date PORTD.0 #define clock_en DDRD.1 #define date_en DDRD.0 unsigned char lab[2][10]={ 0x03,0x9F,0x25,0x0D,0x99,0x49,0x41,0x1F,0x01,0x09, 0x02,0x9E,0x24,0x0C,0x98,0x48,0x40,0x1E,0x00,0x08}; void send(unsigned char w) { unsigned char i; for(i=0;i<8;i++) { clock=0; date=w&1;

实验五 移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用 — 实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图10-1所示。 图10-1 CC40194的逻辑符号及引脚功能 其中 D 0、D 1 、D 2 、D 3为并行输入端;Q 0、Q 1、Q 2、Q 3为并行输出端;S R 为右移串行输入端,S L 为左移串行输入端;S 1、S 0 为操作模式控制端; R C 为直接无条件清零端;CP 为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q 0→Q 3),左移(方向由Q 3→Q 0),保持及清零。 S 1、S 0和R C 端的控制作用如表10-1。 表10-1

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图10-2所示,把输出端 Q 3和右移串行输入端S R 相连接,设初始状态 Q 0Q 1 Q 2 Q 3 =1000,则在时钟脉冲作用下Q Q 1 Q 2 Q 3 将依次变为0100→0010→0001 →1000→……,如表10-2所示,可见它是一个具有四个有效状态的计数

实验五、移位寄存器的设计 一、实验目的 设计并实现一个异步清零同步置数8位并入并出双向移位寄存器电路。 二、实验原理 在数字电路中,用来存放二进制数据或代码的电路成为寄存器。寄存器按功能可分为:基本寄存器和移位寄存器。移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。下面是一个并入串出的8位左移寄存器的VHDL描述: library ieee; use ieee.std_logic_1164.all; port(data_in: in std_logic_vector(7 downto 0); clk: in std_logic; load: in std_logic; data_out:out std_logic); end; architecture one of left8 is signal q: std_logic_vector(7 downto 0); begin process(load,clk) begin if load='1' then q<=data_in; data_out<='Z'; elsif clk'event and clk='1' then for I in 1 to 7 loop 图5-1 q(i)<=q(i-1); end loop; data_out<=q(7); end if; end process; end one; 异步清零同步置数8位并入并出双向移位寄存器电路结构图如图5-1所示。 三、实验要求 输入信号有D[0]~D[7]、DIL、DIR、S、LOAD、CLK和CLR,其中CLK接时钟,其余接拨码开关,输出信号有Q[0]~Q[7],接发光二极管。改变拨码开关的状态,观察实验结果。 实验工程项目命名为rlshift,源程序命名为rlshift8.vhd。 四、实验记录 对比较器实验结果造表,得到其真值表。 五、实验报告要求

实验七 移位寄存器及其应用 一、实验目的 1. 掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2. 熟悉移位寄存器的应用——环形计数器。 二、实验原理 1. 移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又有右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图 1所示。 图 1 74LS194的逻辑符号及其引脚排列 其中D 3、D 2、D 1、D 0为并行输入端, Q 3、Q 2、Q 1、Q 0为并行输出端;S R 为右移串行输入端,S L 为左移串行输入端,S 1、S 0为操作模式控制端;CR 为直接无条件清零端;CP 为时钟脉冲输入端。74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q 3→Q 0),左移(方向由Q 0→Q 3),保持及清零。S 1、S 0和CR 端的控制作用如表 1所示。 表 1

2.移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计致器和串行累加器的线路及其原理。 (1) 环形计数器:把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图2所示,把输出端Q 0和右移串行输入端S R 相连接,设初始状态Q 3 Q 2 Q 1 Q =1000, 则在时钟脉冲作用下Q 3Q 2 Q 1 Q 将依次变为0100→0010→0001→1000→……,可见它是具 有四个有效状态的计数器,这种类型的计效器通常称为环形计数器。图2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

8位数码扫描显示电路设计 一、实验目的 学习硬件扫描显示电路的设计; 二、实验原理 动态数码扫描显示方式是利用了人眼的视觉暂留效应,把八个数码管按一定顺序进行点亮,当点亮的频率不大时,我们看到的是数码管一个个的点亮,然而,当点亮频率足够大时,我们看到的不再是一个一个的点亮,而是全部同时显示,与传统方式得到的视觉效果完全一样。因此我们只要给数码管这样一个扫描频率,那么就可以实现两个以上的数码管同时点亮。而这个频率我们可以通过一个计数器来产生,只要计数频率足够大,就可以实现我们的要求。事实上,因为数码管点亮不是瞬间就可以的,它也需要一定的时间,该时间与数码管的选择有关系。为了折中这一对矛盾,实验中一般可将计数频率选择在100Hz左右。 图示8位数码扫描显示电路,其中每个数码管的8 个段:h、g、f、e、d、c、b、a(h 是小数点)都分别连在一起,8 个数码管分别由8 个选通信号k1、k2、… k8 来选择。被选通的数码管显示数据,其余关闭。如在某一时刻,k3 为高电平,其余选通信号为低电平,这时仅k3 对应的数码管显示来自段信号端的数据,而其它7 个数码管呈现关闭状态。根据这种电路状况,如果希望在8 个数码管显示希望的数据,就必须使得8 个选通信号k1、k2、… k8 分别被单独选通,并在此同时,在段信号输入口加上希望在该对应数码管上显示的数据,于是随着选通信号的扫变,就能实现扫描显示的目的。 实验参考扫描显示程序中clk 是扫描时钟;SG 为7 段控制信号,由高位至低位分别接g、f、e、d、c、b、a 7个段;BT 是位选控制信号,接图5-2 中的8 个选通信号:k1、k2、… k8 。程序中CNT8 是一个3 位计数器,作扫描计数信号,由进程P2 生成;进程P3 是7 段译码查表输出程序,进程P1 是对8 个数码管选通的扫描程序,例如当CNT8 等于

设计 74hc164 控制数码管显示系统 (00-99 显示)

一、总体设计 1、 系统组成 本系统功能由硬件和软件两大部分协调完成。 本系统的硬件采用模块化设计,以单片机控制为核心,74hc164 为驱动,与数码管 接口电路等组成单片机控制的数码管显示系统。该系统硬件主要包括主控模块、报警模块、 数码管显示模块等。其中单片机控制器主要完成外围硬件的控制以及一些运算按功能, 74hc164 完成串行输入,并行输出,数码管显示模块完成字符、数字的显示功能。 应用软件采用模块化设计方法。 该系统软件主要由主程序、 定时器 T0 中断服务子程序、 164 子程序等模块组成。 二、硬件设计 1、主控模块设计 本项目采用 AT89S52 单片机。 电源、时钟信号以及复位电路是单片机工作的基本条件,缺一不可。单片机系统的 基本工作电路电源电路、时钟电路、复位电路。 (1)电源电路模块设计 电源模块为系统板上的其他模块提供+5V 电源。系统板可从 USB 接口获取+5V 电源,即 用相应配套的 USB 线从电脑主机上获取+5V 直流电源。 (2)时钟电路模块设计 单片机的时钟信号用来位单片机芯片内部的各种操作提供时间基准。 时钟电路为单片机产生时钟脉冲序列, 作为单片机工作的时间基准, 典型的晶体振荡频 率为 12MHz。 由于 AT89S52 系列单片机芯片内有时钟振荡电路, 因此本项目中采用内部时钟方式, 只 要在单片机的 XTAL1 和 XTAL2 引脚外接石英晶体和微调电容, 就够成了自激振荡器并在单片 机内部产生时钟脉冲信号,具体电路如图 1-1。图中电容 C1 和 C2 的作用是稳定频率和快速 起振。 (3)复位电路模块设计 复位电路使用单片机或系统中的其他部件处于某中确定的状态。 当在 MC-51 系列单片机的 RST 引脚处引入高电平并保持 2 个机器周期,单片机内部就 执行复位操作。实际应用中,复位操作有两种基本形式:一种是上电复位,另一种是按键复 位。本项目中采用案件复位方式,具体电路设计如图 1-1。在单片机运行期间,可以用此案 件完成复位操作。 2、报警模块设计 本项目中选用蜂鸣器。 蜂鸣器的正极接+5V 的电源, 另一极接在三极管 8550 的集电极, 三极管 8550 主要用于信号的放大,以驱动数码管工作。三极管 8550 的基极通过限流电阻 接到单片机 P2 的 P2.0 如图 1-1,通过控制三极管 8550 的基极电平来打开或关闭蜂鸣器。三 极管 8550 的发射极接地。 3、数码管显示模块设计 本项目中选用 8 段共阳极数码管,数码管的 a、b、c、d、e、f、g、dp 段分别与 74hc164 的 QA、QB、QC、QD、QE、QF、QG、QH 相连,用来控制显示数字。数码管的公共使能端