gcc参数高级应用

- 格式:docx

- 大小:23.39 KB

- 文档页数:8

PCC -一种可塑造的颜料沉淀碳酸钙(简称PCC)已明确为未来的碳酸盐颜料。

其亮点和纯度是无以伦比的。

其可采用的产品种类之多,确保造纸工作者所遇到的任何问题,用PCC都可以解决。

PCC是一种沉淀碳酸钙,其形态为鲜亮的结晶体。

PCC的原料一般是生石灰(CaO)和二氧化碳(CO2)气体。

生产的第一步是熟化,即生石灰与大量的水混合。

CaO与水反映生成氢氧化钙,成泥浆状被汞送到反应器。

在反应器内,氢氧化钙与含有CO2 的气体混合,PCC即沉淀下来。

反映完成后,泥浆状的PCC固含量为18~25%,经过筛选汞送到贮存槽内,以供作为造纸的填料。

用于纸张涂布要求有较高的固含量,因此PCC浆液要脱水到70~72%的固含量。

脱水后的PCC 经搅拌器再分散,在搅拌过程中不加水只加分散剂。

再分散后的PCC经筛选后备用于涂布。

世界上大部分PCC是在附属车间制备的,此附属车间与造纸厂毗邻。

附属车间接受纸厂的烟道气作为CO2的来源。

这种设想的优点是PCC最终产品直接汞送到纸厂的贮存槽。

一座现代化的PCC车间能够生产很多种不同的产品。

能够生产出的每种产品在粒度大小、亮度等方面毫无变化是很重要的。

如果产品质量在长期内保持很一致的话,则纸厂仅就使用PCC(作为填料或涂布颜料)将受益匪浅。

现代化的生产工艺能保证质量的恒定。

PCC和研磨碳酸钙研磨碳酸钙(GCC)是由石灰石或大理石制成的,把这些石头经几段压碎并磨成所要求的细度。

在研磨过程中要经过几次净化。

这一般由浮选和磁选分离出杂质,往往选出大量的废物。

研磨碳酸钙含有小的不规则的碎石和片状石。

相反,PCC沉淀会产生很细的碳酸钙结晶。

此结晶能制成不同的形态(图右)。

PCC的粒度大小,按平均粒度来说,能够千差万别。

对研磨碳酸钙,其粒度的变化是由研磨的次数多少来决定的,而PCC的粒度在沉淀过程中控制的。

PCC的形状不同于所要求的聚集程度有关。

显然,聚集的粒子将比同样大小的固体粒子有较大的表面积(以m2/g计)。

使用傅立叶OCT 评估神经节细胞丢失Prepared by Larry J Alexander, OD FAAOSenior Director of Clinical Education, Optovue, Inc.使用傅立叶域光学相干断层扫描检测青光眼患者黄斑处节细胞丢失Ou Tan, Vikas Chopra, Ake Tzu-Hui Lu, Joel S. Schuman, Hiroshi Ishikawa, Gadi Wollstein, Rohit Varma, David Huang.(Ophthalmology 2009;116:2305–2314 © 2009 by the American Academy of Ophthalmology.)青光眼的特征是神经节细胞和相对应的视神经轴突的丢失,这是长期以来被公认的。

在目前的情况下,对青光眼的标准研究方法包含观察视乳头,观察视网膜神经纤维层萎缩,视野检查和视乳头周边的视神经纤维层的各种图像。

在FD-OCT(频域或傅立叶域OCT)RTVue®出现之前,测量节细胞复合体还没有被应用于临床。

RTVue 的快速和高分辨率,带来更高准确性和重复性的GCC™(节细胞复合体)图像。

由此推断在未来,对节细胞复合体丢失的评估,对于青光眼的病人诊断可以提供重要的信息。

本次研究是使用傅立叶域OCT(RTVue FD-OCT 系统)判断黄斑边界并且评估节细胞复合体的厚度图。

参与者为高级青光眼影像研究组(longitudinal Advanced Imaging for Glaucoma Study ,AIGS)。

把患者分为三组,并对其基于视野,视乳头观测(窄盘沿,垂直杯盘比和视盘出血),中央角膜厚度,前房评估的检查。

这些组分为1>正常人组(65), 2> 视野缺损前青光眼组(52), 3> 有视野缺损的青光眼组(78). 研究者为RTVue FD-OCT设计了一个3D扫描,用于定义黄斑地区边界,并用0.6秒时间在7毫米的方形区域内使用了14,928个A扫描。

gcc 编译流程gcc 是一种常用的编译器,被广泛应用于程序开发和编译过程中。

在了解 gcc 编译流程之前,我们先简单介绍一下编译的基本概念。

编译是将高级语言(如C、C++ 等)编写的源代码转换为机器语言(如汇编代码或机器指令)的过程。

编译器是用来进行编译的工具,而 gcc 就是其中较为常用的一个。

gcc 是GNU Compiler Collection(GNU 编译器集合)的缩写,它是一个由GNU 开发的自由软件项目,也是许多Unix-like 系统中默认的编译器。

gcc 支持多种编程语言,包括C、C++、Objective-C、Objective-C++、Fortran、Ada 等。

这里我们以C 语言为例,来介绍 gcc 的编译流程。

gcc 的编译过程可以分为四个主要阶段:预处理、编译、汇编和链接。

下面将详细介绍这四个阶段的具体操作和作用。

1. 预处理阶段:在预处理阶段,gcc 将源代码中的预处理指令进行处理,生成预处理后的代码。

预处理指令以"#" 开头,如"#include"、"#define" 等。

预处理的主要作用是对源代码进行宏替换、文件包含和条件编译等操作,以生成经过宏展开和文件合并后的代码。

2. 编译阶段:在编译阶段,gcc 将预处理后的代码转换为汇编代码。

汇编代码是一种与机器相关的低级语言,它是由一系列的机器指令组成。

编译的主要任务是对源代码进行词法分析、语法分析和语义分析等操作,以生成对应的汇编代码。

3. 汇编阶段:在汇编阶段,gcc 将汇编代码转换为机器代码。

机器代码是二进制的指令序列,可以被计算机直接执行。

汇编的主要作用是将汇编代码翻译成机器指令,生成可执行文件。

4. 链接阶段:在链接阶段,gcc 将多个源文件编译生成的目标文件进行链接,生成最终的可执行文件。

链接的主要作用是解决函数调用和变量引用等符号之间的关系,将多个目标文件合并成一个可执行文件。

gcc 编译configure语句摘要:一、GCC 编译器简介1.GCC 的发展历程2.GCC 的重要性3.GCC 的应用领域二、编译configure 语句1.configure 语句的作用2.configure 语句的语法结构3.configure 语句的参数及用法三、GCC 编译configure 语句实例1.简单的GCC 编译configure 语句实例2.高级的GCC 编译configure 语句实例四、GCC 编译configure 语句常见问题及解决方法1.编译configure 语句失败的原因2.解决编译configure 语句失败的方法正文:一、GCC 编译器简介GCC(GNU Compiler Collection)是一款由GNU 计划开发的编程语言编译器。

它支持多种编程语言,如C、C++、Java、Fortran 等。

GCC 具有高度可移植性、强大的功能和优秀的性能,被广泛应用于各种操作系统和开发环境中。

二、编译configure 语句1.configure 语句的作用configure 语句是GCC 编译器中用于配置编译选项的关键部分。

它可以根据不同的编译目标和平台,自动选择合适的编译选项,以简化编译过程。

2.configure 语句的语法结构configure 语句的基本语法结构如下:```configure [options]```其中,`options`为可选项,用于指定具体的编译选项。

3.configure 语句的参数及用法configure 语句的参数包括:- `--host`:指定目标主机。

- `--target`:指定目标平台。

- `--prefix`:指定安装目录。

- `--with-xxx`:指定需要使用的库或工具。

三、GCC 编译configure 语句实例1.简单的GCC 编译configure 语句实例以下是一个简单的GCC 编译configure 语句实例,用于编译一个名为`example.c`的C 语言源文件:```gcc -o example example.c```2.高级的GCC 编译configure 语句实例以下是一个高级的GCC 编译configure 语句实例,用于编译一个名为`myprog`的C++程序,并使用`-Wall`选项开启编译器警告:```gcc -o myprog myprog.cpp -Wall```四、GCC 编译configure 语句常见问题及解决方法1.编译configure 语句失败的原因编译configure 语句失败的原因可能包括:- 语法错误:configure 语句的语法有误。

c语言标准gcc -回复“C语言标准(gcc)”是指使用GNU编译器集合(GNU Compiler Collection)编译器来实现C语言标准的一套规范。

本文将一步一步回答有关C语言标准(gcc)的相关问题。

第一步:介绍GCC和C语言标准GCC是GNU计划的一部分,它是一套高度优化的编译器系统,支持多种编程语言,包括C语言。

GCC的核心是一个编译器集合,这些编译器可以将源代码转换成可执行代码。

C语言是一种通用的高级编程语言,广泛用于操作系统、嵌入式系统和图形化应用程序等领域。

第二步:了解C语言标准C语言标准是由国际标准化组织(ISO)和国际电工委员会(IEC)共同制定的一套规范,用于定义C语言的语法、数据类型、函数库以及编译器行为等。

目前,最新的C语言标准是ISO/IEC 9899:2018,通常简称为C18。

之前的版本包括C99和C11。

C语言标准的发布旨在保持语言的稳定性和一致性,以便开发人员可以在不同的编译器和平台上编写可移植的代码。

第三步:gcc对C语言标准的支持GCC作为一个开源编译器,一直致力于对C语言标准的良好支持。

GCC 通过不断更新和改进内部编译器前端和后端来提供对不同C语言标准的支持。

当gcc的命令行参数设置为“-std=c99”、“-std=c11”或“-std=c18”时,gcc将会按照相应的C语言标准进行编译。

此外,gcc还提供了一些扩展功能,以便开发人员使用一些特定于gcc的功能和优化。

第四步:编写符合C语言标准的代码为了确保代码符合C语言的规范,开发人员应该在编码过程中遵循C语言标准的要求。

首先,应该选择一个合适的C语言标准,并在编译时设置gcc参数以匹配所选的标准。

其次,要遵守C语言的语法规则,如正确使用变量、数据类型和运算符等。

此外,还应该遵循最佳实践,如良好的代码注释、模块化设计和错误处理等。

第五步:测试和调试编写完成符合C语言标准的代码后,开发人员应该进行测试和调试。

gcc -include选项的用法标题:GCC中include选项的用法及详细解析引言:GCC是一款常用的编译器,广泛应用于各种平台和编程语言中。

在使用GCC进行编译时,include选项是非常常用的一个选项,它能够指定编译器搜索头文件的路径。

本文将详细介绍GCC中include选项的用法,并针对不同情况进行一步一步的解析,帮助读者更好地理解和应用include选项。

第一部分:include选项的基础知识1.1 include选项的作用include选项用于指定编译器搜索头文件的路径,即告诉编译器在哪里查找头文件。

1.2 include选项的格式GCC的include选项的格式为:-I <路径>,其中“-I”是一个固定的标记,后面跟上具体的路径。

第二部分:include选项的常见用法2.1 指定系统头文件路径在使用GCC编译程序时,需要使用系统提供的头文件,这些头文件通常安装在标准路径下,如/usr/include。

可以使用include选项来指定系统头文件路径,以确保编译器能够正确找到所需的头文件。

示例命令:gcc -I/usr/include program.c2.2 指定自定义头文件路径在编写程序时,有时会使用到自定义的头文件。

可以使用include选项来指定自定义头文件路径,以确保编译器能够找到这些头文件。

示例命令:gcc -I/path/to/header program.c2.3 添加多个头文件路径如果项目中使用到了多个自定义头文件路径,可以使用多个include选项来指定这些路径。

示例命令:gcc -I/path/to/header1 -I/path/to/header2 program.c2.4 使用相对路径在某些情况下,我们可能希望使用相对路径来引用头文件。

可以使用include选项结合相对路径来实现这一目的。

示例命令:gcc -I./include program.c第三部分:include选项的进阶使用3.1 使用尖括号或双引号在使用include选项时,可以选择使用尖括号(<>)或双引号("")来引用头文件。

gcc 常用参数

GCC(GNU Compiler Collection)是一个常用的编译器,用于将源代码编译为目标代码。

GCC提供了许多常用的编译参数,以下是其中一些常用的参数:

-c:仅编译源代码文件,生成目标文件,但不进行链接操作。

-o:指定输出文件的名称。

-g:生成调试信息,方便程序调试和错误排查。

-Wall:显示所有警告信息。

-I:指定搜索包含头文件的路径。

-L:指定搜索包含库文件的路径。

-l:链接指定的库文件。

-O:优化生成的代码,提高执行效率。

-fPIC:生成位置无关的代码(Position Independent Code),用于生成动态库。

-D:定义宏。

-U:取消定义宏。

这些参数可以在编译过程中使用,以控制编译和链接的行为。

具体使用哪个参数取决于源代码的特性和编译器的版本。

建议查阅GCC的官方文档或使用gcc --help命令获取更多参数信息。

GCC编译器优化选项分析及具体优化了什么收藏起因:目前项目使用nios IDE作为开发平台,其使用的编译器为gcc的交叉编译器。

在设定编译条件时,在debug模式下生成的程序正常,但是在release模式下会出现LCD显示的开端显示不全,缺少一个字节或字的状况。

为了了解具体为什么造成该问题,对两种模式下的配置做了对比,编译器皆为nios2-elf-gcc交叉编译器,debug模式编译器参数为:-DALT_DEBUG -O0 -g –Wall。

release模式编译器参数为: -DALT_RELEASE -O2 -g –Wall。

两种模式下的参数简单说明如下-DALT_DEBUG:目前没有明确资料显示该项的具体作用,根据命名可认为与调试有关选项。

且两种模式下都有,暂时认为不会造成差异。

-O0: gcc编译器默认优化等级。

-g:gdb调试器支持选项用于在编译时生成相关调试信息。

-Wall:打开所有编译器告警选项,即编译器最严格告警模式。

-O2:gcc编译高于O0低于O3的编译优化选项。

通过对比可以发现两种模式主要的不同在于编译器优化程度不同,那么编译器在两种优化下究竟做了什么优化那?是否由这些问题造成的显示丢失问题那??现在我们来看看gcc编译器的优化参数到底做了什么优化。

(注:由于关于nios2-elf-gcc的文档资料十分稀少,不能形成可分析的文档,所以以通用的gcc作为分析,毕竟同出一源)正文:GCC编译器优化选项介绍:GCC编译器在目前是不是用最多的编译器也相去不远,尤其在嵌入式领域很多编译器都是基于GCC的cross gcc版本。

毕竟功能成熟而且有开放的源代码。

这里只介绍优化编译的参数-O用来开启优化编译选项。

-O0:默认模式,不做任何优化。

-O1:优化。

该模式下对于一个大的函数或功能会花费更多的时间和内存。

在-O1下:编译会尝试减少代码体积和代码运行时间。

但是并不执行会花费大量时间的优化操作。

软件工程专业培养计划( 080611W )Software Engineering一、培养目标本专业培养能适应 21 世纪社会主义现代化建设需要的,德智体美全面发展的,掌握软件工程专业的 基础知识,具有从事计算机软件分析、设计和开发所必备的相关知识,具备一定的系统软件和应用软件的 分析、设计和开发的基本能力,能在科研、教育、企事业、行政管理等方面从事科学研究、软件开发、计 算机教学、 应用计算机技术进行管理等工作的, 具有创新精神和较强实践能力的应用型高级工程技术人才。

b5E2RGbCAP二、培养要求1、思想品德素质要求:热爱社会主义祖国,拥护中国共产党领导,掌握马列主义、毛泽东思想、邓 小平理论和三个代表重要思想的基本原理,树立正确的世界观、人生观、价值观,具有为国家昌盛繁荣、 为现代化建设奋斗的志向和责任感;具有扎根基层、踏实肯干、爱岗敬业、团结协作,遵纪守法的良好素 养和道德品质;具有理论联系实际,实事求是的科学态度和严谨作风;具有积极进取、勇于探索的新时代 大学生风貌。

p1EanqFDPw2、业务培养要求:本专业学生主要学习自然科学基础、技术科学基础和本专业领域及相关专业的基 本理论和基本知识,受到现代工程师的基本训练,具有分析和解决实际问题及开发计算机软件等方面的基 本能力。

DXDiTa9E3d 毕业生应获得以下几方面的知识和能力: 掌握软件工程专业的基础理论和基础知识,受到良好的科学思维方法的训练; 运用软件工程专业的基本理论和基本方法分析和解决实际问题,具有研究和开发计算机软件系 了解计算机科学与技术学科的发展方向; 具有较强的英语应用能力,能顺利地阅读本专业的英文资料,掌握资料检索查询的基本方法;3、达到国家规定的大学生体育合格标准,具有一定的基本体育知识,掌握科学的体育锻炼方法和技 能,积极参加体育活动,有意识地增强体魄,提高心理素质、审美情操,保证身心健康。

RTCrpUDGiT三、主干学科计算机科学与技术 四、学制 四年 五、授予学位 工学学士六、学位课程(共 100.0 学分)马克思主义基本原理,毛泽东思想、邓小平理论及三个代表重要思想概论,大学外语,高等数学,线 性代数,概率论与数理统计, C++ 程序设计,离散数学,数据结构,操作系统,计算机原理,计算机网络, 软件工程概论, UML 系统建模与设计,数据库原理,设计模式,编译技术,算法设计与分析 5PCzVD7HxA 实践环节:毕业设计(论文)七、课程和环节的总体框架图(1) (2) 统的能力; (3) (4)教学校长:教学质量处处长:教学工作负责人: 执笔人:课程教学体系(图表)实践教学体系(图表)代码学时48 授课实验学时-一- -二二 三四五、. 八七八公 共- 基 础 课〈1130012 思想道德修养与法律 3.0 301811人文 社科部〈1130051基础克思主义基本原理3.0 48 30182〈1130131中国近现代史纲要 2.0 32 2482〈1130071 *毛泽东思想、邓小平 理论和三个代表”重要 6.0 96 60364〈1110024 体育8.0128 96322 2 2 2体育部 X1100184 *大学外语 16.0 256 2564444外语学院 x1100141外语技能训练 2.0 3216161外语学院x1080332 *高等数学 11.0 176 1601655理学院公共基础课小计 51.0 816 672144 12 12 8742专, 业基 础: 课: x2080011 *线性代数2.0 32 322理学院x2080021 *概率论与数理统计 3.0 48 483理学院 x2160241 *C++程序设计 6.0 96 70 266软件学院x2050651 数字逻辑 2.0 32 2662软件学院 x2160031 *离散数学 4.0 64 644软件学院〈2050661 *数据结构5.0 80 60 205软件学院x2050751 汇编语言 3.0 48 38 103软件学院x2050131*计算机原理 4.0 64 56 84软件学院 x2050121 *算法设计与分析3.0 48 32 163软件学院x2050041 *计算机网络 4.0 64 5684软件学院 x2050741 *软件工程概论3.0 48 483软件学院专业基础课小计39.0 624 530 946 11 8 104专-业: 课.x3050021 *数据库原理 4.0 64 48164软件学院x3050101 *操作系统 4.0 64 644软件学院 x3050541 *编译技术4.0 64 48 164软件学院x3050551 *UML 系统建模与设计2.0 32 24 82-9软件学院 x3050561 web 基础应用2.0 32 24 82软件学院x3050571*设计模式 2.0 32 24 82-9软件学院x3050581 人机交互技术2.0 32 24812-19软件学院x3050591 软件体系结构 2.0 32 3211-18软件学院x3050601软件测试 2.0 32 24 811-18软件学院x3050611 ORACLE 数据库设计3.0 4832162-9软件学院专业课小计 27.0 432 344 88 0 0 0 8 6 5 80 0必修课合计117.01872 1546182 144 18 23 24 23 13 10必 修课表一软件工程专业课程设置及学时分配表备注:科研促进教学课程GCC高级应用;MFC高级应用C#.Net高级应用;ASP .NET高级应用;J2EE高级应用jLBHrnAlLg健康教育课按照课内0.5学分、课外0.5学分执行。

G++教程各位选手大家好,本文档为gcc/g++/gdb使用教程,本教程所提及的基本操作一般不会因为版本特性而出错。

教程将介绍如何在各种g++内核的IDE和文字界面下使用g++编译链接C 语言源程序生成目标代码,创立动态链接库(.so,.dll),使用动态链接库。

建议先阅读Visual Studio教程简介gcc/g++是gnu项目下的C/C++编译器,是所有Linux环境下默认的C程序编译器。

windows 化的g++编译器主要有MinGW、cygwin等等。

以这些编译器为基础开发的IDE(集成开发环境)有Dev C++、CodeLite等等。

g++内核的IDE的使用IDE的操作基本上都大同小异,可以参考Visual Studio教程新建一个工程例如在Dev C++4.9.9.2(内核g++3.4.2好像有点老)中,新建工程时出现选择console application(控制台应用程序)即可建立平时大家用的C程序的工程,典型特征是有个唯一的main函数,生成exe可执行文件。

选择dll即可建立动态链接库工程,运行会生成dll而不是exe。

CodeLite6.1.1(g++4.8.1)中需要先建立wrokspace工作区,再在其中建立project工程,注意选择路径。

建立工程时,会选择工程类型。

选择console下的g++即可建立C++工程,选择gcc即可建立C工程,其他选项也可以自己尝试。

选择library下的Dynamic library即可建立动态链接库工程,工程最终生成dll文件。

Linux环境下的IDE操作方式也差不多,这里以Ubuntu13.10下的Code::Block12.10为例选择Console application即可建立可执行文件工程,选择Shared library即可建立动态链接库工程。

生成你的工程写好你的程序之后,选择编译即可编译你的源代码,选择运行即可生成对应的可执行文件或者动态链接库。

gcc编译打印详细1.引言1.1 概述在编译程序时,gcc是一种常用的编译器,它具有强大的功能和广泛的应用。

gcc编译器不仅可以将源代码翻译成可执行程序,还可以通过一系列选项进行配置和优化,以满足开发者的需求。

然而,在开发过程中,有时候我们需要更加详细的编译信息来帮助我们定位问题或者优化程序。

本文将重点介绍如何通过gcc的编译选项来打印详细的编译信息。

本文主要包括以下几个方面内容。

首先,我们将简要介绍gcc编译器的一些基本知识,包括它的功能和特点。

然后,我们会详细介绍gcc的编译选项,包括常用的选项和其作用。

接着,我们将通过实例来演示如何使用这些选项来打印详细的编译信息。

最后,我们会总结gcc编译打印详细的意义和应用,并给出一些建议。

通过本文的学习,读者可以更加深入地了解gcc编译器的使用方法,掌握如何使用gcc的编译选项来打印详细的编译信息。

同时,读者还可以进一步探索gcc编译器的其他高级特性,以提高程序的性能和质量。

本文适用于具有一定编程基础的读者,希望能够帮助读者更好地理解和应用gcc编译器。

同时,本文也是一个详细的参考文档,读者可以随时查阅相关内容。

下一节将进一步介绍本文的结构和目标,希望读者能够跟随文章的逻辑来更好地理解和应用gcc编译打印详细的技巧。

1.2 文章结构本文主要围绕着gcc编译器的详细打印展开,以便更好地了解gcc编译过程中的细节。

下面是本文的大致结构。

第一部分是引言部分,其中包括概述、文章结构和目的。

在概述部分,将简要介绍gcc编译器的基本概念和作用。

然后,在文章结构部分,将详细说明本文的整个结构和各个部分的内容。

最后,目的部分将说明本文撰写的目标和意义。

第二部分是正文部分,主要分为两个小节,分别介绍gcc编译器的概述和gcc编译选项。

在gcc编译器介绍部分,将详细介绍gcc编译器的起源、特点和使用场景。

然后,在gcc编译选项部分,将系统地介绍gcc编译器中常用的编译选项,以及它们的作用和用法。

GCC(GNU Compiler Collection)是一种广泛使用的编译器,支持多种编程语言,包括C、C++、Objective-C、Fortran、Ada等。

GCC手册是一个全面的指南,涵盖了从基础概念到高级优化的所有方面。

手册首先介绍了GCC的基本概念和安装方法,以及如何使用其基本编译选项。

然后,它深入探讨了GCC的各个功能,包括优化选项、并行编译、与特定语言的交互等。

此外,手册还涵盖了关于GCC如何处理代码生成、优化和调试的信息,这些都是开发人员在实际应用中非常关心的主题。

总的来说,GCC手册是一个宝贵的资源,无论是初学者还是经验丰富的开发人员都能从中受益。

通过阅读这本手册,用户可以更好地理解GCC的工作原理,并利用其强大的功能来提高代码质量和性能。

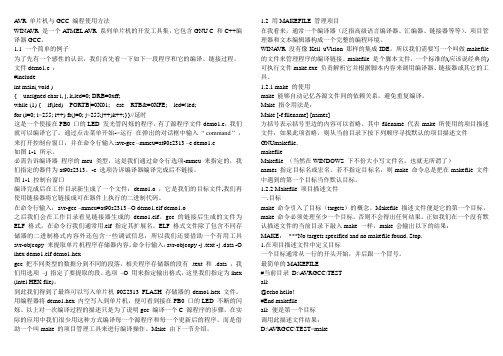

A VR 单片机与GCC 编程使用方法WINA VR 是一个ATMEL A VR 系列单片机的开发工具集,它包含GNU C 和C++编译器GCC。

1.1 一个简单的例子为了先有一个感性的认识,我们首先看一下如下一段程序和它的编译、链接过程。

文件demo1.c :#includeint main( void ){ unsigned char i, j, k,led=0; DRB=0xff;while (1) { if(led) PORTB|=0X01; ese RTB&=0XFE; led=!led;for (i=0; i<255; i++) fr(j=0; j<255;j++)k++;}}//延时这是一个使接在PB0 口的LED 发光管闪烁的程序。

有了源程序文件demo1.c,我们就可以编译它了。

通过点击菜单开始->运行在弹出的对话框中输入― command ‖ ,来打开控制台窗口,并在命令行输入:avr-gcc –mmcu=at90s2313 –c demo1.c如图1-1 所示。

必需告诉编译器程序的mcu 类型,这是我们通过命令行选项-mmcu 来指定的,我们指定的器件为at90s2313。

-c 选项告诉编译器编译完成后不链接。

图1-1 控制台窗口编译完成后在工作目录新生成了一个文件:demo1.o ,它是我们的目标文件,我们再使用链接器将它链接成可在器件上执行的二进制代码。

在命令行输入:avr-gcc –mmcu=at90s2313 –O demo1.elf demo1.o之后我们会在工作目录看见链接器生成的demo1.elf。

gcc 的链接后生成的文件为ELF 格式,在命令行我们通常用.elf 指定其扩展名。

ELF 格式文件除了包含不同存储器的二进制格式内容外还包含一些调试信息,所以我们还要借助一个有用工具avr-objcopy 来提取单片机程序存储器内容。

命令行输入:avr-objcopy -j .text -j .data -O ihex demo1.elf demo1.hexgcc 把不同类型的数据分到不同的段落,相关程序存储器的段有.text 和.data ,我们用选项–j 指定了要提取的段。

高级语言程序设计(c语言)高级语言程序设计(C语言)C语言是一种高级的程序设计语言,广泛应用于软件开发、嵌入式系统和科学计算等领域。

本文将从C语言的基础知识、语法结构、常用函数和应用实例等方面进行论述,帮助读者更好地理解和应用C语言。

一、C语言的基础知识1. C语言简介C语言是由贝尔实验室的Dennis Ritchie于20世纪70年代开发的,它具有高效性、可移植性和灵活性的特点。

C语言提供了丰富的功能和库函数,可以实现底层硬件的访问和高级算法的编写。

2. 开发环境的搭建在开始学习C语言之前,我们需要配置开发环境。

常用的C语言开发环境包括GCC、Visual Studio和Code::Blocks等,选取适合自己的集成开发环境(IDE)进行安装和配置。

二、C语言的语法结构1. 变量和数据类型在C语言中,变量是用来存储和操作数据的。

通过定义变量的名称和类型,我们可以为不同类型的数据分配内存空间,并对其进行读写操作。

常见的数据类型包括整型、浮点型、字符型和指针型等。

2. 运算符和表达式运算符是C语言中用于进行各种数学和逻辑运算的符号。

通过使用运算符,我们可以实现加减乘除、位操作和条件判断等功能。

表达式是由运算符和操作数组成的,通过对表达式的计算可以得到一个具体的值。

3. 控制语句控制语句用于控制程序的执行流程,根据不同的条件执行不同的代码块。

常用的控制语句包括条件语句(if-else)、循环语句(for、while、do-while)和跳转语句(break、continue、goto)等。

三、C语言的常用函数1. 输入输出函数C语言提供了多个输入输出函数,用于从键盘读取数据和向屏幕输出结果。

常用的输入函数有scanf()和gets(),用于读取用户输入的数据;输出函数有printf()和puts(),用于将结果打印到屏幕上。

2. 字符串函数字符串是由字符组成的数组,在C语言中提供了一系列用于处理字符串的函数。

C语言中的调试技巧与工具使用C语言是一种广泛应用于软件开发和系统编程的高级编程语言。

在日常的编程工作中,我们经常会遇到无法预料的bug和错误,这时候我们就需要使用调试技巧和工具来定位和解决问题。

在本文中,我将介绍一些C语言中常用的调试技巧和工具的使用方法。

一、断点调试断点是调试代码时非常实用的工具。

通过在代码中设置断点,我们可以暂停程序的执行,查看当前变量的值,检查代码的执行路径等。

在C语言中,可以使用调试器来设置断点并进行调试。

1. 使用GDB调试器GDB是一款功能强大的开源调试器,可用于调试C和C++程序。

下面是一些常用的GDB调试命令:- "break 文件名:行号":在指定的文件和行号处设置断点。

- "run":运行程序直到遇到第一个断点。

- "next":执行下一行代码。

- "step":进入函数调用并且停在函数的第一行。

- "print 变量名":打印变量的值。

- "continue":继续执行直到下一个断点或程序结束。

2. 使用LLDB调试器LLDB是另一种流行的调试器,它支持多种编程语言,包括C语言。

以下是一些常用的LLDB调试命令:- "b 文件名:行号":在指定的文件和行号处设置断点。

- "r":运行程序直到遇到第一个断点。

- "n":执行下一行代码。

- "s":进入函数调用并且停在函数的第一行。

- "p 变量名":打印变量的值。

- "c":继续执行直到下一个断点或程序结束。

二、代码注释与输出调试代码注释和输出调试是我们在日常编程中常用的调试技巧。

通过在代码中添加注释和输出语句,我们可以更好地理解程序的执行流程,以及在某个过程中变量的值。

1. 代码注释在C语言中,可以使用 "//" 进行单行注释,使用 "/* */" 进行多行注释。

GCCP6操作快速指南1. 准备工作在开始使用GCCP6之前,请确保您的开发环境满足以下要求:- 安装Java JDK 1.8或以上版本- 安装Maven 3.6或以上版本- 安装Git 2.14或以上版本- 配置好SSH密钥,以便于使用Git进行代码管理2. 创建项目在GCCP6平台上创建项目,请按照以下步骤进行:1. 登录GCCP6平台。

如果您还没有账号,请先注册。

2. 在主页面点击“创建项目”按钮。

3. 填写项目名称、描述和选择项目模板。

4. 选择云服务提供商(如阿里云、腾讯云等)。

5. 配置项目环境,如CPU、内存、存储等。

6. 点击“创建项目”按钮,等待项目创建完成。

3. 开发应用在项目创建完成后,您可以开始开发云原生应用。

以下是基本的开发流程:1. 编写代码:使用您熟悉的编程语言(如Java、Python等)编写应用代码。

2. 构建项目:使用Maven或Gradle等构建工具进行项目构建。

3. 测试应用:在本地环境进行单元测试和集成测试。

4. 打包应用:将应用打包成适合在云端运行的格式,如Docker 镜像。

4. 部署应用将编写和测试好的应用部署到GCCP6平台,请遵循以下步骤:1. 上传镜像:在GCCP6平台的镜像管理中上传打包好的Docker镜像。

2. 创建服务:在GCCP6平台的服务管理中创建一个新的服务。

3. 配置服务:选择刚刚上传的镜像,配置服务所需的CPU、内存、存储等资源。

4. 部署服务:点击“部署”按钮,GCCP6平台将自动创建所需资源并部署应用。

5. 管理应用在应用部署后,您需要对其进行管理和监控,以确保其稳定运行。

以下是管理应用的基本方法:1. 监控应用:在GCCP6平台的监控管理中查看应用的运行状态、CPU使用率、内存使用情况等。

2. 日志管理:在日志管理中查看应用的输出日志,以便于排查问题和定位故障。

3. 更新和扩缩容:根据需求对应用进行更新和扩缩容操作。

6. 清理资源当您完成应用的开发、部署和管理后,请确保清理所有使用的资源,以避免产生不必要的费用。

Linux编程起步 GCC基本用法初学时最好从命令行入手,这样可以熟悉从编写程序、编译、调试和执行的整个过程。

编写程序可以用vi或其它编辑器编写。

编译则使用GCC命令。

要往下学习首先就得熟悉GCC命令的用法。

GCC命令提供了非常多的命令选项,但并不是所有都要熟悉,初学时掌握几个常用的就可以了,到后面再慢慢学习其它选项,免得因选项太多而打击了学习的信心。

一. 常用编译命令选项假设源程序文件名为test.c。

1. 无选项编译链接用法:#gcc test.c作用:将test.c预处理、汇编、编译并链接形成可执行文件。

这里未指定输出文件,默认输出为a.out。

2. 选项 -o用法:#gcc test.c -o test作用:将test.c预处理、汇编、编译并链接形成可执行文件test。

-o选项用来指定输出文件的文件名。

3. 选项 -E用法:#gcc -E test.c -o test.i作用:将test.c预处理输出test.i文件。

4. 选项 -S用法:#gcc -S test.i作用:将预处理输出文件test.i汇编成test.s文件。

5. 选项 -c用法:#gcc -c test.s作用:将汇编输出文件test.s编译输出test.o文件。

6. 无选项链接用法:#gcc test.o -o test作用:将编译输出文件test.o链接成最终可执行文件test。

7. 选项-O用法:#gcc -O1 test.c -o test作用:使用编译优化级别1编译程序。

级别为1~3,级别越大优化效果越好,但编译时间越长。

二. 多源文件的编译方法如果有多个源文件,基本上有两种编译方法:[假设有两个源文件为test.c和testfun.c]1. 多个文件一起编译用法:#gcc testfun.c test.c -o test作用:将testfun.c和test.c分别编译后链接成test可执行文件。

2. 分别编译各个源文件,之后对编译后输出的目标文件链接。

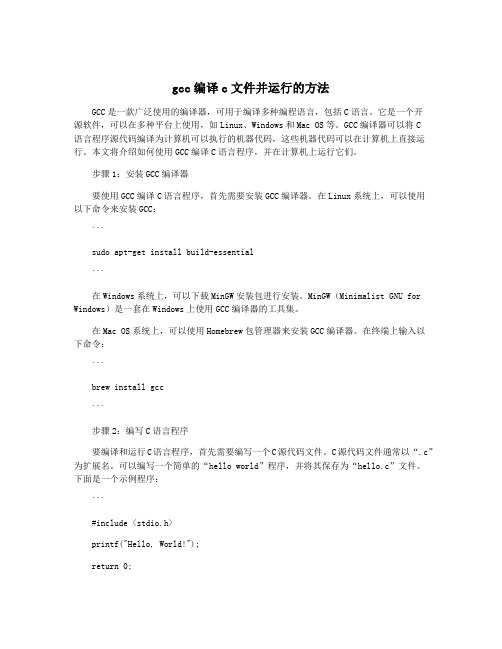

gcc编译c文件并运行的方法GCC是一款广泛使用的编译器,可用于编译多种编程语言,包括C语言。

它是一个开源软件,可以在多种平台上使用,如Linux、Windows和Mac OS等。

GCC编译器可以将C语言程序源代码编译为计算机可以执行的机器代码,这些机器代码可以在计算机上直接运行。

本文将介绍如何使用GCC编译C语言程序,并在计算机上运行它们。

步骤1:安装GCC编译器要使用GCC编译C语言程序,首先需要安装GCC编译器。

在Linux系统上,可以使用以下命令来安装GCC:```sudo apt-get install build-essential```在Windows系统上,可以下载MinGW安装包进行安装。

MinGW(Minimalist GNU for Windows)是一套在Windows上使用GCC编译器的工具集。

在Mac OS系统上,可以使用Homebrew包管理器来安装GCC编译器。

在终端上输入以下命令:```brew install gcc```步骤2:编写C语言程序要编译和运行C语言程序,首先需要编写一个C源代码文件。

C源代码文件通常以“.c”为扩展名。

可以编写一个简单的“hello world”程序,并将其保存为“hello.c”文件。

下面是一个示例程序:```#include <stdio.h>printf("Hello, World!");return 0;}```步骤3:使用GCC编译器编译C语言程序一旦编写好了C语言程序,就可以使用GCC编译器将其编译为可执行程序。

在终端上,进入C语言程序所在目录,并使用以下命令编译程序:```gcc -o hello hello.c```在这个命令中,“-o”参数指定编译器编译完后生成的可执行文件的名称。

在本例中,编译器将生成一个名为“hello”的可执行文件。

步骤4:运行已编译的C语言程序执行上述编译命令后,GCC编译器将生成一个可执行文件。

gccstrip参数

使用gccstrip参数可以减小可执行文件或共享库的大小,从而节省存储空间,同时也可以提高程序的运行速度。

在命令行中,可以通过"-s"或"--strip-all"选项来告诉GCC去除所有符号表和调试信息。

另外,还可以使用"-g"选项来指定保留调试信息或者"-S"选项来指定只去除符号表而保留调试信息。

需要注意的是,使用gccstrip参数可能会使得调试变得困难,因为去除了符号表和调试信息。

因此,在开发阶段通常不建议使用gccstrip参数,而是在发布产品时再使用它来优化可执行文件或共享库。

gcc的基本使⽤编译gcc⽂件在hello_world.c⽂件中有如下代码:#include <stdio.h>int main() {int i;printf("Hello world!\n");}在终端中输⼊:gcc hello_world.c这样hello_world.c⽂件所在的⽂件夹中编译出了叫做a.out的可执⾏程序,但是如果我们不想让编译出来的可执⾏程序叫做a.out,我们可以通过-o选项来指定编译出来的可执⾏⽂件的名字:gcc hello_world.c -o hello_world这样我们编译出来得到的可执⾏⽂件名就是hello_world,我们可以通过./hello_world来执⾏它。

让gcc输出警告在默认情况下gcc会忽略⼀些低等级的警告,但这些警告往往能帮助我们找到程序中的问题。

通过在编译的时候添加-Wall就可以让gcc输出全部的警告信息,按实际情况对程序进⾏修改。

gcc -Wall hello_world.c -o hello_world这时程序会报warning:hello_world.c: In function ‘main’:hello_world.c:6:9: warning: unused variable ‘i’ [-Wunused-variable]int i;^这个警告是说,我们声明了变量i但是却没有使⽤它。

类似的这种警告是⾮常好⽤的,程序出现问题后我们可以根据这种提⽰顺藤摸⽠地找到问题的根源。

程序优化在gcc中有⼀个-O选项,后⾯会跟⼀个字符,例如-O2,-Os,-O0,-Og等代表不同的优化等级。

不同的优化等级有不同的侧重点。

对于-O0,-O1,-O2,-O3这四种优化⼤家可以这样认为,在⼤部分情况下,数字越⼤优化等级越⾼,程序运⾏效率越⾼,但是编译出来的⽂件⼤⼩也会越⼤,可以理解为⽤空间换时间。

-O2优化-O2优化⾮常好的平衡了程序的性能与程序最后的⼤⼩;gcc -Wall -O2 hello_world.c -o hello_world-Os优化-Os优化与-O2相似,它只是把⼀些通过增⼤程序⼤⼩从⽽提⾼程序运⾏速度的优化⼿段给禁⽤了;gcc -Wall -Os hello_world.c -o hello_world-Og优化通常在在开启优化之后,源码中的⼀些代码可能被编译器优化掉了,那么这些代码在最终的程序中并不存在。

Gcc参数高级应用1.Gcc对ARM的优化/onlinedocs/gcc/ARM-Options.htmlARM OptionsThese `-m' options are defined for Advanced RISC Machines (ARM) architectures:-mabi=nameGenerate code for the specified ABI. Permissible values are: `apcs-gnu', `atpcs', `aapcs', `aapcs-linux' and `iwmmxt'.-mapcs-frameGenerate a stack frame that is compliant with the ARM Procedure Call Standard for all functions, even if this is not strictly necessary for correct execution of the code. Specifying -fomit-frame-pointer with this option will cause the stack frames not to be generated for leaf functions. The default is -mno-apcs-frame.-mapcsThis is a synonym for -mapcs-frame.-mthumb-interworkGenerate code which supports calling between the ARM and Thumb instruction sets. Without this option, on pre-v5 architectures, the two instruction sets cannot be reliably used inside one program. The default is -mno-thumb-interwork, since slightly larger code is generated when -mthumb-interwork is specified. In AAPCS configurations this option is meaningless.-mno-sched-prologPrevent the reordering of instructions in the function prolog, or the merging of those instruction with the instructions in the function's body. This means that all functions will start with a recognizable set of instructions (or in fact one of a choice from a small set of different function prologues), and this information can be used to locate the start if functions inside an executable piece of code. The default is -msched-prolog.-mfloat-abi=nameSpecifies which floating-point ABI to use. Permissible values are: `soft', `softfp' and `hard'. Specifying `soft' causes GCC to generate output containing library calls for floating-point operations. `softfp' allows the generation of code using hardware floating-point instructions, but still uses the soft-float calling conventions. `hard' allows generation of floating-point instructions and uses FPU-specific calling conventions.The default depends on the specific target configuration. Note that the hard-float and soft-float ABIs are not link-compatible; you must compile your entire program with the same ABI, and linkwith a compatible set of libraries.-mlittle-endianGenerate code for a processor running in little-endian mode. This is the default for all standard configurations.-mbig-endianGenerate code for a processor running in big-endian mode; the default is to compile code for a little-endian processor.-mwords-little-endianThis option only applies when generating code for big-endian processors. Generate code for a little-endian word order but a big-endian byte order. That is, a byte order of the form `32107654'. Note: this option should only be used if you require compatibility with code for big-endian ARM processors generated by versions of the compiler prior to 2.8. This option is now deprecated.-mcpu=nameThis specifies the name of the target ARM processor. GCC uses this name to determine what kind of instructions it can emit when generating assembly code. Permissible names are: `arm2', `arm250', `arm3', `arm6', `arm60', `arm600', `arm610', `arm620', `arm7', `arm7m', `arm7d', `arm7dm', `arm7di', `arm7dmi', `arm70', `arm700', `arm700i', `arm710', `arm710c', `arm7100', `arm720', `arm7500', `arm7500fe', `arm7tdmi', `arm7tdmi-s', `arm710t', `arm720t', `arm740t', `strongarm', `strongarm110', `strongarm1100', `strongarm1110', `arm8', `arm810', `arm9', `arm9e', `arm920', `arm920t', `arm922t', `arm946e-s', `arm966e-s', `arm968e-s', `arm926ej-s', `arm940t', `arm9tdmi', `arm10tdmi', `arm1020t', `arm1026ej-s', `arm10e', `arm1020e', `arm1022e', `arm1136j-s', `arm1136jf-s', `mpcore', `mpcorenovfp', `arm1156t2-s', `arm1156t2f-s', `arm1176jz-s', `arm1176jzf-s', `cortex-a5', `cortex-a8', `cortex-a9', `cortex-a15', `cortex-r4', `cortex-r4f', `cortex-r5', `cortex-m4', `cortex-m3', `cortex-m1', `cortex-m0', `xscale', `iwmmxt', `iwmmxt2', `ep9312', `fa526', `fa626', `fa606te', `fa626te', `fmp626', `fa726te'.-mtune=nameThis option is very similar to the -mcpu= option, except that instead of specifying the actual target processor type, and hence restricting which instructions can be used, it specifies that GCC should tune the performance of the code as if the target were of the type specified in this option, but still choosing the instructions that it will generate based on the CPU specified by a -mcpu= option. For some ARM implementations better performance can be obtained by using this option.-march=nameThis specifies the name of the target ARM architecture. GCC uses this name to determine what kind of instructions it can emit when generating assembly code. This option can be used in conjunction with or instead of the -mcpu= option. Permissible names are: `armv2', `armv2a', `armv3', `armv3m', `armv4', `armv4t', `armv5', `armv5t', `armv5e', `armv5te', `armv6', `armv6j',`armv6t2', `armv6z', `armv6zk', `armv6-m', `armv7', `armv7-a', `armv7-r', `armv7-m', `iwmmxt', `iwmmxt2', `ep9312'.-mfpu=name-mfpe=number-mfp=numberThis specifies what floating point hardware (or hardware emulation) is available on the target. Permissible names are: `fpa', `fpe2', `fpe3', `maverick', `vfp', `vfpv3', `vfpv3-fp16', `vfpv3-d16', `vfpv3-d16-fp16', `vfpv3xd', `vfpv3xd-fp16', `neon', `neon-fp16', `vfpv4', `vfpv4-d16', `fpv4-sp-d16' and `neon-vfpv4'. -mfp and -mfpe are synonyms for -mfpu=`fpe'number, for compatibility with older versions of GCC.If -msoft-float is specified this specifies the format of floating point values.If the selected floating-point hardware includes the NEON extension (e.g. -mfpu=`neon'), note that floating-point operations will not be used by GCC's auto-vectorization pass unless -funsafe-math-optimizations is also specified. This is because NEON hardware does not fully implement the IEEE 754 standard for floating-point arithmetic (in particular denormal values are treated as zero), so the use of NEON instructions may lead to a loss of precision.-mfp16-format=nameSpecify the format of the __fp16 half-precision floating-point type. Permissible names are `none', `ieee', and `alternative'; the default is `none', in which case the __fp16 type is not defined. See Half-Precision, for more information.-mstructure-size-boundary=nThe size of all structures and unions will be rounded up to a multiple of the number of bits set by this option. Permissible values are 8, 32 and 64. The default value varies for different toolchains. For the COFF targeted toolchain the default value is 8. A value of 64 is only allowed if the underlying ABI supports it.Specifying the larger number can produce faster, more efficient code, but can also increase the size of the program. Different values are potentially incompatible. Code compiled with one value cannot necessarily expect to work with code or libraries compiled with another value, if they exchange information using structures or unions.-mabort-on-noreturnGenerate a call to the function abort at the end of a noreturn function. It will be executed if the function tries to return.-mlong-calls-mno-long-callsTells the compiler to perform function calls by first loading the address of the function into a register and then performing a subroutine call on this register. This switch is needed if the targetfunction will lie outside of the 64 megabyte addressing range of the offset based version of subroutine call instruction.Even if this switch is enabled, not all function calls will be turned into long calls. The heuristic is that static functions, functions which have the `short-call' attribute, functions that are inside the scope of a `#pragma no_long_calls' directive and functions whose definitions have already been compiled within the current compilation unit, will not be turned into long calls. The exception to this rule is that weak function definitions, functions with the `long-call' attribute or the `section' attribute, and functions that are within the scope of a `#pragma long_calls' directive, will always be turned into long calls.This feature is not enabled by default. Specifying -mno-long-calls will restore the default behavior, as will placing the function calls within the scope of a `#pragma long_calls_off' directive. Note these switches have no effect on how the compiler generates code to handle function calls via function pointers.-msingle-pic-baseTreat the register used for PIC addressing as read-only, rather than loading it in the prologue for each function. The run-time system is responsible for initializing this register with an appropriate value before execution begins.-mpic-register=regSpecify the register to be used for PIC addressing. The default is R10 unless stack-checking is enabled, when R9 is used.-mcirrus-fix-invalid-insnsInsert NOPs into the instruction stream to in order to work around problems with invalid Maverick instruction combinations. This option is only valid if the -mcpu=ep9312 option has been used to enable generation of instructions for the Cirrus Maverick floating point co-processor. This option is not enabled by default, since the problem is only present in older Maverick implementations. The default can be re-enabled by use of the -mno-cirrus-fix-invalid-insns switch.-mpoke-function-nameWrite the name of each function into the text section, directly preceding the function prologue. The generated code is similar to this:t0.ascii "arm_poke_function_name", 0.alignt1.word 0xff000000 + (t1 - t0)arm_poke_function_namemov ip, spstmfd sp!, {fp, ip, lr, pc}sub fp, ip, #4When performing a stack backtrace, code can inspect the value of pc stored at fp + 0. If the trace function then looks at location pc - 12 and the top 8 bits are set, then we know that there is a function name embedded immediately preceding this location and has length ((pc[-3]) & 0xff000000).-mthumb-marmSelect between generating code that executes in ARM and Thumb states. The default for most configurations is to generate code that executes in ARM state, but the default can be changed by configuring GCC with the --with-mode=state configure option.-mtpcs-frameGenerate a stack frame that is compliant with the Thumb Procedure Call Standard for all non-leaf functions. (A leaf function is one that does not call any other functions.) The default is -mno-tpcs-frame.-mtpcs-leaf-frameGenerate a stack frame that is compliant with the Thumb Procedure Call Standard for all leaf functions. (A leaf function is one that does not call any other functions.) The default is -mno-apcs-leaf-frame.-mcallee-super-interworkingGives all externally visible functions in the file being compiled an ARM instruction set header which switches to Thumb mode before executing the rest of the function. This allows these functions to be called from non-interworking code. This option is not valid in AAPCS configurations because interworking is enabled by default.-mcaller-super-interworkingAllows calls via function pointers (including virtual functions) to execute correctly regardless of whether the target code has been compiled for interworking or not. There is a small overhead in the cost of executing a function pointer if this option is enabled. This option is not valid in AAPCS configurations because interworking is enabled by default.-mtp=nameSpecify the access model for the thread local storage pointer. The valid models are soft, which generates calls to __aeabi_read_tp, cp15, which fetches the thread pointer from cp15 directly (supported in the arm6k architecture), and auto, which uses the best available method for the selected processor. The default setting is auto.-mtls-dialect=dialectSpecify the dialect to use for accessing thread local storage. Two dialects are supported — gnuand gnu2. The gnu dialect selects the original GNU scheme for supporting local and global dynamic TLS models. The gnu2 dialect selects the GNU descriptor scheme, which provides better performance for shared libraries. The GNU descriptor scheme is compatible with the original scheme, but does require new assembler, linker and library support. Initial and local exec TLS models are unaffected by this option and always use the original scheme.-mword-relocationsOnly generate absolute relocations on word sized values (i.e. R_ARM_ABS32). This is enabled by default on targets (uClinux, SymbianOS) where the runtime loader imposes this restriction, and when -fpic or -fPIC is specified.-mfix-cortex-m3-ldrdSome Cortex-M3 cores can cause data corruption when ldrd instructions with overlapping destination and base registers are used. This option avoids generating these instructions. This option is enabled by default when -mcpu=cortex-m3 is specified.2.gcc常用参数-Wa,<选项> 将逗号分隔的<选项> 传递给汇编器-Wp,<选项> 将逗号分隔的<选项> 传递给预处理器-Wl,<选项> 将逗号分隔的<选项> 传递给链接器-Xassembler <参数> 将<参数> 传递给汇编器-Xpreprocessor <参数> 将<参数> 传递给预处理器-Xlinker <参数> 将<参数> 传递给链接器-save-temps 不删除中间文件-save-temps=<arg> 不删除中间文件-no-canonical-prefixes 生成其他gcc 组件的相对路径时不生成规范化的前缀-pipe 使用管道代替临时文件-time 为每个子进程计时-specs=<文件> 用<文件> 的内容覆盖内建的specs 文件-std=<标准> 指定输入源文件遵循的标准--sysroot=<目录> 将<目录> 作为头文件和库文件的根目录-B <目录> 将<目录> 添加到编译器的搜索路径中-v 显示编译器调用的程序-### 与-v 类似,但选项被引号括住,并且不执行命令-E 仅作预处理,不进行编译、汇编和链接-S 编译到汇编语言,不进行汇编和链接-c 编译、汇编到目标代码,不进行链接-o <文件> 输出到<文件>-x <语言> 指定其后输入文件的语言允许的语言包括:c c++ assembler none‘none’意味着恢复默认行为,即根据文件的扩展名猜测源文件的语言以-g、-f、-m、-O、-W 或--param 开头的选项将由gcc 自动传递给其调用的不同子进程。