万年历时钟表

- 格式:docx

- 大小:2.03 MB

- 文档页数:20

2024年10月

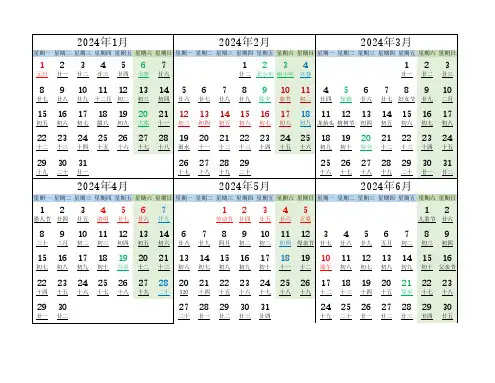

2024年,是公历闰年,共366天、53周。

农历甲辰年(龙年),无闰月,共354天,农历起止日期为2024年2月10日—2025年1月28日。

2024年假日安排

一、元旦:1月1日放假,与周末连休。

二、春节:2月10日至17日放假调休,共8天。

2月4日(星期日)、2月18日(星期日)上班。

鼓励各单位结合带薪年休假等制度落实,安排职工在除夕(2月9日)休息。

三、清明节:4月4日至6日放假调休,共3天。

4月7日(星期日)上班。

四、劳动节:5月1日至5日放假调休,共5天。

4月28日(星期日)、5月11日(星期六)上班。

五、端午节:6月10日放假,与周末连休。

六、中秋节:9月15日至17日放假调休,共3天。

9月14日(星期六)上班。

七、国庆节:10月1日至7日放假调休,共7天。

9月29日(星期日)、10月12日(星期六)上班。

一、实训目的本次万年历时钟实训的主要目的是通过实际操作,学习万年历时钟的设计与制作,掌握万年历时钟的原理和制作方法,提高动手实践能力和创新思维。

实训过程中,我们学习了万年历时钟的硬件组成、软件编程、电路设计等知识,并对万年历时钟进行了实际制作。

二、实训内容1. 万年历时钟硬件组成万年历时钟主要由以下几部分组成:(1)单片机:作为万年历时钟的核心控制器,负责处理时间、日期、温度等数据,并控制整个时钟的运行。

(2)DS1302实时时钟模块:用于存储和提供当前时间、日期等信息。

(3)DS18B20温度传感器:用于检测环境温度。

(4)LCD12864液晶显示屏:用于显示时间、日期、温度等信息。

(5)按键:用于设置和调整时间、日期、温度等信息。

2. 万年历时钟软件编程万年历时钟的软件编程主要包括以下几部分:(1)主程序:负责初始化硬件设备,处理时间、日期、温度等数据,控制LCD显示。

(2)时钟模块:负责读取DS1302模块中的时间、日期信息,并实现时钟功能。

(3)温度模块:负责读取DS18B20传感器中的温度信息,并实现温度显示功能。

(4)按键处理模块:负责处理按键输入,实现时间、日期、温度的设置和调整。

3. 万年历时钟电路设计万年历时钟的电路设计主要包括以下几部分:(1)单片机与DS1302模块的连接:通过I2C接口连接单片机与DS1302模块,实现时间、日期信息的读取和写入。

(2)单片机与DS18B20传感器的连接:通过1-Wire接口连接单片机与DS18B20传感器,实现温度信息的读取。

(3)单片机与LCD12864显示屏的连接:通过SPI接口连接单片机与LCD12864显示屏,实现显示信息的输出。

(4)按键与单片机的连接:通过GPIO接口连接按键与单片机,实现按键输入的处理。

三、实训过程1. 硬件准备首先,准备好万年历时钟所需的硬件设备,包括单片机、DS1302模块、DS18B20传感器、LCD12864显示屏、按键等。

万年历数字钟及可调时钟系统一、引言万年历数字钟是一种用万年历时钟芯片实现年、月、日、时、分、秒计时,并通过单片机处理后送给显示芯片显示的装置,与机械式时钟相比具有更高的准确性和直观性,且具有更长的使用寿命。

本系统还可以扩展为可调的自动开关,对家电对用电设备进行控制,笔者在随后改制成为可调时的自动断电的供电系统.二、原理图设计1.单片机及其外围电路设计复位采用X25045芯片,复位电路如图1所示。

图1 复位电路设计单片机采用贴片封装的AT89S51,晶振为11.0592MHz。

其中P1.5~P1.7为下载程序使用,电路如图2所示。

图2 单片机89S51外围电路设计2.时钟芯片电路设计时钟芯片采用PCF8563,晶振采用32.768K,电容使用15pf。

PCF8563 是PHILIPS 公司推出的一款工业级内含I2C 总线接口功能的具有极低功耗的多功能时钟/日历芯片。

内部时钟电路、内部振荡电路、内部低电压检测电路(1.0V)以及两线制I2C 总线通讯方式,不但使外围电路及其简洁,而且也增加了芯片的可靠性。

同时每次读写数据后,内嵌的字地址寄存器会自动产生增量。

电路如图3所示。

图3 时钟芯片电路设计3.显示芯片电路设计显示芯片采用ZLG7289,晶振为12MHz。

ZLG7289A 是广州周立功单片机发展有限公司自行设计的,具有SPI 串行接口功能的可同时驱动8 位共阴式数码管(或64 只独立LED )的智能显示驱动芯片,该芯片同时还可连接多达64 键的键盘矩阵,单片即可完成LED 显示﹑键盘接口的全部功能。

电路如图4所示。

图4 显示芯片电路设计4.双电源电路设计系统采用双电源,平时使用V1=10V的外接电源,停电时使用电池,由V2输入。

电池有6节,其电压为9V。

当电池电压低于6V时,LED亮,说明电池电量不足。

电路如图5所示。

图5 双电源电路设计三、程序设计程序开始时先对系统初始化,并设置好各种中断。

下步操作主要是对时钟芯片进行操作,首先要给时钟芯片设置初值,时钟芯片便自行计数。

《嵌入式课程设计》讲义项目1 智能数字万年历一.项目指标分析项目指标要求如下:1. 显示年、月、日、时、分、秒和星期。

2. 实时显示温度。

3. 可手动调整时间。

4. 采用LCD显示。

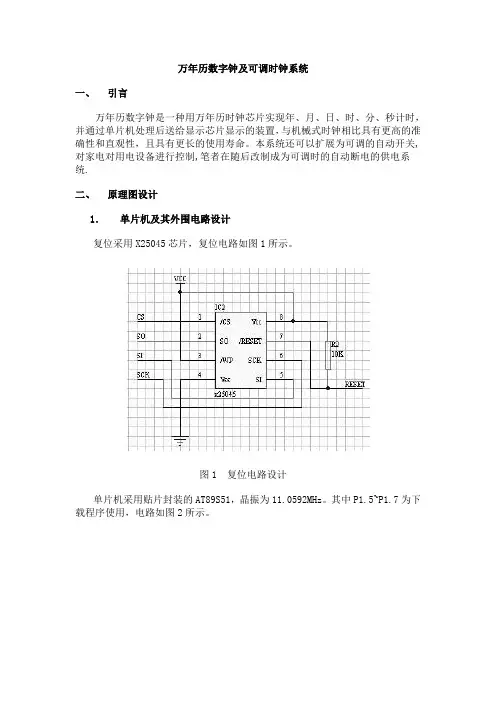

基于以上要求,核心控制芯片选用STC89C51;时钟芯片选用DS1302;温度传感器选用DS18B20;液晶屏选用LCD1602;设置按键,以便于调整时间。

二.电路原理系统电路功能图如图1所示:图1 智能数字万年历电路功能图由图1可知,P2口控制LCD的数据端;P3.5、P3.6和P3.7控制着LCD的片选、读/写和寄存器选择信号;可调电阻RP2用于调节屏的显示对比度。

P3.4是温度传感器DS18B20的1-wire接口,即片选、时钟和数据信号均由P3.4口控制。

P0.5、P0.6和P0.7是时钟芯片DS1302的SPI接口,为使信号控制更稳定,这三个接口上都上拉了10KΩ电阻;为获得精准的时钟信号,选用频率为32.768KHz的外部晶振对DS1302提供振荡信号。

P0.0-P0.3控制着四个按键,以便于调整时间。

三.程序设计基于这个项目,程序的设计可分成各芯片驱动程序设计和控制算法程序两部分。

1.各芯片的驱动程序设计在写驱动程序时,首先通读芯片手册,以掌握主要技术指标;然后可按照以下3个步骤进行:(1)分清楚各芯片的通信属于哪种接口方式,例如:时钟芯片DS1302按照SPI 接口进行通信;温度传感器DS18B20按照1-wire接口进行通信;液晶屏LCD1602采用常规的并行数据传输方式。

(2)仔细分析芯片时序图,弄清楚片选信号是高电平有效还是低电平有效;数据是在时钟信号的上升沿还是下降沿时打入;数据前还是时钟前等。

(3)将功能程序函数化、驱动程序模块化。

2.控制算法程序设计这里的算法主要集中在如何设置按键识别程序,即便于调整时间,又不影响液晶屏的显示。

这里,提供两种思想以便参考。

(1)循环扫描方式流程图图2 循环扫描方式流程图(2图3 状态机方式流程图将图2和图3比较起来看,两种方式的最大差别在于“10ms消抖时间如何度过?”。

基于单片机的万年历设计摘要随着社会、科技的发展,人类得知时间,从观太阳、摆钟到现在电子钟,不断研究、创新。

为了在观测时间的同时,能够了解其它与人类密切相关的信息,比如温度、星期、日期等,电子万年历诞生了,它集时间、日期、星期和温度功能于一身,具有读取方便、显示直观、功能多样、电路简洁等诸多优点,符合电子仪器仪表的发展趋势,具有广阔的市场前景。

该电子万年历主要采用AT89C55WD单片机作为主控核心,由DS1302时钟芯片提供时钟、LED动态扫描显示屏显示。

AT89C55WD单片机是由Atmel 公司推出的,功耗小,电压可选用4~6V电压供电;DS1302时钟芯片是美国DALLAS公司推出的具有涓细电流充电功能的低功耗实时时钟芯片,它可以对年、月、日、星期、时、分、秒进行计时,还具有闰年补偿等多种功能,而且DS1302的使用寿命长,误差小;数字显示是采用的LED液晶显示屏来显示,可以同时显示年、月、日、星期、时、分、秒和温度等信息。

此外,该电子万年历还具有时间校准等功能。

关键词时钟电路;时钟芯片DS1302;LCD1602液晶显示器;单片机AT89C55WD.The Design of Calendar Based on SCMABSTRACTWith the society, science and technology, mankind learned that time, from the view of the sun, to the present electronic clock pendulum clock, continuous research and innovation. Observation time in the same time, be able to understand other human beings is closely related to information, such as temperature, week, date and so on, the birth of the electronic calendar, and it set the time, date, week and temperature-in-one, with easy to read, intuitive display functional diversity, and many other advantages of simple circuit with the electronic instrumentation of the development trend of the. market prospects are broad.The main use of the electronic calendar AT89C55WD single-chip microcomputer as the main core, provided by the DS1302 clock chip clock, DS18B20 the temperature chip acquisition transition temperature, LCD1602 display shows the dynamic scan. AT89C55WD single-chip microcomputer is introduced by Atmel Corporation, a small power consumption, voltage can be selected 4 ~ 6V power supply voltage; DS1302 clock chip is introduced DALLAS fine with trickle charge function of current low-power real-time clock chip, which can of the year, month, day, week, hour, minute, second for time, also has multiple functions, such as a leap year compensation, and long life of the DS1302, a small error; DS18B20 temperature chip is a digital temperature sensor with a measurement accuracy high, a simple circuit to connect the characteristics of such sensors only need a data cable for data transmission; digital LED display is used to display LCD screen, can display year, month, day, week, hour, minute, second and temperature, etc. information. In addition, the electronic calendar is also a time-calibrationfunctions.KEY WORDS: clock circuit; clock chip DS1302;LCD1602 screen; single-chipAT89C55WD;目录摘要 (I)ABSTRACT (II)前言 (1)第1章设计要求与方案论证 (2)§1.1功能要求 (2)§1.2 系统基本方案选择和论证 (2)§1.2.1 显示模块选择方案和论证 (2)§1.2.2 单片机的选择 (2)§1.2.3 键盘模块的选择 (3)§1.2.4 时钟芯片的选择方案和论证 (3)§1.3 电路设计最终方案决定 (4)第2章系统硬件电路的设计 (5)§2.1 闪电存储型器件AT89C55WD (5)§2.1.1 AT89C55WD具有下列主要性能 (5)§2.1.2 AT89C55WD的引脚及功能 (5)§2.1.3单片机主控制模块原理图 (7)§2.2 DS1302时钟电 (8)§2.2.1 DS1302芯片介绍 (8)§2.2.2 DS1302的性能特性 (9)§2.2.3 DS1302数据操作原理 (9)§2.2.4 DS1302的应用 (12)§2.3 DS18B20 数字温度传感器 (13)§2.3.1 DS18B20的主要特性 (13)§2.3.2 DS18B20的外形和内部结构 (13)§2.3.3 DS18B20工作原理 (14)§2.3.4 DS18B20的应用电路 (15)§2.4 LCD1602液晶显示器 (16)§2.4.1 1602LCD的基本参数 (16)§2.4.2引脚功能说明 (17)§2.4.3 LCD1602的应用电路 (18)§2.5 键盘电路 (18)§2.6 闹铃电路 (18)第3章系统的软件设计 (20)§3.1系统的主序流程图 (20)§3.2 时间调整程序流程图 (21)§3.3 温度子程序流程图 (22)第4章调试结果 (23)结论 (25)参考文献 (26)致谢 (27)附录一电路原理图 (28)附录二源程序代码 (29)附录三元器件清单 (32)前言随着电子技术的发展,人类不断研究,不断创新纪录。

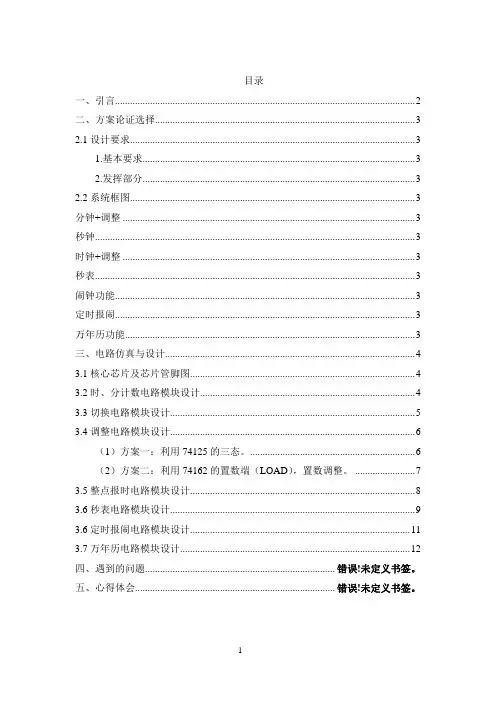

数字电子钟设计报告(显示、调整、报时、万年历、闹钟、秒表)目录一、引言............................................................................ ............................................ 2 二、方案论证选择............................................................................ ............................ 3 2.1设计要求............................................................................ .. (3)1.基本要求............................................................................ ................................. 32.发挥部分............................................................................ ................................. 3 2.2系统框图............................................................................ ...................................... 3 分钟+调整 ........................................................................... .......................................... 3 秒钟............................................................................ .................................................... 3 时钟+调整 ........................................................................... .......................................... 3 秒表............................................................................ .................................................... 3 闹钟功能............................................................................ ............................................ 3 定时报闹............................................................................ ............................................ 3 万年历功能............................................................................ ........................................ 3 三、电路仿真与设计............................................................................ ........................ 4 3.1核心芯片及芯片管脚图............................................................................ .............. 4 3.2时、分计数电路模块设计...................................................................................... 4 3.3切换电路模块设计............................................................................ ...................... 5 3.4调整电路模块设计............................................................................ . (6)(1)方案一:利用74125的三态。

带温度显示可调闹钟万年历摘要本设计由数据显示模块、温度采集模块、时间处理模块和调整设置模块四个模块组成。

系统最大的特点是体现了较强的人机交互和独立的模块化程序设计。

温度采集选用DS18B20芯片,数据显示采用1602A液晶显示模块,在第一行显示年月日、星期以及当前的状态,第二行显示温度和时间,合理的利用液晶显示区域。

51主芯片利用定时中断产生时间,控制着液晶的显示更新、温度的实时变化以及按键的读取处理,而对于闹钟,实际上就是时间里的一个嵌套程序。

时间和闹钟的值由按键调整设置,采用通用的二十四小时制。

该电路采用51单片机作为核心,功耗小,能在3V的低压工作,电压可选用3~5V电压供电。

综上所述此万年历具有读取方便、显示直观、功能多样、电路简洁、成本低廉等诸多优点,符合电子仪器仪表的发展趋势,具有广阔的市场前景。

关键字:万年历;温度计;闹钟;液晶显示一、方案设计与论证根据要求,系统分为四个模块进行方案设计:1.数据显示模块方案一:数据采集处理后采用六位数码管动态扫描,循环依次显示年月日(如09.01.01)、当前时间(如12.00.00)和温度星期(如+23.5_1),数码管用74LS164芯片驱动,硬件电路复杂且显示略显混乱,在软件方面,扫描部分由于要显示的数据太多而显的不清晰。

方案二:考虑到要显示的内容颇多,故运用1602A显示实时数据,第一行显示状态以及年月日星期(如S 2009—01—01 THU),第二行显示温度和实时时间(22.0C12:00:00),在处理按键设置时,第二行暂时屏蔽温度的显示而显示设置的内容。

这样虽然在程序方面多了1602A的一些初始化和读写子函数的定义,但程序的模块化却更加的清楚。

而且采用1602A LCM的液晶显示模块后不仅满足了大量数据的显示,,系统的硬件电路变的十分简单清晰明朗。

本设计采用了这种方案。

2 温度采集模块采用常用的温度采集芯片DS18B20单线数字温度传感器进行温度的采集。

万年历日历表传统的日历是将日干、日支记入日历,与干支的周期必须相同,才能显示日期。

但是日历无法与历法匹配,使用起来也不方便。

万年历日历 APP基于多年对传统日历的研究,对传统日历进行了重新编排,不仅加入了干支、日支记等功能,还增加了干支和年干、日支等功能。

万年历日历 APP界面简洁小巧,功能强大。

用户只需使用手机就可以轻松记录每天所发生的事情,每天一页,可以把每天发生的事情按日期顺序排列在日历中以便查询!1、智能计算农历天数智能计算农历天数,是我一直以来的梦想。

万年历日历自动生成农历天数,每天都会以日历日期的形式出现在智能日历中,非常人性化。

它有自动计算节气时间功能,无需手动计算。

这是一个方便快捷的日历功能!它有日期查询功能,主要用于查询农历日期。

它支持“年干”和“年支”分类查询农历天数,用户在选择“年干”后,系统会自动计算该日期天数为5天,自动生成农历天数为30天,之后自动将天数加入到日历列表中来。

如果日历自动计算日期和干、支都没有问题的话,用户还可以选择添加年干表或者日支表来方便查看。

2、日历功能齐全万年历日历为用户提供了各种日历查询功能,帮助用户轻松掌握生活的方方面面。

比如每天的生活轨迹,以及健康状况预测。

在日历界面的下方有三个常用选项,分别是每日总结、农历以及干支。

当用户输入关键字后,就可以从日总结中找到相关信息。

比如:今日的节气信息就可以了解到它是什么月份的节令,还可以根据日期的顺序性调整生活节奏等等!用户还可以根据自己的需要添加特定的内容来获取信息,比如天气情况等等!除此之外,万年历日历还提供了日历主题和日历菜单,为用户提供个性化选择!3、预览功能现在大多数手机都自带了智能导航功能,可以帮助用户更好地规划路线,方便快速地到达目的地。

万年历日历 APP可以让用户直接使用导航功能,在自己手机上预览自己在这一天所记录的事情。

同时,如果有特殊需求的用户可以手动输入日期,就可以省去在日期选择时浪费的时间了。

目录一、引言 (2)二、方案论证选择 (3)2.1设计要求 (3)1.基本要求 (3)2.发挥部分 (3)2.2系统框图 (3)分钟+调整 (3)秒钟 (3)时钟+调整 (3)秒表 (3)闹钟功能 (3)定时报闹 (3)万年历功能 (3)三、电路仿真与设计 (4)3.1核心芯片及芯片管脚图 (4)3.2时、分计数电路模块设计 (4)3.3切换电路模块设计 (5)3.4调整电路模块设计 (6)(1)方案一:利用74125的三态。

(6)(2)方案二:利用74162的置数端(LOAD),置数调整。

(7)3.5整点报时电路模块设计 (8)3.6秒表电路模块设计 (9)3.6定时报闹电路模块设计 (11)3.7万年历电路模块设计 (12)四、遇到的问题.......................................................................... 错误!未定义书签。

五、心得体会.............................................................................. 错误!未定义书签。

一、引言电子钟亦称数显钟(数字显示钟),是一种用数字电路技术实现时、分、秒计时的装置,与机械时钟相比,直观性为其主要显著特点,且因非机械驱动,具有更长的使用寿命,相较石英钟的石英机芯驱动,更具准确性。

电子钟已成为人们日常生活中必不可少的必需品,广泛用于个人家庭以及车站、码头、剧院、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大地方便。

相对于其他时钟类型,它的特点可归结为“两强一弱”:比机械钟强在观时显著,比石英钟强在走时准确,但是它的弱点为显时较为单调。

数字钟的核心即数字电子技术课程中有关时序逻辑电路、组合逻辑电路的内容。

这些也是我们学电子的学生应该掌握的最基本知识。

通过这次试验,不仅可以加深我对数字电子技术课程的理解,也可以提高自己的动手能力以及实际问题中解决问题的能力,培养对数字电子技术的兴趣。

一、功能描述1、上板复位后从元年1月1号开始计数,为方便上板调试,将一天的时间压缩为1秒;2、按键用于设置日历,按下按键0进入设置状态,再次按下按键0退出设置状态;3、按键1来选择想要设置的年月日的各个位;4、按键2在设置状态进行计数设置,每按下一次数码管显示数字加1;5、平年365天(52周+1天),闰年366天(52周+2天)。

平年2月28天,闰年2月29天。

6、闰年:每400年整一闰,或每4年且不为百年的一闰。

即能被400整除,或不能被100整除但能被4整除的年份为闰年。

二、平台效果图3.仿真结果:选取3个日期检查(1)1900年2月28日:该年不是闰年,故2月份只有28天(2)2000年2月29日:该年是闰年,故2月份有29天(3)2016年12月27日:经验证,日期显示正确。

三、实现过程首先根据所需要的功能,列出工程顶层的输入输出信号列表。

我们可以把工程划分成三个模块,分别是万年历计数模块、按键模块和数码管显示模块。

1.万年历计数模块万年历计数模块实现的是万年历计数功能,为方便观看,将一天时间设置为一秒,日计数器dat_cnt、月份计数器mon_cnt_h、mon_cnt_1、mon_2_h、mon_2_1分别为大月小月以及平年闰年的2月计数器、年份计数器yea_one、yea_ten、yea_hun、yea_tho分别为年份的个十百千位,由yea_cnt_tol <= yea_cnt1000 + yea_cnt100 + yea_cnt10 + yea_one得到年份。

本模块还自动计算当年是否是平闰年。

本模块信号列表如下:2.按键模块本次案例万年历使用的是4x4矩阵键盘,本模块就是实现了矩阵键盘的扫描并使用以及按键消抖功能。

通过行扫描法得到按下的键的位置信息。

本模块的信号列表如下:3.数码管模块数码管模块实现了将年月日的信息显示在数码管上。

本模块的信号列表如下:。

摘要电子万年历是一种非常广泛日常计时工具,对现代社会越来越流行。

它可以对年、月、日、周日、时、分、秒进行计时,还具有闰年补偿等多种功能。

本系统选用DALLAS公司生产的日历时钟芯片DS12C887来作为实时时钟芯片,为本系统提供详细的年、月、日、星期和小时、分钟等时间信息。

数字万年历采用直观数字显示,可以同时显示年、月、日、周日、时、分、秒和温度等信息,还具有定时和时间校准等功能。

该电路采用AT89S52单片机作为核心,功耗小,能在3V的低压工作,电压可选用3~5V电压供电。

本系统硬件部分由AT89S52单片机、DS12C887时钟芯片、1062液晶显示器、DS18B20温度测量、键盘、蜂鸣器系统等部分构成。

软件部分在keil 环境下用C51语言编写,包括时间设置、时间显示、定时设置、定时闹钟、温度显示。

没有良好的基础知识和实践经验会受到很大限制,每项功能实现时需要那种硬件,程序该如何编写,算法如何实现等,没有一定的基础就不可能很好的实现。

在编写程序过程中发现以现有的相关知识要独自完成编写任务困难重重,在老师和同学的帮助下才完成了程序部分的编写。

文章后附有电路原理图、程序清单,以供读者参考。

因水平有限,难免有疏落不足之处,敬请老师和同学能给与批评指正。

关键词:时钟芯片DS12C887;温度采集DS18B20;单片机AT89S52;液晶显示1602目录第一章概述 (3)§1.1实时时钟研究的背景及意义 (3)§1.2论文主要研究内容 (3)1.2.1 系统设计实现的目标 (3)1.2.2 系统的总体设计 (3)第二章硬件电路设计 (5)§2.1单片机最小系统 (5)§2.2时钟芯片电路 (5)2.2.1 时钟芯片引脚介绍 (5)2.2.2时钟芯片DS12C887,其内存空间介绍 (7)2.2.3 4个控制寄存器介绍 (7)§2.4温度采集电路设计 (9)2.4.1 DS18B20的主要特性 (9)2.4.2 DS1820的基本操作指令 (9)2.4.3 温度测量的步骤 (10)2.4.4 DS18B20的操作时序 (10)§2.5 1602LCD液晶显示屏 (12)2.5.1 1602字符型LCD简介 (12)2.5.2 1602引脚功能说明 (12)2.5.3 1602LCD的指令说明及时序 (12)2.5.4 1602LCD的RAM地址映射及标准字库表 (14)2.5.5 1602LCD的一般初始化(复位)过程 (16)2.4.6 1602LCD的电路连接 (16)§2.6 蜂鸣器闹铃电路 (17)§2.7 按键调整电路 (17)§2.8 电源模块 (18)第三章软件部分设计 (19)§3.1 主程序流程 (19)§3.2 时间设置子程序流程 (19)§3.3 闹钟设置子程序流程 (20)§3.4 程序设计问题 (21)3.4.1 按键抖动问题 (21)3.4.2 蜂鸣器设置 (21)3.4.3 液晶显示的设置 (21)3.4.4 中断设置 (21)3.4.5 时钟芯片设置 (22)结束语 (25)致谢词 (26)参考文献 (27)附件1 (28)第一章概述§1.1实时时钟研究的背景及意义在现实我们生活中每个人都可能有自己的时钟,光阴在永不停息的流逝,有了时钟人们就能随着时间有计划的过着每一天。

本次课程设计要求显示万年历时钟表。

要求实现正常的时、分、秒计数。

二十四小时的时间计时。

本次课程设计采用黑金AX301开发平台。

相关硬件原理图和PCB图见文件夹。

一.各个设计模块描述(一)计时模块1.秒计数是由一个六十进制的计数器构成,生成元器件如下Clk:驱动秒计时器的时钟信号Clr:校准时间时清零的输入端En:使能端Sec0[3..0] sec1[3..0]:秒的高位显示,低位显示Co:进位输出端,作为分的clk输入代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity second isport (clk,clr,en:in std_logic;sec0,sec1:out std_logic_vector(3 downto 0);co:out std_logic);end second;architecture sec of second isSIGNAL cnt1,cnt0:std_logic_vector(3 downto 0);beginprocess(clk)beginif(clr='0')thencnt0<="0000";cnt1<="0000";elsif(clk'event and clk='1')thenif cnt1="0101" and cnt0="1000" thenco<='1';cnt0<="1001";elsif cnt0<"1001" thencnt0<=(cnt0+1);elsecnt0<="0000";if cnt1<"0101"thencnt1<=cnt1+1;elsecnt1<="0000";co<='0';end if;end if;end if;end if;sec1<=cnt1;sec0<=cnt0;end process;end sec;仿真图如下:2.分计数是由六十进制的计数器构成,生成元器件如下Clk:设置分输入和秒进位的或输入En:使能输入Min1[3..0] min0[3..0]:分的高位显示,低位显示Co:向时的进位输出代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity minute isport (clk,en:in std_logic;min1,min0:out std_logic_vector(3 downto 0);co:out std_logic);end minute;architecture min of minute isSIGNAL cnt1,cnt0:std_logic_vector(3 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thenif en='1' thenif cnt1="0101" and cnt0="1001" thenco<='1';cnt0<="0000";cnt1<="0000";elsif cnt0<"1001" thencnt0<=(cnt0+1);elsecnt0<="0000";cnt1<=cnt1+1;co<='0';end if;end if;end if;min1<=cnt1;min0<=cnt0;end process;end min;仿真图如下:3.时计数是由二十四进制的计数器构成,生成元器件如下Clk:设置时间输入和分进位输入的或en:使能端h1[3..0] h0[3..0]:时的高位显示和低位显示代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity hour isport(clk,en:in std_logic;h1,h0:out std_logic_vector(3 downto 0));end hour;architecture beha of hour issignal cnt1,cnt0:std_logic_vector(3 downto 0);beginprocess(clk)beginif(clk'event and clk='1') thenif en='1' thenif cnt1="0010" and cnt0="0011" thencnt1<="0000";cnt0<="0000";elsif cnt0<"1001" thencnt0<=cnt0+1;elsecnt0<="0000";cnt1<=cnt1+1;end if;end if;h1<=cnt1;h0<=cnt0;end process;end beha;仿真图如下:(二)设置时间模块1.按键去抖动,生成元器件如下Clk:256hz频率输入Reset:接GNDDin:接按键Dout:输出传给按键选择器代码如下library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity debounce isport(clk,reset:in std_logic; --200HZdin:in std_logic;dout:out std_logic);end debounce;architecture a of debounce istype state is(s0,s1,s2);signal current:state;process(clk,reset,din)beginif(reset='1')thencurrent<=s0;dout<='1';elsif (clk'event and clk='1')then case current iswhen s0=>dout<='1';if(din='0')thencurrent<=s1;elsecurrent<=s0;end if;when s1=>dout<='1';if(din='0')thencurrent<=s2;elsecurrent<=s0;end if;when s2=>dout<='0';if(din='0')thencurrent<=s2;elsecurrent<=s0;end if;when others=>dout<='1'; current<=s0;end case;end if;end process;end a;仿真图如下:2.按键选择器,生成元器件如下:Clk:16hz输入Key1:按键调分的输入Key2:按键调时的输入Key3:按键秒清零的输入Led1:输出信号给分元器件Led2:输出信号给时元器件Led3:输出清零信号给秒元器件代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity ctr1 isport(clk:in std_logic; --10HZkey1,key2,key3,key4:in std_logic;led1,led2,led3,led4:out std_logic);end ctr1;architecture a of ctr1 isbeginprocess (clk)beginif(clk'event and clk='1')thenif(key1='0')thenled1<='1';led2<='0';led3<='0';led4<='0';elsif(key2='0')thenled1<='0';led2<='1';led3<='0';led4<='0';elsif(key3='0')thenled1<='0';led2<='0';led3<='1';led4<='0';elsif(key4='0')thenelseled1<='0';led2<='0';led3<='0';led4<='0'; end if;end if;end process;end a;仿真图如下:(三)整点报时模块生成元器件如下:Clk1:接512hzClk2 clk:En:使能输入M1[3..0] m0[3..0]:接分的高位输出和低位输出S1[3..0] s0[3..0]:接秒的高位输出和低位输出Speaker:连接蜂鸣器代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity xiang isport(m1,m0,s1,s0:in std_logic_vector(3 downto 0);en,clk1,clk2,clk:in std_logic;speaker:out std_logic);end xiang;architecture sss_arc of xiang isbeginprocess(clk,clk1,clk2,m1,m0,s1,s0)beginif(en='1')thenspeaker<=clk;elsif(m1="0101"and m0="1001")thenif(s1="0101")thenif(s0="1001")thenelsif(s0="0001" or s0="0011" or s0="0101" or s0="0111")thenspeaker<=clk1;--512HZend if;elsespeaker<='0';end if;elsif(m0<"1001" or m1<"0101"or s1<"0101")thenspeaker<='0';end if;end process;end sss_arc;仿真图如下:(四)显示时间模块1.模八的器件控制八个数码管显示的循环,生成元器件如下Clk:输入Clr:接GNDEn:使能端Y[2..0]:输出接数码管三个接受端代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mo8 isport(clr,clk,en:in std_logic;y:out std_logic_vector(2 downto 0));end mo8;architecture beha of mo8 issignal p:std_logic_vector(2 downto 0);beginprocess(clk)beginif clk'event and clk='1' thenif en='1' thenif p="111" thenp<="000";elsif p<"111" thenp<=p+1;end if;end if;end if;y<=p;end process;end beha;仿真图如下:2.八选一的器件控制数码管的亮或不亮,生成元器件如下Sel【2..0】:连接模八器件M7[3..0] m6[3..0]:连接秒的高位和低位输出M5[3..0]:接vcc(显示横)M4[3..0] m3[3..0]:接分的高位和低位输出M2[3..0]:接vcc(显示横)M1[3..0] m0[3..0]:连接时的高位低位输出Y[3..0]:输出给数码管显示代码如下:library ieee;use ieee.std_logic_1164.all;entity mux8_1 isport(m0,m1,m2,m3,m4,m5,m6,m7:in std_logic_vector(3 downto 0); sel:in std_logic_vector(2 downto 0);y:out std_logic_vector(3 downto 0));end mux8_1;architecture arc of mux8_1 isbeginprocess(sel)begincase sel iswhen"000"=>y<=m0;when"001"=>y<=m1;when"010"=>y<=m2;when"011"=>y<=m3;when"100"=>y<=m4;when"101"=>y<=m5;when"110"=>y<=m6;when"111"=>y<=m7;when others=>y<="XXXX";end case;end process;end arc;仿真图如下:3.数码管显示器件,生成元器件如下Num[3..0]:接收八选一的输出信号Y[6..0]:驱动数码管显示代码如下:library ieee;use ieee.std_logic_1164.all;entity xianshi isport(num:in std_logic_vector(3 downto 0);y:out std_logic_vector(6 downto 0));end xianshi;architecture beha of xianshi isbeginprocess(num)begincase num iswhen"0000"=>y<="0111111";when"0001"=>y<="0000110";when"0010"=>y<="1011011";when"0011"=>y<="1001111";when"0100"=>y<="1100110";when"0101"=>y<="1101101";when"0110"=>y<="1111101";when"0111"=>y<="0000111";when"1000"=>y<="1111111"; when"1001"=>y<="1101111";when others=>y<="1000000";end case;end process;end beha;仿真图如下:(五)分频模块分频器生成的元器件如下:Clk:时钟输入Clk512:512hz给响铃模块Clk1:1hz输出给秒计数器Clk16:16hz输出给按键选择器Clk256:256hz输出给按键抖动代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin isport(clk:in std_logic;-- q:out std_logic_vector(9 downto 0);clk512,clk4,clk1,clk16,clk256:out std_logic); end fenpin;architecture behave of fenpin issignal y:std_logic_vector(9 downto 0);beginprocess(clk)beginif(clk='1')thenif(y="1111111111")theny<="0000000000";clk512<=y(0);clk256<=y(1);clk16<=y(5);clk4<=y(7);clk1<=y(9);elsey<=y+'1';clk512<=y(0);clk256<=y(1);clk16<=y(5);clk4<=y(7);clk1<=y(9);end if;end if;end process;end behave;仿真图如下:闹钟模块1.比较器,比较当时显示时间与设置的闹钟时间是否相等,如相等,输出信号给蜂鸣器。