数字逻辑状态机例子

- 格式:doc

- 大小:661.50 KB

- 文档页数:9

fpga2段状态机设计FPGA(现场可编程门阵列)是一种灵活的数字电路设计工具,它可以用来实现各种数字逻辑电路,包括状态机。

状态机是一种抽象的数学模型,用于描述系统在不同状态之间的转移和行为。

在FPGA中设计状态机需要考虑多个方面,包括状态的定义、状态转移条件、输出逻辑等。

首先,我们需要定义状态机的状态。

状态机可以是Mealy型或者Moore型。

Mealy型状态机的输出取决于当前状态和输入,而Moore型状态机的输出仅仅取决于当前状态。

在设计状态机时,我们需要明确定义每个状态以及状态之间的转移条件。

这可以通过状态转移图或者状态转移表来表示。

其次,我们需要考虑状态机的输入和输出。

输入可以是外部信号,输出可以是状态机的输出信号或者控制其他逻辑电路的信号。

在FPGA中,我们可以使用寄存器来存储状态机的当前状态,使用组合逻辑来实现状态转移条件和输出逻辑。

另外,时序是状态机设计中一个非常重要的考虑因素。

我们需要确保状态机的状态转移和输出逻辑在时钟的控制下按照预期进行。

在FPGA中,我们可以使用时钟信号来同步状态机的操作,确保状态机的稳定和可靠性。

最后,我们需要进行综合和布局布线,将状态机的逻辑电路映射到FPGA的可编程逻辑单元(PLC)和寄存器中。

在这个过程中,我们需要考虑逻辑优化、时序约束等问题,以确保状态机能够在FPGA中正确运行。

综上所述,设计FPGA中的状态机需要考虑状态定义、状态转移条件、输出逻辑、时序等多个方面。

在实际设计中,我们需要结合具体的应用场景和FPGA的特性来进行设计,以实现所需的功能并满足性能要求。

fpga 有限状态机例子有限状态机(Finite State Machine,FSM)是一种常见的设计模式,用于描述和实现具有有限数量状态的对象的行为。

在硬件设计中,有限状态机常常用于描述数字逻辑电路的行为。

以下是一个使用Verilog语言编写的简单有限状态机的例子:verilog复制代码module counter(input clk, reset, output reg [3:0] count);// 定义状态机的状态parameter IDLE = 4'b0000; // 初始状态parameter COUNTER = 4'b0001; // 计数状态// 状态机的当前状态reg [3:0] current_state;// 状态转移逻辑always @(posedge clk or posedge reset) begin if (reset) begincurrent_state <= IDLE; // 如果reset信号为高,则进入IDLE状态end else begincase (current_state)IDLE: beginif (count == 4'b1000) current_state <= COUNTE R; // 如果计数达到8,则进入COUNTER状态endCOUNTER: begincurrent_state <= IDLE; // 在COUNTER状态下,计数完成后回到IDLE状态enddefault: begincurrent_state <= IDLE; // 如果状态机处于未知状态,则强制回到IDLE状态endendcaseendend// 计数逻辑always @(posedge clk) beginif (current_state == COUNTER) count <= count + 1; // 在COUNTER状态下,计数器递增endendmodule在这个例子中,我们定义了一个简单的4位计数器。

有限状态机的verilog例子有限状态机(Finite State Machine, FSM)是数字电路设计中的一种基本构件,它可以用来实现各种复杂的控制逻辑。

在Verilog中,可以用模块(module)来描述一个有限状态机,使用参数(parameters)来定义状态数量和状态转移逻辑。

以下是一个简单的有限状态机的Verilog例子,该FSM有3个状态(S0, S1, S2)和两个输入(clk, rst_n)以及一个输出(next_state, out):```verilogmodule fsm(input wire clk, // 时钟信号input wire rst_n, // 低电平复位信号input wire [1:0] in, // 输入信号,这里位宽为2,可以扩展output reg next_state, // 下一状态输出output reg out // 输出信号);// 状态参数parameter S0 = 2'b00;parameter S1 = 2'b01;parameter S2 = 2'b10;// 状态寄存器reg [1:0] state;// 状态转移逻辑always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 当处于复位状态时,状态寄存器和输出都初始化为0state <= S0;out <= 1'b0;end else begin// 根据当前状态和输入信号,更新下一状态和输出case (state)S0: beginnext_state <= S1;out <= 1'b1;endS1: beginnext_state <= S2;out <= 1'b0;endS2: beginnext_state <= S0;out <= 1'b1;enddefault: beginnext_state <= S0;out <= 1'b0;endendcaseendendendmodule```在这个例子中:- `clk` 是时钟信号。

数字逻辑实验报告数字逻辑实验报告引言数字逻辑是计算机科学中的重要基础知识,通过对数字信号的处理和转换,实现了计算机的高效运算和各种复杂功能。

本实验旨在通过实际操作,加深对数字逻辑电路的理解和应用。

实验一:二进制加法器设计与实现在这个实验中,我们需要设计一个二进制加法器,实现两个二进制数的加法运算。

通过对二进制数的逐位相加,我们可以得到正确的结果。

首先,我们需要将两个二进制数输入到加法器中,然后通过逻辑门的组合,实现逐位相加的操作。

最后,将得到的结果输出。

实验二:数字比较器的应用在这个实验中,我们将学习数字比较器的应用。

数字比较器可以比较两个数字的大小,并输出比较结果。

通过使用数字比较器,我们可以实现各种判断和选择的功能。

比如,在一个电子秤中,通过将待测物品的重量与设定的标准重量进行比较,可以判断物品是否符合要求。

实验三:多路选择器的设计与实现在这个实验中,我们需要设计一个多路选择器,实现多个输入信号中的一路信号的选择输出。

通过使用多路选择器,我们可以实现多种条件下的信号选择,从而实现复杂的逻辑控制。

比如,在一个多功能遥控器中,通过选择不同的按钮,可以控制不同的家电设备。

实验四:时序电路的设计与实现在这个实验中,我们将学习时序电路的设计与实现。

时序电路是数字逻辑电路中的一种重要类型,通过控制时钟信号的输入和输出,实现对数据的存储和处理。

比如,在计数器中,通过时序电路的设计,可以实现对数字的逐位计数和显示。

实验五:状态机的设计与实现在这个实验中,我们将学习状态机的设计与实现。

状态机是一种特殊的时序电路,通过对输入信号和当前状态的判断,实现对输出信号和下一个状态的控制。

状态机广泛应用于各种自动控制系统中,比如电梯控制系统、交通信号灯控制系统等。

实验六:逻辑门电路的优化与设计在这个实验中,我们将学习逻辑门电路的优化与设计。

通过对逻辑门电路的布局和连接方式进行优化,可以减少电路的复杂性和功耗,提高电路的性能和可靠性。

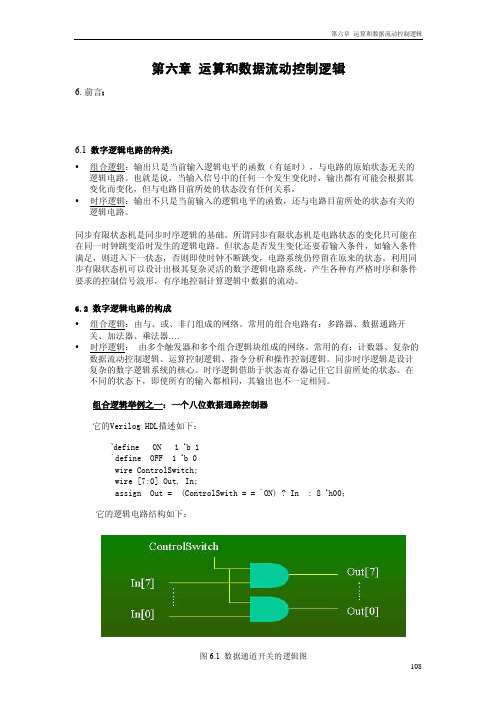

第六章运算和数据流动控制逻辑6.前言:6.1数字逻辑电路的种类:•组合逻辑:输出只是当前输入逻辑电平的函数(有延时),与电路的原始状态无关的逻辑电路。

也就是说,当输入信号中的任何一个发生变化时,输出都有可能会根据其变化而变化,但与电路目前所处的状态没有任何关系。

•时序逻辑:输出不只是当前输入的逻辑电平的函数,还与电路目前所处的状态有关的逻辑电路。

同步有限状态机是同步时序逻辑的基础。

所谓同步有限状态机是电路状态的变化只可能在在同一时钟跳变沿时发生的逻辑电路。

但状态是否发生变化还要看输入条件,如输入条件满足,则进入下一状态,否则即使时钟不断跳变,电路系统仍停留在原来的状态。

利用同步有限状态机可以设计出极其复杂灵活的数字逻辑电路系统,产生各种有严格时序和条件要求的控制信号波形,有序地控制计算逻辑中数据的流动。

6.2 数字逻辑电路的构成•组合逻辑:由与、或、非门组成的网络。

常用的组合电路有:多路器、数据通路开关、加法器、乘法器….•时序逻辑:由多个触发器和多个组合逻辑块组成的网络。

常用的有:计数器、复杂的数据流动控制逻辑、运算控制逻辑、指令分析和操作控制逻辑。

同步时序逻辑是设计复杂的数字逻辑系统的核心。

时序逻辑借助于状态寄存器记住它目前所处的状态。

在不同的状态下,即使所有的输入都相同,其输出也不一定相同。

组合逻辑举例之一:一个八位数据通路控制器它的Verilog HDL描述如下:`define ON 1 ‘b 1`define OFF 1 ‘b 0wire ControlSwitch;wire [7:0] Out, In;assign Out = (ControlSwith = = `ON) ? In : 8 ‘h00;它的逻辑电路结构如下:图6.1 数据通道开关的逻辑图108109它对数据通路所起的作用如下:组合逻辑举例之二:一个八位三态数据通路控制器它的Verilog HDL 描述如下:`define ON 1 ‘b 1`define OFF 1 ‘b 0wire LinkBusSwitch;wire [7:0] outbuf;inout [7:0] bus;assign bus = (LinkBusSwitch== `ON) ? outbuf : 8 ‘hzz它的逻辑电路结构和对数据通路的作用如下:它与组合逻辑举例之一的差别只在前者在开关断开时输出为零,而后者在开关断开时输出为高阻,即与总线脱离连接。

案例5状态机:MOORE机、MEALY机(以序列检测器为主要内容)5.1 预习内容(1)状态机的基本概念,分类,原理,设计方法,时序情况。

(2)状态机的具体设计流程:逻辑抽象--状态定义--状态转换分析,画出状态图--根据状态图写出代码。

5.2 案例目的熟悉利用QuartusⅡ的代码输入方法设计状态机,并掌握编程配置以及硬件测试验证等一系列相关技术,并理解FPGA/CPLD技术中是如何解决生活中实际逻辑问题的。

5.3 案例环境状态机是数字系统设计中重要的内容之一。

无论是简单的译码电路还是复杂的CPU都可以用状态机来实现。

5.4 案例原理序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号这在数字通信领域有广泛的应用当序列检测器连续收到一组串行二进制码后如果这组码与检测器中预先设置的码相同则输出1否则输出0由于这种检测的关键在于正确码的收到必须是连续的这就要求检测器必须记住前一次的正确码及正确序列直到在连续的检测中所收到的每一位码都与预置数的对应码相同在检测过程中任何一位不相等都将回到初始状态重新开始检测如图1所示当一串待检测的串行数据进入检测器后若此数在每一位的连续检测中都与预置的密码数相同则输出A 否则仍然输出B。

图1 8位序列检测器逻辑图comb_outputsstate_inputs resetclkFSM:s_machineCOM next_state current_state PROCESS REG PROCESS图2 一般状态机结构图5.5 案例步骤(1) 按照状态机的设计流程,完成逻辑抽象到状态图表示等一系列流程,根据状态图设计出硬件描述语言代码,完成代码的输入,编译、综合,通过对报错信息的分析调试代码直到代码完全正确。

完成电路的仿真,观察仿真波形是否符合电路的逻辑功能要求。

(2) 完成电路的引脚锁定,分别将各输入引脚锁定到按键或者跳线上,时钟输入端锁定在开发试验系统的时钟输出引脚上,将计数器的输出通过译码电路连接到7段数码管上进行显示。

verilog 组合逻辑例子Verilog组合逻辑例子Verilog是一种硬件描述语言,常用于数字逻辑综合和编写硬件模块。

组合逻辑是Verilog中的一种基本类型,用于描述没有存储功能,只有输入和输出之间逻辑关系的电路。

以下是一些Verilog组合逻辑例子及其详细讲解。

1. 逻辑门AND门module and_gate(input a,input b,output y);assign y = a && b;endmodule在这个例子中,我们定义了一个AND门的模块。

它有两个输入a 和b,一个输出y。

通过assign语句,我们将输出y赋值为输入a和b 的逻辑与结果。

OR门module or_gate(input a,input b,output y);assign y = a || b;endmodule这是一个OR门的例子。

和AND门类似,我们通过assign语句将输出y赋值为输入a和b的逻辑或结果。

2. 多路选择器module mux(input a,input b,input c,input d,input [1:0] sel,output y);assign y = (sel == 2'b00) ? a :(sel == 2'b01) ? b :(sel == 2'b10) ? c :d;endmodule这个例子演示了一个4路多路选择器。

它有4个输入a、b、c和d,一个2位选择信号sel,一个输出y。

根据选择信号的不同值,输出y将根据如下规则选择不同的输入信号:00选择a,01选择b,10选择c,11选择d。

3. 比较器module comparator(input [3:0] a,input [3:0] b,output eq,output gt,output lt);assign eq = (a == b);assign gt = (a > b);assign lt = (a < b);endmodule上面的例子展示了一个比较器。

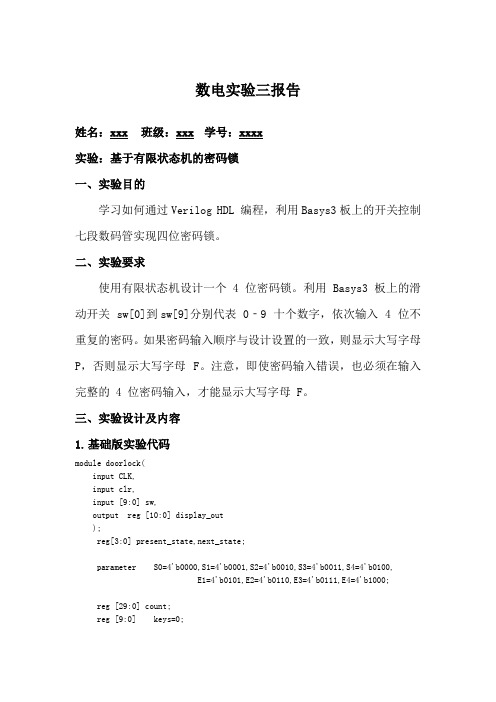

数电实验三报告姓名:xxx班级:xxx 学号:xxxx实验:基于有限状态机的密码锁一、实验目的学习如何通过Verilog HDL 编程,利用Basys3板上的开关控制七段数码管实现四位密码锁。

二、实验要求使用有限状态机设计一个 4 位密码锁。

利用 Basys3 板上的滑动开关 sw[0]到sw[9]分别代表 0‐9 十个数字,依次输入 4 位不重复的密码。

如果密码输入顺序与设计设置的一致,则显示大写字母P,否则显示大写字母F。

注意,即使密码输入错误,也必须在输入完整的 4 位密码输入,才能显示大写字母 F。

三、实验设计及内容1.基础版实验代码module doorlock(input CLK,input clr,input [9:0] sw,output reg [10:0] display_out);reg[3:0] present_state,next_state;parameter S0=4'b0000,S1=4'b0001,S2=4'b0010,S3=4'b0011,S4=4'b0100,E1=4'b0101,E2=4'b0110,E3=4'b0111,E4=4'b1000;reg [29:0] count;reg [9:0] keys=0;always @(posedge CLK or posedge clr)beginif (clr) count<=0;else count<=count+1;endassign clk_3=count[24];// ~3Hzalways @(posedge clk_3 or posedge clr) // STATE TRANSITIONbeginif (keys!=sw) keys <= sw;if (clr) present_state <= S0;else present_state <= next_state;end// Demo for Finite State Machine// the correct password is 0->1->2->3 (Switch sw[0]->sw[1]->sw[2]->sw[3] in order. always @(*)begincase (present_state)S0: beginif (~|keys[9:0]) next_state <=S0; // no key pressedelse if (keys[2]) next_state <=S1; // first valid key pressedelse next_state <=E1; // first invalid key pressedendS1: beginif (~|keys[9:3]&&~|keys[1:0]) next_state <=S1; // no key pressedelse if (keys[1]) next_state <=S2;// second valid key pressedelse next_state <=E2;// second invalid key pressedendS2: beginif (~|keys[9:3]&&~|keys[0]) next_state <=S2; // no key pressedelse if (keys[7]) next_state <=S3; // third valid key pressedelse next_state <=E3;// third invalid key pressedendS3: beginif (~|keys[9:8]&&~|keys[6:3]&&~|keys[0]) next_state <=S3; // no key pressedelse if (keys[3]) next_state <=S4;// fourth vaild key pressedelse next_state <=E4;// fourth invalid key pressedendS4: beginif (~|keys[9:8]&&~|keys[6:4]&&~|keys[0]) next_state <=S4; // no keypressedelse next_state <=E1; // fifth key pressed, but ignored *** endE1:beginif (keys!=sw) next_state <=E2; // second invalid key pressedelse next_state <=E1; // no key pressedendE2:beginif (keys!=sw) next_state <=E3; // third invalid key pressedelse next_state <=E2; // no key pressedendE3:beginif (keys!=sw) next_state <=E4; // fourth invalid key pressedelse next_state <=E3; // no key pressedendE4: next_state <=E4; // the additional keys are ALL ignored ***default: next_state <=S0;endcaseendalways @(*) // indicate the number of inputs and display the tag begincase(present_state)S4: display_out<=11'b0111_0011000;// P in left-most segmentE4: display_out<=11'b1110_0111000;// F in right-most segmentS0: display_out<=11'b1001_0011100;// oo in the middle segmentsS1,E1: display_out<=11'b1001_0111111;// confirm first inputS2,E2: display_out<=11'b1001_0011111;// confirm second inputS3,E3: display_out<=11'b1001_0011110;// confirm third inputdefault:display_out<=11'b1111_1111111; // no displayendcaseendendmodule2.进阶版实验代码module doorlock2(input CLK,input clr,input [9:0] sw,output reg [10:0] display_out);reg[3:0] present_state,next_state;reg [19:0]count1=0;reg [2:0] sel=0;parameter S0= 4'b0000,S1=4'b0001,S2=4'b0010,S3=4'b0011,S4=4'b0100, S01=4'b1001,S02=4'b1010,S03=4'b1011,E1=4'b0101,E2=4'b0110,E3=4'b0111,E4=4'b1000;parameter T1MS=50000,T2MS=20000_0000;reg [29:0] count;reg [32:0] count2=0;reg [9:0] keys=0;reg flag;always @(posedge CLK or posedge clr)beginif (clr)begincount<=0;endelse count<=count+1;endwire clk_3;assign clk_3=count[24];// ~3Hzalways @(posedge clk_3 or posedge clr) // STATE TRANSITIONbeginif (keys!=sw) keys <= sw;if (clr) present_state <= S0;else present_state <= next_state;endalways@(posedge CLK or posedge clr)beginif(present_state == S4)beginif(count2<T2MS)begincount2<=count2+1;flag<=1'b0;endelsebeginflag<=1'b1;endendif(clr) count2<=0;end// Demo for Finite State Machine// the correct password is 0->1->2->3 (Switch sw[0]->sw[1]->sw[2]->sw[3] in order. always @(*)begincase (present_state)S0: beginif (~|keys[9:0]) next_state <=S0; // no key pressedelse if (keys[2]) next_state <=S1; // first valid key pressedelse next_state <=E1; // first invalid key pressedendS1: beginif (~|keys[9:3]&&~|keys[1:0]) next_state <=S1; // no key pressed//else if (!sw) next_state <=S01;// second valid key pressedelse if(keys[1]&&keys[2]) next_state<=S2;else next_state <=E2;// second invalid key pressedendS01:beginif(!sw) next_state<=S01;else if(sw[2]) next_state<=S2;else next_state<=E2;endS2: beginif (~|keys[9:3]&&~|keys[0]) next_state <=S2; // no key pressed//else if (!sw) next_state <=S02; // third valid key pressedelse if (keys[2]&&keys[1]&&keys[3]) next_state <=S3;else next_state<=E3;// third invalid key pressedendS02: beginif(!sw) next_state<=S02;else if(sw[1]) next_state<=S3;else next_state<=E3;endS3: beginif (keys[1]&&keys[2]&&keys[3]) next_state <=S3; // no key pressed else if (!sw[3]) next_state <=S03;// fourth vaild key pressedelse next_state <=E4;// fourth invalid key pressedendS03:beginif(~|keys[9:3]&&~|keys[0]) next_state<=S03;else if(keys[3]) next_state<=S4;else next_state<=E4;endS4: beginif (~|keys[9:4]&&~|keys[0]) next_state <=S4; // no key pressedelse next_state <=E1; // fifth key pressed, but ignored *** endE1:beginif (keys!=sw) next_state <=E2; // second invalid key pressedelse next_state <=E1; // no key pressedendE2:beginif (keys!=sw) next_state <=E3; // third invalid key pressedelse next_state <=E2; // no key pressedendE3:beginif (keys!=sw) next_state <=E4; // fourth invalid key pressedelse next_state <=E3; // no key pressedendE4: next_state <=E4; // the additional keys are ALL ignored ***default: next_state <=S0;endcaseendalways@(posedge CLK)begincount1<=count1+1;if(count1==T1MS)begincount1<=0;sel<=sel+1;if(sel==4)sel<=0;endendalways @(posedge CLK) // indicate the number of inputs and display the tagbegincase(present_state)S0: begincase(sel)0:display_out<=11'b0111_0101000;1:display_out<=11'b1011_0110000;2:display_out<=11'b1101_1000100;3:display_out<=11'b1110_0110110;default:display_out<=11'b1111_1111111;endcaseendS1: begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1110111;2:display_out<=11'b1101_1110111;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseend // confirm first inputS2: begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_1110111;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseend // confirm second inputS3: begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_0000110;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseend // confirm third inputS4: beginif(!flag)begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_0000110;3:display_out<=11'b1110_0000110;default:display_out<=11'b1111_1111111;endcaseendelse display_out<= 11'b0111_0011000 ;end // P in left-most segmentS01:begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1110111;2:display_out<=11'b1101_1110111;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseendS02:begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_1110111;3:display_out<=11'b1110_1110111; default:display_out<=11'b1111_1111111;endcaseendS03: begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_0000110;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseendE1: display_out<=11'b0111_0111000;E2: display_out<=11'b1011_0111000;E3: display_out<=11'b1101_0111000;E4: display_out<=11'b1110_0111000;// F in right-most segment default:display_out<=11'b1111_1111111; // no displayendcaseendendmodule约束文件代码:## Clock signalset_property PACKAGE_PIN W5 [get_ports CLK]set_property IOSTANDARD LVCMOS33 [get_ports CLK]## Switchesset_property PACKAGE_PIN V17 [get_ports {sw[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]set_property PACKAGE_PIN V16 [get_ports {sw[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]set_property PACKAGE_PIN W16 [get_ports {sw[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]set_property PACKAGE_PIN W17 [get_ports {sw[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]set_property PACKAGE_PIN W15 [get_ports {sw[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]set_property PACKAGE_PIN V15 [get_ports {sw[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]set_property PACKAGE_PIN W14 [get_ports {sw[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]set_property PACKAGE_PIN W13 [get_ports {sw[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}]set_property PACKAGE_PIN V2 [get_ports {sw[8]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}]set_property PACKAGE_PIN T3 [get_ports {sw[9]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}]## sw[15]set_property PACKAGE_PIN R2 [get_ports {clr}]set_property IOSTANDARD LVCMOS33 [get_ports {clr}]## 7-seg displayset_property PACKAGE_PIN W4 [get_ports {display_out[10]}]set_property PACKAGE_PIN V4 [get_ports {display_out[9]}]set_property PACKAGE_PIN U4 [get_ports {display_out[8]}]set_property PACKAGE_PIN U2 [get_ports {display_out[7]}]set_property PACKAGE_PIN W7 [get_ports {display_out[6]}]set_property PACKAGE_PIN W6 [get_ports {display_out[5]}]set_property PACKAGE_PIN U8 [get_ports {display_out[4]}]set_property PACKAGE_PIN V8 [get_ports {display_out[3]}]set_property PACKAGE_PIN U5 [get_ports {display_out[2]}]set_property PACKAGE_PIN V5 [get_ports {display_out[1]}]set_property PACKAGE_PIN U7 [get_ports {display_out[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[9]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[8]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[7]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[6]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[5]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[4]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[10]}]四、实验结果1基础结果图2.进阶结果图进阶实验成品效果说明:进阶视频演示:正确示范:密码输入错误示范:五、实验总结1.通过本次实验了解了时钟信号的作用原理以及对时序电路的控制机理。

数字系统有两大类有限状态机(Finite State Machine,FSM):Moore状态机和Mealy 状态机。

Moore状态机其最大特点是输出只由当前状态确定,与输入无关。

Moore状态机的状态图中的每一个状态都包含一个输出信号。

这是一个典型的Moore状态机的状态跳转图,x、y、z是输入,a、b、c是输出。

Mealy状态机它的输出不仅与当前状态有关系,而且与它的输入也有关系,因而在状态图中每条转移边需要包含输入和输出的信息。

状态编码数字逻辑系统状态机设计中常见的编码方式有:二进制码(Binary码)、格雷码(Gray 码)、独热码(One-hot码)以及二一十进制码(BCD码)。

格雷码的特点:相邻的两个码组之间仅有一位不同。

普通二进制码与格雷码之间可以相互转换。

二进制码转换为格雷码:从最右边一位起,一次与左边一位“异或”,作为对应格雷码该位的值,最左边的一位不变(相当于最左边是0)。

格雷码转换为二进制码:从左边第二位起,将每一位与左边一位解码后的值“异或”,作为该解码后的值(最左边的一位依然不变)。

独热码又分为独热1码和独热0码,是一种特殊的二进制编码方式。

当任何一种状态有且仅有一个1时,就是独热1码,相反任何一种状态有且仅有一个0时,就是独热0码。

状态机的描述状态机有三种描述方式:一段式状态机、两段式状态机、三段式状态机。

下面就用一个小例子来看看三种方式是如何实现的。

(各种图片,各种坑爹啊 - -!)一段式状态机当把整个状态机卸载一个always模块中,并且这个模块既包含状态转移,又含有组合逻辑输入/输出时,称为一段式状态机。

不推荐采用这种状态机,因为从代码风格方面来讲,一般都会要求把组合逻辑和时序逻辑分开;从代码维护和升级来说,组合逻辑和书序逻辑混合在一起不利于代码维护和修改,也不利于约束。

1.//一段式状态机来实现:在异步复位信号的控制下,一段式状态机进入IDLE2.//状态,q_sig4被复位,一旦sig1或者sig2有效,状态机进入WAIT状态,如果3.//sig1和sig2同时有效,那么状态机进入DONE状态,4.//如果sig4还有效,那么q_sig4置位,同时状态机进入IDLE状态。

数字电路状态机设计数字电路状态机是一种在特定输入条件下,产生特定输出逻辑电路的设计。

它通常用于处理控制信号和顺序逻辑的应用中。

本文将介绍数字电路状态机的基本概念、设计流程以及应用实例。

一、数字电路状态机的概念数字电路状态机是一种使用状态和状态转移来描述电路行为的模型。

它由状态寄存器、组合逻辑和组合逻辑控制电路组成。

状态寄存器用于存储当前状态,组合逻辑决定下一个状态和输出的逻辑条件。

二、数字电路状态机的设计流程1. 确定状态和输入信号:首先确定设计中所需要的状态数量和输入信号的种类和数量。

状态可以是离散的值,如0、1等,也可以是更复杂的状态。

2. 绘制状态转移图:根据状态数量和输入信号的种类和数量,绘制状态转移图。

状态转移图是一种有向图,用于描述状态之间的转移条件和动作。

3. 设计状态表:根据状态转移图,设计状态表。

状态表列出了每个状态的转移条件、动作和输出。

4. 实现状态转移表:将状态表转化为逻辑电路,实现状态转移逻辑和输出逻辑。

5. 验证和测试:对设计进行验证和测试,确保状态机在各种输入条件下都能正确地工作。

三、数字电路状态机的应用实例数字电路状态机广泛应用于各种控制和顺序逻辑的场景,下面是一个以闹钟为例的应用实例。

假设我们需要设计一个简单的闹钟电路,具有以下要求:1. 闹钟有两种状态:开和关。

2. 闹钟有两个输入:按钮A(表示设置时间)和按钮B(表示开关闹钟)。

3. 当闹钟处于关闭状态下,按下按钮B时,闹钟进入开启状态,并发出响铃信号。

4. 当闹钟处于开启状态下,按下按钮B时,闹钟进入关闭状态,停止响铃。

通过状态机设计流程,我们可以得到以下结果:1. 状态:开(S1)和关(S0)。

2. 输入信号:按钮A(I1)和按钮B(I0)。

3. 输出信号:响铃(O)。

根据设计要求,我们绘制状态转移图,如下所示:```S0───┐┌──────┐┌──────┐││ I1=1 ││ I1=0 │S1───┘└──────┘└──────┘ I0=1 I0=1```根据状态转移图,设计状态表如下:```当前状态输入下一个状态输出 S0 0 S0 0S0 1 S1 0S1 0 S0 1S1 1 S1 0```根据状态表,实现状态转移表如下:```当前状态输入下一个状态输出 S0 00 S0 0S0 01 S1 0S1 11 S1 0```最后,根据状态转移表实现逻辑电路并进行验证和测试。

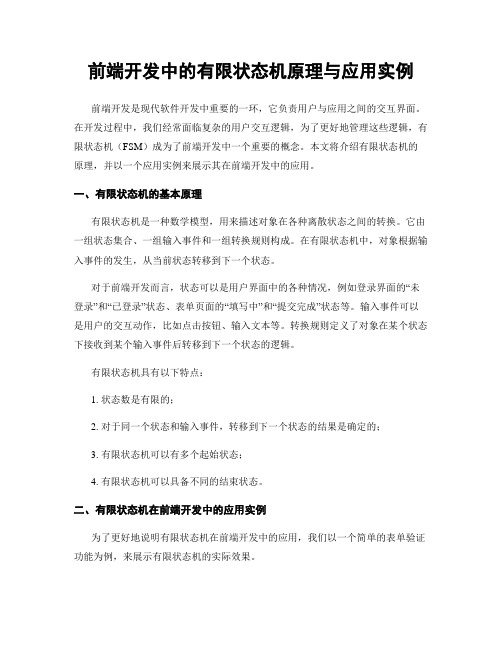

前端开发中的有限状态机原理与应用实例前端开发是现代软件开发中重要的一环,它负责用户与应用之间的交互界面。

在开发过程中,我们经常面临复杂的用户交互逻辑,为了更好地管理这些逻辑,有限状态机(FSM)成为了前端开发中一个重要的概念。

本文将介绍有限状态机的原理,并以一个应用实例来展示其在前端开发中的应用。

一、有限状态机的基本原理有限状态机是一种数学模型,用来描述对象在各种离散状态之间的转换。

它由一组状态集合、一组输入事件和一组转换规则构成。

在有限状态机中,对象根据输入事件的发生,从当前状态转移到下一个状态。

对于前端开发而言,状态可以是用户界面中的各种情况,例如登录界面的“未登录”和“已登录”状态、表单页面的“填写中”和“提交完成”状态等。

输入事件可以是用户的交互动作,比如点击按钮、输入文本等。

转换规则定义了对象在某个状态下接收到某个输入事件后转移到下一个状态的逻辑。

有限状态机具有以下特点:1. 状态数是有限的;2. 对于同一个状态和输入事件,转移到下一个状态的结果是确定的;3. 有限状态机可以有多个起始状态;4. 有限状态机可以具备不同的结束状态。

二、有限状态机在前端开发中的应用实例为了更好地说明有限状态机在前端开发中的应用,我们以一个简单的表单验证功能为例,来展示有限状态机的实际效果。

假设我们有一个用户注册页面,在用户点击提交按钮后,需要对表单数据进行合法性验证。

我们可以使用有限状态机来管理整个验证流程。

首先,我们可以定义三个状态:“准备中”、“验证中”和“完成”。

初始状态为“准备中”。

用户点击提交按钮后,状态从“准备中”转移到“验证中”状态。

在“验证中”状态下,我们可以进行表单数据的合法性验证操作。

如果验证通过,则状态转移到“完成”状态,并完成表单的提交操作。

如果验证未通过,则状态返回到“准备中”状态。

这个过程可以使用如下的有限状态机图表示:(图中省略)有限状态机的实现可以使用各种编程语言和工具,例如JavaScript中的状态机库xstate。

verilog状态机设计例题Verilog状态机设计是数字电路设计中的重要内容,它通常用于控制系统和序列逻辑电路的设计。

在Verilog中,状态机通常使用行为级描述或者结构级描述来实现。

下面我将从例题的角度来介绍Verilog状态机设计。

假设我们要设计一个简单的2位计数器,它可以按顺序循环输出00、01、10、11、00……的计数序列。

我们可以使用Verilog来实现这个状态机。

首先,我们需要定义状态机的状态和状态转移。

在这个例子中,我们有4个状态:S0、S1、S2和S3,分别对应00、01、10、11四种计数状态。

状态转移规则如下:当当前状态为S0时,下一个状态为S1;当当前状态为S1时,下一个状态为S2;当当前状态为S2时,下一个状态为S3;当当前状态为S3时,下一个状态为S0。

接下来,我们可以使用Verilog的行为级描述来实现这个状态机。

下面是一个简单的Verilog代码示例:verilog.module counter (。

input clk, // 时钟输入。

input rst, // 复位输入。

output reg [1:0] count // 2位计数输出。

);// 定义状态。

typedef enum {S0, S1, S2, S3} state_type;reg [1:0] state, next_state;// 状态转移逻辑。

always @(posedge clk or posedge rst) begin.if (rst) begin.state <= S0; // 复位时初始状态为S0。

end.else begin.state <= next_state; // 根据下一个状态更新当前状态。

end.end.// 下一个状态逻辑。

case (state)。

S0: next_state = S1;S1: next_state = S2;S2: next_state = S3;S3: next_state = S0;default: next_state = S0;endcase.end.// 输出逻辑。

verilog 状态机写法Verilog是一种硬件描述语言,常用于设计和开发数字电路和系统。

在Verilog中,状态机是一种常用的建模方法,用于描述系统的状态和状态转移。

Verilog的状态机可以使用不同的写法来实现,通常有两种主要的方法:行为级描述和结构级描述。

行为级描述是一种以状态转移的逻辑和状态转移的条件为基础的写法。

在行为级描述中,我们需要定义状态变量和状态转移条件,然后使用if-else语句来实现状态转移逻辑。

以下是一个简单的例子,使用行为级描述写法实现一个简单的二进制计数器状态机:```verilogmodule binary_counter(input clk,input reset,output reg [3:0] count);reg [3:0] next_count;always @(posedge clk or posedge reset) beginif (reset) begincount <= 4'b0000;end else begincase (count)4'b0000: next_count = 4'b0001;4'b0001: next_count = 4'b0010;4'b0010: next_count = 4'b0011;4'b0011: next_count = 4'b0100;4'b0100: next_count = 4'b0101;4'b0101: next_count = 4'b0110;4'b0110: next_count = 4'b0111;4'b0111: next_count = 4'b1000;4'b1000: next_count = 4'b1001;4'b1001: next_count = 4'b0000;default: next_count = 4'b0000;endcasecount <= next_count;endendendmodule```在上面的例子中,我们定义了一个4位的计数器变量`count`,并在always块中定义了状态转移逻辑。

verilog优化逻辑的例子Verilog是一种硬件描述语言,用于描述数字逻辑电路。

在设计和实现数字逻辑电路时,优化逻辑是至关重要的。

通过优化逻辑可以提高电路的性能、减少功耗、降低成本等。

下面列举了10个以Verilog优化逻辑的例子。

1. 使用位移操作代替乘法运算:在一些情况下,乘法运算需要大量的硬件资源,可以使用位移操作来代替乘法运算,从而减少硬件资源的使用。

2. 使用并行操作代替串行操作:在一些情况下,串行操作需要较长的延迟时间,可以使用并行操作来代替串行操作,从而减少延迟时间。

3. 优化状态机:对于复杂的状态机,可以通过精简状态转移图或者使用更高效的状态编码方式来优化状态机的逻辑。

4. 使用查找表代替复杂的逻辑判断:对于一些复杂的逻辑判断,可以使用查找表来代替,从而简化逻辑电路。

5. 使用流水线技术:对于一些需要处理大量数据的电路,可以使用流水线技术将处理过程划分为多个阶段,从而提高电路的吞吐量。

6. 使用FIFO缓冲区:在一些需要缓存数据的电路中,使用FIFO缓冲区可以有效地管理数据的输入和输出,提高电路的处理能力。

7. 使用复用器和选择器:在一些需要多路复用和选择的电路中,使用复用器和选择器可以减少硬件资源的使用,简化电路的逻辑。

8. 使用加法器代替减法器:在一些需要进行减法运算的电路中,可以通过转换运算表达式,使用加法器来代替减法器,从而减少硬件资源的使用。

9. 使用编码器和解码器:在一些需要进行编码和解码的电路中,使用编码器和解码器可以简化逻辑电路,降低硬件资源的使用。

10. 使用异步时序逻辑:在一些需要处理异步信号的电路中,使用异步时序逻辑可以提高电路的响应速度和稳定性。

通过以上的优化技术,可以有效地提高数字逻辑电路的性能和效率。

在实际应用中,根据具体的设计需求和资源限制,选择适合的优化技术进行逻辑优化,可以使电路更加高效、可靠和经济。

Digital System Design

1

2011/6/21

Computer Faculty of Guangdong University of Technology

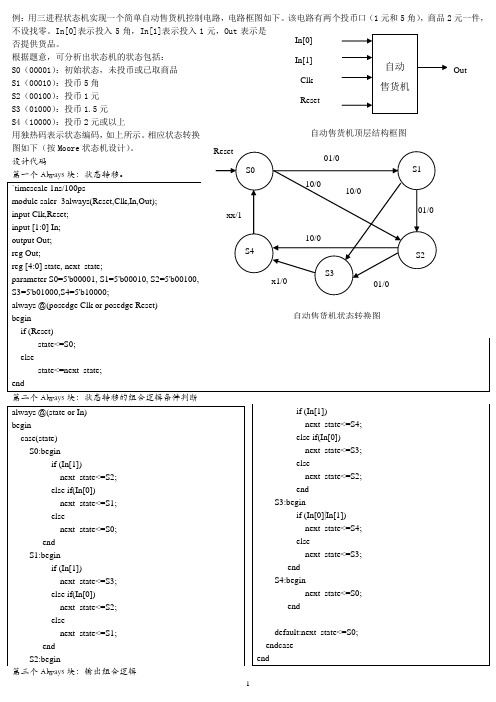

例:用三进程状态机实现一个简单自动售货机控制电路,电路框图如下。

该电路有两个投币口(1元和5角),商品2元一件,不设找零。

In[0]表示投入5角,In[1]表示投入1元,Out 表示是否提供货品。

Digital System Design

2

2011/6/21

Computer Faculty of Guangdong University of Technology

根据题意,可分析出状态机的状态包括: S0(00001):初始状态,未投币或已取商品 S1(00010):投币5角 S2(00100):投币1元 S3(01000):投币1.5元 S4(10000):投币2元或以上

用独热码表示状态编码,如上所示。

相应状态转换图如下(按Moore 状态机设计)。

Digital System Design

3

2011/6/21

Computer Faculty of Guangdong University of Technology

自动售货机状态转换图

Digital System Design

4

2011/6/21

Computer Faculty of Guangdong University of Technology

设计代码

第一个Always 块:状态转移。

Digital System Design

5

2011/6/21

Computer Faculty of Guangdong University of Technology

第二个Always 块:状态转移的组合逻辑条件判断

Digital System Design

6

2011/6/21

Computer Faculty of Guangdong University of Technology

第三个Always 块:输出组合逻辑

Digital System Design

7

2011/6/21

Computer Faculty of Guangdong University of Technology

测试平台代码

Digital System Design

8

2011/6/21

Computer Faculty of Guangdong University of Technology

功能仿真结果

Digital System Design

9

2011/6/21

Computer Faculty of Guangdong University of Technology

综合结果。