半导体制造工艺简介

- 格式:ppt

- 大小:2.07 MB

- 文档页数:67

半导体制造工艺范文1.晶圆制备:晶圆是制造半导体器件的基础。

可通过切割单晶硅棒或者熔融硅制备。

制备好的晶圆表面需要经过化学机械抛光,使其表面光滑。

2.掩膜制备:掩膜是指将特定模式转移到晶圆表面的层。

通过光刻技术,在掩膜层上照射紫外线光束,使其形成特定模式。

常用掩膜材料有光刻胶。

3.刻蚀:刻蚀是通过化学或物理的方式去除掩膜层以外的材料,形成所需的结构。

常用的刻蚀方法有湿刻蚀和干刻蚀。

湿刻蚀使用化学溶液去除非掩膜区域的材料,干刻蚀则使用离子轰击或者等离子体气体去除材料。

4.离子注入:离子注入是指向掺杂原子加速并注入到晶圆内部,改变其电学性质。

通过掩膜层上开口处的掺杂窗口进行注入,常用的离子有硼、磷等。

5.扩散:扩散是将注入到晶圆内的掺杂原子在高温下扩散扩展,形成特定的杂质浓度分布。

扩散可以使半导体材料的电学性能得到改善。

通常在氮气或者氢气气氛中进行。

6.金属沉积:金属沉积是将金属材料沉积在晶圆表面,用于电极、导线等器件的制作。

通过化学气相沉积或者物理气相沉积等方法进行。

7.封装:封装是将制造好的芯片装配到封装材料中,制作成可使用的半导体器件。

常用的封装方法有芯片焊接在载体上并用封装材料覆盖,然后进行焊接。

此外,半导体制造工艺还包括成品测试和质量控制等环节。

成品测试是指对制造好的半导体器件进行功能性、电学性能等方面的测试,以验证其质量和性能是否达到要求。

质量控制是指在制造过程中对各个步骤进行监控和调整,以确保最终的产品达到规定的质量标准。

总结而言,半导体制造工艺是一个复杂严谨的过程,需要精确的控制和高精度的设备支持。

只有通过严格的工艺流程和质量控制,才能制备出性能稳定可靠的半导体器件。

这些器件广泛应用于电子、通信、计算机等领域,对现代社会的发展具有重要作用。

八大半导体工艺顺序剖析八大半导体工艺顺序剖析在现代科技领域中,半导体材料和器件扮演着重要的角色。

作为电子设备的基础和核心组件,半导体工艺是半导体制造过程中不可或缺的环节。

有关八大半导体工艺顺序的剖析将会有助于我们深入了解半导体制造的工作流程。

本文将从简单到复杂,逐步介绍这八大工艺的相关内容。

1. 排版工艺(Photolithography)排版工艺是半导体制造过程中的首要步骤。

它使用光刻技术,将设计好的电路图案转移到硅晶圆上。

排版工艺需要使用光刻胶、掩膜和曝光设备等工具,通过逐层叠加和显影的过程,将电路图案转移到硅晶圆上。

2. 清洗工艺(Cleaning)清洗工艺在排版工艺之后进行,用于去除光刻胶和其他污染物。

清洗工艺可以采用化学溶液或高纯度的溶剂,保证硅晶圆表面的干净和纯净。

3. 高分辨率电子束刻蚀(High-Resolution Electron BeamLithography)高分辨率电子束刻蚀是一种先进的制造技术。

它使用电子束在硅晶圆表面进行刻蚀,以高精度和高分辨率地制作微小的电路图案。

4. 电子束曝光系统(Electron Beam Exposure Systems)电子束曝光系统是用于制造高分辨率电子束刻蚀的设备。

它具有高能量电子束发射器和复杂的控制系统,能够精确控制电子束的位置和强度,实现微米级别的精细曝光。

5. 高能量离子注入(High-Energy Ion Implantation)高能量离子注入是半导体器件制造中的一项重要工艺。

通过将高能量离子注入到硅晶圆表面,可以改变硅晶圆的电学性质,实现电路中的控制和测量。

6. 薄膜制备与沉积(Film Deposition)薄膜制备与沉积是制造半导体器件的关键工艺之一。

这个工艺将薄膜材料沉积在硅晶圆表面,包括化学气相沉积、物理气相沉积和溅射等方法。

这些薄膜能够提供电介质、导电材料或阻挡层等功能。

7. 设备和工艺完善(Equipment and Process Optimization)设备和工艺完善的步骤是优化半导体制造工艺的关键。

半导体制造工艺技术半导体制造工艺技术是指用于生产半导体器件的工艺步骤和方法。

半导体器件是现代电子设备中最基本的组成部分,包括晶体管、集成电路等。

半导体制造工艺技术是将半导体材料加工成器件的关键环节,对于器件的性能和质量有着重要影响。

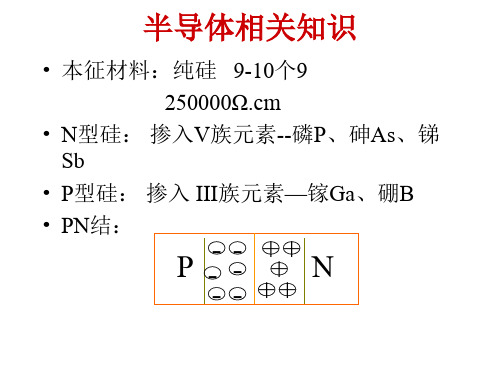

首先,半导体制造工艺技术的第一步是选择合适的半导体材料。

常用的半导体材料有硅、砷化镓等。

这些材料具有较好的导电性和半导性,能够在一定条件下控制电流的传导。

接下来,半导体制造工艺技术的第二步是进行材料清洁和去除氧化层。

在制造过程中,材料表面可能会附着一些杂质和氧化层,会影响器件的性能。

因此,将材料进行清洁和去除氧化层是非常重要的步骤。

第三步是进行材料的掺杂和扩散。

掺杂是向材料中加入一定浓度的所需的杂质元素,以改变材料的导电性。

扩散是使掺杂材料均匀分布在整个材料中,以获得稳定的性能。

第四步是进行光刻和蚀刻。

光刻是在材料表面涂覆光刻胶,通过光刻机械刻蚀模板上的图案,以形成器件的结构。

蚀刻是使用化学物质去除材料表面的不需要的部分。

第五步是进行金属沉积和金属化。

金属沉积是将金属材料沉积在材料表面,以与器件的其他部分连接。

金属化是利用蚀刻制造导线和联系器件。

第六步是进行热处理和包封。

热处理是使用高温处理器件,以提高其电学性能和结构稳定性。

包封是将器件用封装材料密封,以保护器件并提供连接接口。

最后,进行测试和质检。

测试是检验制造的器件是否符合要求。

质检是对制造过程中的每个步骤进行检查,以确保器件的质量和可靠性。

总的来说,半导体制造工艺技术是一项复杂而精密的工艺,需要严格控制每个步骤和参数,以确保制造出高性能、高质量的半导体器件。

随着科技的进步,半导体制造工艺技术也在不断创新和发展,为电子产业的发展提供了强有力的支持。

半导体制造工艺技术是一门关乎现代电子产业发展的重要技术,其应用范围广泛,涵盖了从传统的晶体管制造到先进的集成电路制造等多个领域。

随着电子产品的普及和需求的不断增长,半导体制造工艺技术也在不断发展和改进,以满足市场的需求。

半导体制造工艺流程简介导言:一、晶圆加工晶圆加工是制造集成电路的第一步。

它包括以下过程:1.晶圆生长:通过化学气相沉积或金属有机化学气相沉积等方法,在硅片基底上生长单晶硅。

这个过程需要非常高的温度和压力。

2.剥离:将生长的单晶硅从基底上剥离下来,并校正其表面的缺陷。

3.磨削和抛光:使用机械研磨和化学力学抛光等方法,使晶圆的表面非常光滑。

二、晶圆清洗晶圆清洗是为了去除晶圆表面的杂质和污染物,以保证后续工艺的顺利进行。

清洗过程包括以下步骤:1.热酸洗:利用强酸(如硝酸和氢氟酸)将晶圆浸泡,以去除表面的金属杂质。

2.高温氧化:在高温下将晶圆暴露在氧气中,通过热氧化去除有机杂质和表面缺陷。

3.金属清洗:使用氢氟酸和硝酸等强酸,去除金属杂质和有机污染物。

4.DI水清洗:用去离子水清洗晶圆,以去除化学清洗剂的残留。

三、晶圆制备晶圆制备是将晶圆上的材料和元件结构形成的过程。

它包括以下过程:1.掩膜制作:将光敏材料涂覆在晶圆表面,通过光刻技术进行曝光和显影,形成图案化的光刻胶掩膜。

2.沉积:通过物理气相沉积或化学气相沉积等方法,在晶圆上沉积材料层,如金属、氧化物、硅等。

3.腐蚀:采用湿法或干法腐蚀等技术,去除晶圆上不需要的材料,形成所需的结构。

4.清洗:再次进行一系列清洗步骤,以去除腐蚀产物和掩膜残留物,保证材料层的质量。

四、材料获取材料获取是指在晶圆上制造晶体管、电阻器、电容器等器件结构的过程。

它包括以下步骤:1.掺杂:通过离子注入或扩散等方法,在晶圆上引入有选择性的杂质,以改变材料的导电性或断电性能。

2.退火:通过高温热处理,消除杂质引入过程中的晶格缺陷,并使掺杂的材料达到稳定状态。

3.金属-绝缘体-金属(MIM)沉积:在晶圆上沉积金属、绝缘体和金属三层结构,用于制造电容器。

4.金属-绝缘体(MIS)沉积:在晶圆上沉积金属和绝缘体两层结构,用于制造晶体管的栅极。

五、封装和测试封装是将晶圆上制造的芯片放在封装底座上,并封装成可插入其他设备的集成电路。

半导体工艺流程简介

《半导体工艺流程简介》

半导体工艺流程是指在半导体器件制造过程中所采用的一系列工艺步骤。

它包括了晶圆加工、器件制造和封装测试三个主要环节,每个环节又包含了不同的工艺步骤。

首先是晶圆加工。

这个过程包括了晶圆的清洁、去除氧化层、光刻、蚀刻、离子注入、扩散和沉积等步骤。

光刻是把芯片上的线路图案印制到光敏胶上,蚀刻是把芯片上不需要的部分去除,离子注入是通过向晶圆注入掺杂物改变材料的电子性质,扩散是在晶圆中扩散掺杂物,沉积则是在晶圆上沉积导体或绝缘体材料。

接下来是器件制造。

这个过程包括了制造晶体管、电容器、电阻器等器件,并将它们连接成一个完整的电路。

这个过程需要通过光刻、蚀刻、金属沉积、刻蚀、退火、金属化、绝缘层沉积等一系列工艺步骤完成。

最后是封装测试。

在这一步骤中,芯片被封装成一个完整的器件,并通过测试来检测器件的性能和质量。

封装是将芯片封装在塑料或陶瓷封装体内,并连接上引脚;测试则是通过测试设备对器件进行功能、可靠性和一致性等方面的测试。

总的来说,半导体工艺流程包含了各种化学、物理和电子工艺步骤,它是半导体器件制造的基础,对器件的性能和可靠性有

着重要的影响。

随着半导体技术的不断发展,工艺流程也在不断地更新和改进,以适应新的器件制造需求。

ws 半导体工艺WS半导体工艺是一种常用的半导体制造工艺,它在集成电路的制造过程中起到了重要的作用。

本文将介绍WS半导体工艺的原理、应用以及未来的发展趋势。

一、WS半导体工艺的原理WS半导体工艺,即湿法硅工艺(Wet Silicon),是一种利用湿法处理硅片表面的工艺。

在WS工艺中,硅片经过一系列的清洗和蚀刻处理后,再进行高温烘烤,最后形成所需的结构和电路。

WS工艺的主要步骤包括:清洗、蚀刻、沉积和退火。

清洗过程中,通过化学溶液去除硅片表面的杂质和污染物,保证硅片的纯净度。

蚀刻过程中,利用化学溶液或气体反应,去除硅片表面的一部分材料,使其形成所需的结构。

沉积过程中,通过物理或化学方法,在硅片表面沉积一层新的材料,用于电路的隔离或保护。

退火过程中,通过高温处理,使硅片中的材料重新排列和结晶,提高电路的性能和稳定性。

二、WS半导体工艺的应用WS半导体工艺广泛应用于集成电路的制造过程中。

它可以用于制造各种类型的晶体管、二极管、电容器等器件。

WS工艺具有处理速度快、工艺稳定性好、成本低廉等优点,因此在半导体行业得到了广泛的应用。

在集成电路的制造过程中,WS工艺主要用于形成电路的隔离层和保护层。

通过沉积一层氧化硅或氮化硅材料,可以隔离不同的电路单元,避免干扰和电流泄漏。

同时,这些材料也可以保护电路不受外界环境的影响,提高电路的可靠性和稳定性。

三、WS半导体工艺的发展趋势随着科技的不断进步,WS半导体工艺也在不断发展和改进。

未来的发展趋势主要体现在以下几个方面:1. 纳米工艺的发展:随着集成电路的尺寸越来越小,WS工艺也在不断追求更高的分辨率和精度。

新的纳米工艺技术将进一步提高WS 工艺的制造效率和精度,使得集成电路的性能得到进一步提升。

2. 新材料的应用:随着新材料的不断涌现,WS工艺也将应用更多的新材料。

这些新材料具有更好的电学性能和机械性能,可以提高集成电路的性能和可靠性。

3. 三维集成电路的发展:随着三维集成电路的兴起,WS工艺也将面临新的挑战和机遇。

半导体工艺介绍

在现代科技领域中,半导体技术一直扮演着至关重要的角色。

半导体工艺是指制备半导体器件所需的工艺流程和技术。

通过一系列步骤,半导体材料被精确地处理和加工,最终形成各种高性能的电子器件。

下面将介绍一些常见的半导体工艺。

晶体生长

晶体生长是半导体工艺中至关重要的一部分。

在晶体生长过程中,高纯度的半导体原料被加热,液态或气态的半导体材料被沉积在晶体上。

这个过程对半导体器件的电学性能至关重要。

光刻工艺

光刻工艺是半导体工艺中一项关键的步骤,用于在半导体晶片表面定位并加工各种微小的结构。

通过将光源通过光掩膜,将图案投影在光敏剂上,然后对光敏剂进行显影和溅射,形成半导体晶片上所需的微米结构。

清洗工艺

清洗工艺是半导体制造中不可或缺的一环。

在材料处理过程中,表面会附着各种杂质和不纯物,为了确保半导体器件性能的稳定和可靠,清洗工艺起着至关重要的作用。

清洗过程通过使用不同的化学溶液和清洗设备,将表面的不纯物去除,确保器件的质量。

沉积工艺

沉积工艺是将半导体原料沉积在基片上的一种工艺。

通过化学气相沉积或物理气相沉积等方法,将所需的半导体材料以薄膜的形式沉积在基片表面,形成各种功能性薄膜,用于制备半导体器件。

退火工艺

退火工艺在半导体工艺中扮演着至关重要的角色。

在晶片制备完成后,通过高温处理,使半导体材料内部结构重新排列,消除杂质和缺陷,提高器件的性能和稳定性。

以上是半导体工艺中的一些常见步骤和技术,半导体工艺的发展将进一步推动科技的发展,为人类带来更多的便利和可能性。

半导体全⾯分析:制造三⼤⼯艺,晶圆四⼤⼯艺!技术:设计流程 100 亿个晶体管在指甲盖⼤⼩的地⽅组成电路,想想就头⽪发⿇!⼀个路⼝红绿灯设置不合理,就可能导致⼤⽚堵车,电⼦在芯⽚上跑来跑去,稍微有个 PN 结出问题,电⼦同样会堵车,所以芯⽚的设计异常重要 芯⽚制造的过程就如同⽤乐⾼盖房⼦⼀样,先有晶圆作为地基,再层层往上叠的芯⽚制造流程后,就可产出必要的芯⽚(后⾯会介绍),然⽽,没有设计图,拥有再强制造能⼒都没有⽤1. 规格制定在 IC 设计中,最重要的步骤就是规格制定,这个步骤就像是在设计建筑前,先决定要⼏间房间、浴室,有什么建筑法规需要遵守,在确定好所有的功能之后在进⾏设计,这样才不⽤再花额外的时间进⾏后续修改第⼀步:确定 IC 的⽬的、效能为何,对⼤⽅向做设定第⼆步:察看需要何种协议,否则芯⽚将⽆法和市⾯上的产品相容第三步:确⽴ IC 的实作⽅法,将不同功能分配成不同的单元,并确⽴不同单元间连结的⽅法,如此便完成规格的制定 2. 设计芯⽚细节这个步骤就像初步记下建筑的规画,将整体轮廓描绘出来,⽅便后续制图。

在 IC 芯⽚中,便是使⽤硬体描述语⾔(HDL)将电路描写出来。

常使⽤的 HDL 有Verilog、VHDL等,藉由程式码便可轻易地将⼀颗 IC 功能表达出来。

接着就是检查程式功能的正确性并持续修改,直到它满⾜期望的功能为⽌ 3. 设计蓝图在 IC 设计中,逻辑合成这个步骤便是将确定⽆误的 HDL code,放⼊电⼦设计⾃动化⼯具(EDA tool),让电脑将 HDL code 转换成逻辑电路,产⽣如下的电路图,之后,反复的确定此逻辑闸设计图是否符合规格并修改,直到功能正确为⽌ 4. 电路布局与绕线将合成完的程式码再放⼊另⼀套EDA tool,进⾏电路布局与绕线(Place And Route)。

在经过不断的检测后,便会形成如下的电路图。

图中可以看到蓝、红、绿、黄等不同颜⾊,每种不同的颜⾊就代表着⼀张光罩 ▲常⽤的演算芯⽚- FFT 芯⽚,完成电路布局与绕线的结果 5.光罩⼀颗IC 会产⽣多张的光罩,这些光罩有上下层的分别,每层有各⾃的任务。

一、引言Polymide半导体工艺制程是一种重要的半导体制造技术,其在电子行业中具有广泛的应用。

本文将对Polymide半导体工艺制程进行全面介绍,包括其定义、原理、工艺流程和应用领域等方面。

二、Polymide半导体工艺制程的定义Polymide是一种高分子材料,具有优异的绝缘性能和化学稳定性。

在半导体制造领域,Polymide被用作一种重要的材料,用于制作半导体器件的绝缘层。

Polymide半导体工艺制程就是利用Polymide材料来制作半导体器件的工艺技术。

三、Polymide半导体工艺制程的原理Polymide在半导体器件中的应用主要基于其良好的绝缘性能和化学稳定性。

在半导体器件中,Polymide被用作绝缘层,起到隔离导电材料和保护器件的作用。

通过Polymide半导体工艺制程,可以在半导体器件的不同层次之间形成绝缘层,从而实现器件的稳定性和可靠性。

四、Polymide半导体工艺制程的工艺流程Polymide半导体工艺制程包括多个关键步骤,一般包括准备基板、涂覆Polymide、光刻、蚀刻、退火等工艺步骤。

具体工艺流程可以根据实际情况进行调整,但以上几个步骤是Polymide半导体工艺制程的核心步骤。

1. 准备基板:首先需要选择适合的半导体基板,通常是硅片或玻璃基板。

2. 涂覆Polymide:利用涂覆机将Polymide溶液均匀涂覆在基板表面,并经过烘烤使其形成均匀的绝缘层。

3. 光刻:利用光刻技术,在Polymide层上形成所需的图案。

4. 蚀刻:利用化学蚀刻或物理蚀刻技术,将Polymide层非光刻区域去除。

5. 退火:对蚀刻后的Polymide层进行退火处理,提高其物理性能和化学稳定性。

五、Polymide半导体工艺制程的应用领域Polymide半导体工艺制程在电子行业中具有广泛的应用,主要包括集成电路、传感器、显示器件等领域。

在集成电路制造中,Polymide被用作多层金属线路的绝缘层;在传感器制造中,Polymide被用作传感器的封装层;在显示器件制造中,Polymide被用作柔性显示器的基底材料。

半导体制程简介半导体制程是指制造半导体器件所需的一系列工艺步骤和设备。

它是将材料转换为具有特定功能的半导体器件的过程,多数情况下是芯片制造的关键部分。

半导体制程通常分为六个主要步骤:前道工艺、IC 设计、曝光与衬底处理、薄膜沉积、刻蚀与清洗、以及后道工艺。

前道工艺是半导体制程的起始阶段。

在这个阶段,制造商会选择适合的衬底材料(通常是硅),并使用一系列的物理和化学方法准备它,以便于后续的加工。

IC 设计是将半导体器件的功能、结构和电路设计成电子文件的过程。

这些文件将被用于后续的曝光与衬底处理。

曝光与衬底处理是半导体制程的关键步骤之一。

在这个步骤中,使用光刻机将设计好的电子文件投射到光敏材料上,形成模式。

然后,通过化学方法去除暴露的材料,从而得到衬底上的所需结构。

这些步骤会多次重复,以逐渐形成多层结构。

在薄膜沉积阶段,使用化学蒸气沉积(CVD)或物理蒸镀(PVD)等方法将薄膜材料沉积到衬底上。

这些膜层将用于实现器件的不同功能,如导电层、绝缘层和隔离层等。

刻蚀与清洗是将多余的材料从衬底上去除的过程。

使用化学或物理方法,将不需要的材料刻蚀掉,并进行清洗和检查,确保器件的质量和一致性。

后道工艺是半导体制程的最后阶段。

在这个阶段中,制造商会进行结构和线路的连接,以及器件的测试和封装等。

这些步骤将半导体器件转换为实际可用的芯片。

半导体制程是一个复杂而精细的过程。

通过精确的控制和不断的优化,制造商可以获得高质量、高性能的半导体器件。

这些器件在现代技术中发挥着重要的作用,包括计算机、通信设备、消费电子产品等。

因此,半导体制程在推动科技进步和社会发展中扮演着重要的角色。

半导体制程在现代科技领域扮演着极为重要的角色。

随着信息技术的发展和人们对高性能电子设备的需求不断增长,半导体制程成为了现代社会的基石之一。

在这方面,特别值得一提的是摩尔定律。

摩尔定律是一种经验规律,它指出在相同面积上可以容纳的晶体管数量每隔大约18-24个月将翻一番,同时造价也会下降50%。

半导体主要生产工艺

半导体主要生产工艺包括:

晶圆制备:晶圆是半导体制造的基础,其质量直接影响到后续工艺的进行和最终产品的性能。

薄膜沉积:薄膜沉积技术是用于在半导体材料表面沉积薄膜的过程。

刻蚀与去胶:刻蚀是将半导体材料表面加工成所需结构的关键工艺。

离子注入:离子注入是将离子注入半导体材料中的关键工艺。

退火与回流:退火与回流是使半导体材料内部的原子或分子的运动速度减缓,使偏离平衡位置的原子或分子回到平衡位置的工艺。

金属化与互连:金属化与互连是利用金属材料制作导电线路,实现半导体器件间的电气连接的过程。

测试与封装:测试与封装是确保半导体器件的质量和可靠性的必要环节。

半导体的工艺的四个重要阶段是:

原料制作阶段:为制造半导体器件提供必要的原料。

单晶生长和晶圆的制造阶段:为制造半导体器件提供必要的晶圆。

集成电路晶圆的生产阶段:在制造好的晶圆上,通过一系列的工艺流程制造出集成电路。

集成电路的封装阶段:将制造好的集成电路封装起来,便于安装和使用。

半导体材料有以下种类:

元素半导体:在元素周期表的ⅢA族至IVA族分布着11种具有半导性的元素,其中C表示金刚石。

无机化合物半导体:分二元系、三元系、四元系等。

有机化合物半导体:是指以碳为主体的有机分子化合物。

非晶态与液态半导体。

word半导体制造工艺NPN高频小功率晶体管制造的工艺流程为:外延片——编批——清洗——水汽氧化——一次光刻——检查——清洗——干氧氧化——硼注入——清洗——UDO淀积——清洗——硼再扩散——二次光刻——检查——单结测试——清洗——干氧氧化——磷注入——清洗——铝下CVD——清洗——发射区再扩散——三次光刻——检查——双结测试——清洗——铝蒸发——四次光刻——检查——氢气合金——正向测试——清洗——铝上CVD——检查——五次光刻——检查——氮气烘焙——检查——中测——中测检查——粘片——减薄——减薄后处理——检查——清洗——背面蒸发——贴膜——划片——检查——裂片——外观检查——综合检查——入中间库。

PNP小功率晶体管制造的工艺流程为:外延片——编批——擦片——前处理——一次氧化——QC检查〔tox〕——一次光刻——QC检查——前处理——基区CSD涂覆——CSD预淀积——后处理——QC检查〔R□〕——前处理——基区氧化扩散——QC检查〔tox、R□〕——二次光刻——QC检查——单结测试——前处理——POCl3预淀积——后处理〔P液〕——QC检查——前处理——发射区氧化——QC检查〔tox〕——前处理——发射区再扩散〔R□〕——前处理——铝下CVD——QC检查〔tox、R□〕——前处理——HCl氧化——前处理——氢气处理——三次光刻——QC检查——追扩散——双结测试——前处理——铝蒸发——QC检查〔t Al〕——四次光刻——QC检查——前处理——氮气合金——氮气烘焙——QC检查〔ts〕——五次光刻——QC检查——大片测试——中测——中测检查〔——粘片——减薄——减薄后处理——检查——清洗——背面蒸发——贴膜——划片——检查——裂片——外观检查〕——综合检查——入中间库。

GR平面品种〔小功率三极管〕工艺流程为:编批——擦片——前处理——一次氧化——QC检查〔tox〕——一次光刻——QC检查——前处理——基区干氧氧化——QC检查〔tox〕——一GR光刻〔不腐蚀〕——GR硼注入——湿法去胶——前处理——GR基区扩散——QC检查〔Xj、R□〕——硼注入——前处理——基区扩散与氧化——QC检查〔Xj、tox、R□〕——二次光刻——QC检查——单结测试——前处理——发射区干氧氧化——QC检查〔tox〕——磷注入——前处理——发射区氧化和再扩散——前处理——POCl3预淀积〔R□〕——后处理——前处理——铝下CVD——QC检查〔tox〕——前处理——氮气退火——三次光刻——QC检查——双结测试——前处理——铝蒸发——QC检查〔t Al〕——四次光刻——QC检查——前处理——氮气合金——氮气烘焙——正向测试——五次光刻——QC检查——大片测试——中测编批——中测——中测检查——入中间库。

半导体制造主要设备及工艺流程主要设备:1.清洗设备:用于清洗硅片,去除表面的杂质和污染物。

主要有超声波清洗机和流体喷洗机。

2.涂覆设备:用于在硅片表面涂覆光刻胶。

主要有旋涂机和喷涂机。

3.曝光设备:用于将光刻胶上的图案转移到硅片上。

主要有光刻机和直写机。

4.退火设备:用于去除光刻胶和修复表面缺陷。

主要有热退火炉和激光退火机。

5.切割设备:用于将硅片切割成单个芯片。

主要有切割机和钻孔机。

6.清除设备:用于清除硅片表面的残留物。

主要有湿法清洗机和干法清洗机。

主要工艺流程:1.接收硅片:开始时,原始硅片被送至半导体制造工厂,并经过检查和测试,以确保质量符合要求。

2.清洗:硅片被放入超声波清洗机或流体喷洗机中进行清洗,以去除表面的杂质和污染物。

3.涂覆:清洗后的硅片被放入旋涂机或喷涂机中,涂覆一层光刻胶在硅片表面。

4.曝光:涂覆光刻胶的硅片被放入光刻机或直写机中,通过曝光机将图案转移到光刻胶上。

5.退火:曝光后的硅片经过热退火炉或激光退火机退火,以去除光刻胶和修复表面缺陷。

6.切割:退火后的硅片被送到切割机或钻孔机中进行切割,将硅片切割成单个芯片。

7.清除:切割后的芯片进一步进行清除,以去除硅片表面的残留物。

8.检验和测试:清除后的芯片被检查和测试,以确保质量和功能合格。

9.封装:通过封装设备将芯片封装到塑料封装中,并连接到引脚。

10.测试:封装后的芯片被送到测试设备中进行功能测试和性能评估。

11.校准:测试后的芯片也经过校准,以确保准确性和一致性。

12.包装和出货:测试和校准后,芯片被放入包装盒中,然后运送到客户。

以上是半导体制造的主要设备及工艺流程的详细介绍。

这个过程需要高度的精确性和技术要求,以确保半导体产品的质量和性能。

半导体制造工艺NPN高频小功率晶体管制造的工艺流程为:外延片——编批——清洗——水汽氧化——一次光刻——检查——清洗——干氧氧化——硼注入——清洗——UDO淀积——清洗——硼再扩散——二次光刻——检查——单结测试——清洗——干氧氧化——磷注入——清洗——铝下CVD——清洗——发射区再扩散——三次光刻——检查——双结测试——清洗——铝蒸发——四次光刻——检查——氢气合金——正向测试——清洗——铝上CVD——检查——五次光刻——检查——氮气烘焙——检查——中测——中测检查——粘片——减薄——减薄后处理——检查——清洗——背面蒸发——贴膜——划片——检查——裂片——外观检查——综合检查——入中间库。

PNP小功率晶体管制造的工艺流程为:外延片——编批——擦片——前处理——一次氧化——QC检查(tox)——一次光刻——QC检查——前处理——基区CSD涂覆——CSD预淀积——后处理——QC检查(R□)——前处理——基区氧化扩散——QC检查(tox、R□)——二次光刻——QC检查——单结测试——前处理——POCl3预淀积——后处理(P液)——QC检查——前处理——发射区氧化——QC检查(tox)——前处理——发射区再扩散(R□)——前处理——铝下CVD——QC检查(tox、R□)——前处理——HCl氧化——前处理——氢气处理——三次光刻——QC检查——追扩散——双结测试——前处理——铝蒸发——QC检查(t Al)——四次光刻——QC检查——前处理——氮气合金——氮气烘焙——QC检查(ts)——五次光刻——QC检查——大片测试——中测——中测检查(——粘片——减薄——减薄后处理——检查——清洗——背面蒸发——贴膜——划片——检查——裂片——外观检查)——综合检查——入中间库。

GR平面品种(小功率三极管)工艺流程为:编批——擦片——前处理——一次氧化——QC检查(tox)——一次光刻——QC检查——前处理——基区干氧氧化——QC检查(tox)——一GR光刻(不腐蚀)——GR硼注入——湿法去胶——前处理——GR基区扩散——QC检查(Xj、R□)——硼注入——前处理——基区扩散与氧化——QC检查(Xj、tox、R□)——二次光刻——QC检查——单结测试——前处理——发射区干氧氧化——QC检查(tox)——磷注入——前处理——发射区氧化和再扩散——前处理——POCl3预淀积(R□)——后处理——前处理——铝下CVD——QC检查(tox)——前处理——氮气退火——三次光刻——QC检查——双结测试——前处理——铝蒸发——QC检查(t Al)——四次光刻——QC检查——前处理——氮气合金——氮气烘焙——正向测试——五次光刻——QC检查——大片测试——中测编批——中测——中测检查——入中间库。