串行输入并行输出

- 格式:doc

- 大小:66.50 KB

- 文档页数:3

74LS164简介74LS164是一种8位串行输入/并行输出移位寄存器,广泛应用于数字电子领域。

它由TI(Texas Instruments)公司制造,是74系列(TTL)的一员。

功能74LS164具有以下主要功能:•8位位移寄存器:可以将8位数据进行位移操作,并将结果存储在内部存储器中。

•串行输入:通过一个输入引脚,可以逐位地输入8位数据。

•并行输出:通过8个输出引脚,可以同时输出寄存器中存储的8位数据。

引脚描述74LS164具有如下引脚:1.DS(Data Serial Input):串行数据输入引脚,用于输入通过位移操作需要存储的8位数据。

2.SHCP(Shift Clock Input):移位时钟输入引脚,用于控制位移操作的时钟信号。

3.STCP(Storage Clock Input):存储时钟输入引脚,用于控制存储数据的时钟信号。

4.GND(Ground):接地引脚。

5.Q7’(Serial Output):串行输出引脚,用于输出移位操作的结果。

6.Q0-Q6(Parallel Outputs):并行输出引脚,用于输出存储的8位数据。

7.VCC(Positive Supply):正电源引脚。

工作原理74LS164工作时,可以通过两个时钟信号控制其行为。

下面是其工作原理的描述:•存储器清零:在存储器清零时,将SHCP和STCP引脚设置为高电平,并将DS引脚设置为低电平。

此时,存储器中所有的输出引脚将保持低电平状态。

•位移操作:在进行位移操作时,将SHCP引脚设置为低电平,然后将输入引脚DS设置为要输入的数据位状态(0或1)。

接下来,通过将SHCP 引脚设置为高电平,使得数据在寄存器内进行位移,具体移位方向取决于输入引脚DS的状态。

重复进行8次位移操作,即可完成8位数据的输入。

•存储数据:要将位移操作的结果存储在内部存储器中,需要控制STCP引脚的信号。

当所有位移操作完成后,将STCP引脚设置为高电平,将移位结果存储在寄存器中。

74HC165功能说明

1.并行输入:74HC165具有8个并行输入引脚(A-H),可以同时读取8个输入信号。

这些输入信号可以是数字信号,也可以是模拟信号。

2.串行输出:74HC165具有串行输出引脚(QH),它可以将输入信号转换为串行输出信号。

输出信号的顺序与输入信号的读取顺序相同。

3.移位操作:74HC165可以通过移位操作来读取并且存储输入信号。

移位操作可以由一个时钟信号(SH/LD)和一个时钟使能信号(CLKINH)来控制。

当时钟使能信号为高电平时,移位操作生效;当时钟使能信号为低电平时,移位操作被禁止。

4.并行加载:除了移位操作之外,74HC165还可以通过并行加载操作来读取并存储输入信号。

并行加载操作可以通过时钟使能引脚(CLKINH)和并行加载引脚(PL)来控制。

当时钟使能引脚为高电平时,同时并行加载引脚为高电平,即可进行并行加载操作。

5.级联操作:多个74HC165芯片可以级联在一起,以扩展输入信号的数量。

级联操作可以通过级联引脚(SERA/B)和级联输出引脚(QH)来实现。

级联引脚可以将一个74HC165的输出连接到另一个74HC165的输入,以实现数据的串行传输。

总结起来,74HC165是一种用于将8个并行输入信号转换为串行输出信号的移位寄存器芯片。

它通过移位操作和并行加载操作来读取并存储输入信号,并且可以通过级联操作扩展输入信号的数量。

这种芯片在数字电路控制和数据采集等应用中非常常见,具有广泛的用途。

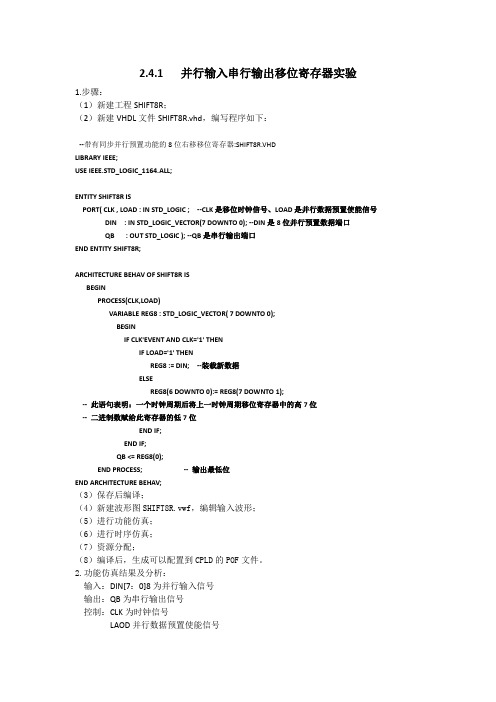

2.4.1 并行输入串行输出移位寄存器实验1.步骤:(1)新建工程SHIFT8R;(2)新建VHDL文件SHIFT8R.vhd,编写程序如下:--带有同步并行预置功能的8位右移移位寄存器:SHIFT8R.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SHIFT8R ISPORT( CLK , LOAD : IN STD_LOGIC ; --CLK是移位时钟信号、LOAD是并行数据预置使能信号DIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --DIN是8位并行预置数据端口QB : OUT STD_LOGIC ); --QB是串行输出端口END ENTITY SHIFT8R;ARCHITECTURE BEHAV OF SHIFT8R ISBEGINPROCESS(CLK,LOAD)VARIABLE REG8 : STD_LOGIC_VECTOR( 7 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENIF LOAD='1' THENREG8 := DIN; --装载新数据ELSEREG8(6 DOWNTO 0):= REG8(7 DOWNTO 1);-- 此语句表明:一个时钟周期后将上一时钟周期移位寄存器中的高7位-- 二进制数赋给此寄存器的低7位END IF;END IF;QB <= REG8(0);END PROCESS; -- 输出最低位END ARCHITECTURE BEHAV;(3)保存后编译;(4)新建波形图SHIFT8R.vwf,编辑输入波形;(5)进行功能仿真;(6)进行时序仿真;(7)资源分配;(8)编译后,生成可以配置到CPLD的POF文件。

2.功能仿真结果及分析:输入:DIN[7:0]8为并行输入信号输出:QB为串行输出信号控制:CLK为时钟信号LAOD并行数据预置使能信号(1)功能仿真:波形分析:LOAD=1,CLK=1,输入并行信号“01001101”LOAD=0,每输入一个脉冲,右移一位并从QB 端输出,依次为“01001101” 因此,该设计可以实现并行输入串行输出的右移移位功能。

寄存器实验报告一、实验目的1. 了解寄存器的分类方法,掌握各种寄存器的工作原理;2. 学习使用Verilog HDL 语言设计两种类型的寄存器。

二、实验设备PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。

三、实验内容寄存器中二进制数的位可以用两种方式移入或移出寄存器。

第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。

第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。

因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。

本实验使用Verilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。

四、实验步骤1.并行输入串行输出移位寄存器实验步骤1). 运行Quartus II 软件,选择File New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。

2.) 选择File New 菜单,创建Verilog HDL 描述语言设计文件,打开文本编辑器界面。

3.) 在文本编辑器界面中编写Verilog HDL 程序,源程序如下:module SHFIT8R(din,r_st,clk,load,dout);input [7:0]din;input clk,r_st,load;output dout;reg dout;reg [7:0]tmp;always @(posedge clk)if(!r_st)begindout<=0;endelsebeginif(load)begintmp=din;endelsebegintmp[6:0]=tmp[7:1];tmp[7]=0;enddout<=tmp[0];endendmodule4). 选择File Save As 菜单,将创建的VHDL 设计文件保存为工程顶层文件名SHIFT8R.V。

任务8.2模式锁存触发电路设计任务说明习题解答一、测试(一)判断题1、移位寄存器74LS194 可串行输入并行输出,但不能串行输入串行输出。

答案:F解题:并行送数功能。

当/CR=1,M1M0=11时,在上升沿作用下,D0~D3端输入的数码d0~d3并行送入寄存器。

当/CR=1、M1M0=01时,在上升沿作用下,DSR端输入的数码依次送入寄存器。

2、寄存器并行方式与串行方式比较,并行存取方式的速度比串行存取方式慢得多,而且所用的数据线要比串行方式多。

答案:F解题:寄存器并行方式与串行方式比较,并行存取方式的速度比串行存取方式快得多,但所用的数据线要比串行方式多。

3、寄存器能够把串行数据变成并行数据。

答案:T解题:寄存器能够把串行数据变成并行数据。

4、双向移位寄存器74LS194当/CR端输入低电平时,所有输出均为零。

答案:T解题:双向移位寄存器74LS194当/CR端输入低电平时,所有输出均为零。

5、数据锁存器74HC573的/OE引脚输入无效信号为高时,输出为高阻。

答案:T解题:数据锁存器74HC573的/OE引脚输入无效信号为高时,输出为高阻6.能存放二值代码的部件叫做寄存器。

寄存器按功能分为数码寄存器和移位寄存器。

数码寄存器只供暂时存放数码,可以根据需要将存放的数码随时取出参加运算或者进行数据处理。

移位寄存器不但可存放数码,而且在移位脉冲作用下,寄存器中的数码可根据需要向左或向右移位。

答案:T解题:能存放二值代码的部件叫做寄存器。

寄存器按功能分为数码寄存器和移位寄存器。

数码寄存器只供暂时存放数码,可以根据需要将存放的数码随时取出参加运算或者进行数据处理。

移位寄存器不但可存放数码,而且在移位脉冲作用下,寄存器中的数码可根据需要向左或向右移位。

7.从寄存器取出数码的方式也有并行输出和串行输出两种。

在并行输出方式中,被取出的数码在对应的输出端同时出现;在串行输出方式中,被取出的数码在一个输出端逐位输出。

基本的通讯方式有并行通讯和串行通讯两种。

并行通讯:一条信息的各位数据被同时传送的通讯方式称为并行通讯。

并行通讯的特点是:各数据位同时传送,传送速度快、效率高,但有多少数据位就需多少根数据线,因此传送成本高,且只适用于近距离(相距数米)的通讯。

串行通讯:一条信息的各位数据被逐位按顺序传送的通讯方式称为串行通讯。

串行通讯的特点是:数据位传送,传按位顺序进行,最少只需一根传输线即可完成,成本低但送速度慢。

串行通讯的距离可以从几米到几千米。

根据信息的传送方向,串行通讯可以进一步分为单工、半双工和全双工三种。

信息只能单向传送为单工;信息能双向传送但不能同时双向传送称为半双工;信息能够同时双向传送则称为全双工。

而按照串行数据的时钟控制方式,串行通信又可分为同步通信和异步通信两种方式。

异步通信:接收器和发送器有各自的时钟;同步通信:发送器和接收器由同一个时钟源控制。

1、异步串行方式的特点所谓异步通信,是指数据传送以字符为单位,字符与字符间的传送是完全异步的,位与位之间的传送基本上是同步的。

异步串行通信的特点可以概括为:①以字符为单位传送信息。

②相邻两字符间的间隔是任意长。

③因为一个字符中的比特位长度有限,所以需要的接收时钟和发送时钟只要相近就可以,不需同步。

④异步方式特点简单的说就是:字符间异步,字符内部各位同步。

2、异步串行方式的数据格式异步串行通信的数据格式如图1所示,每个字符(每帧信息)由4个部分组成:①1位起始位,规定为低电0;②5~8位数据位,即要传送的有效信息;③1位奇偶校验位;④1~2位停止位,规定为高电平1。

3、同步串行方式的特点所谓同步通信,是指数据传送是以数据块(一组字符)为单位,字符与字符之间、字符内部的位与位之间都同步。

同步串行通信的特点可以概括为:①以数据块为单位传送信息。

②在一个数据块(信息帧)内,字符与字符间无间隔。

③因为一次传输的数据块中包含的数据较多,所以接收时钟与发送进钟严格同步,通常要有同步时钟。

74ls165工作原理74LS165是一款逐位移位寄存器,它可以将8位的输入数据进行并行转换,输出到8位的串行数据线上。

下面我们来了解一下74LS165的工作原理。

让我们了解一下74LS165的引脚和功能。

引脚|功能-|-1|GND2A|串行数据输入2B|并行数据输入3|时钟输入4-11|并行数据输出12|输出使能13-16|电源电压1.并行数据输入与串行数据输入的选择在74LS165中,可以通过引脚2A和2B选择并行输入或串行输入。

当2A引脚被使能时,串行数据输入被禁用,只有并行数据输入被使用。

当2B引脚被使能时,串行数据输入被启用。

2.时钟输入时钟输入引脚(引脚3)接收到一个高电平脉冲时,输入的数据就会进行一次并行转换,然后被输出到串行数据线上。

3.并行数据输出在74LS165中,有8个并行数据输出引脚(引脚4-11),这些引脚输出并行转换后的8位数据。

当时钟输入引脚接收到高电平脉冲时,输入的数据被放入寄存器中,并且寄存器的输出被更新。

在74LS165中,也有一个串行数据输出引脚(引脚2A)。

这个引脚在并行输入模式下不起作用,但在串行输入模式下,输出的数据是串行输入的数据。

5.输出使能输出使能引脚(引脚12)用于控制输出数据。

当输出使能被禁用时,无法从并行数据输出引脚和串行数据输出引脚中读取数据。

除了了解74LS165的工作原理外,还有一些注意事项需要我们关注。

首先是和时钟的相关问题。

在使用74LS165时,时钟输入必须关注到其稳定性和精确度。

如果时钟信号不稳定或者精度不够,将会影响到转换数据的准确性和精度。

其次是和输入电平的相关问题。

对于74LS165,它的输入电平应该在规定范围之内,否则会对其正常工作产生影响。

当输入电平过高时,就会超出芯片的工作范围,导致器件失效。

而当输入电平过低时,芯片不能正常工作。

芯片的使用温度也需要注意。

74LS165的使用温度范围为0℃到70℃,如果超出这个范围,就会对芯片产生影响。

74ls164与单片机的串并转换(串转并\串进并出)

74LS164串转并实验本实验是用74LS164把输入的串行数转换成并行数输出,74LS164为串行输入并行输出移位寄存器,其引脚图及功能如下:

A、B:串行输入端;

QA~QH:并行输出端;

CLR:清零端,低电平有效;

CLK:时钟脉冲输入端,上升沿有效。

实验采用单片机串行工作方式0和P1端口两种方式串行输出数据。

串行口工作方式0时,数据为8位,从RXD端输出,TXD端输出移位信号,其波特率固定为Fosc/12。

在CPU 将数据写入SBUF寄存器后,立即启动发送。

待8位数据输完后,硬件将状态寄存器的TI位置1,TI必须由软件清零。

串行口工作方式0数据/时钟是自动移位输出,用P1端口输出数据时,要编程位移数据,每输出一个数据位,再输出一个移位脉冲。

内容及步骤:

本实验需要用到单片机最小系统(F1区)、十六位逻辑电平显示(I4区)和74LS164(G3区)。

1、选用89C51单片机最小应用系统模块,用八位数据线连接74LS164的并行输出JD5G 与十六位逻辑电平显示模块JD2I,将74LS164的串行输入端A/B(1和2脚)接到RXD 上,CLK接到TXD上,CLR接INT0。

2、用串行数据通信线连接计算机与仿真器,把仿真器插到模块的锁紧插座中,请注意仿真器的方向:缺口朝上。

3、打开KeiluVision2仿真软件,首先建立本实验的项目文件,接着添加TH23_74164.ASM 源程序,进行编译,直到编译无误。

4、全速运行程序,观察发光二极管亮灭情况,先右移动两次,再左移动两次,然后闪烁两次。

串并转换原理

串并转换原理是指将串行输入的数据按照一定的规则转换成并

行输出的过程。

串行输入的数据是指数据按照一定的顺序一个一个地输入,而并行输出的数据则是同时输出多个数据。

在计算机领域中,串并转换常常用于数据传输、存储等方面。

串并转换的原理是利用时序电路将串行输入的数据按照一定的

规则进行拆分并行输出。

具体实现方式包括:串行输入数据通过一个移位寄存器进行存储,然后通过时序电路进行分拆,并行输出到多个输出端口。

在这一过程中,数据的位数应满足移位寄存器和输出端口的位数要求。

串并转换的应用非常广泛。

在计算机内部的数据传输中,串并转换可以大大提高数据传输速度和效率。

同时,在高速通信接口中,如网络通信等,串并转换也能够有效地提高通信速率。

此外,串并转换还可以用于数据存储,如将数据从一个存储介质上串行读出,然后转换为并行数据存储到另一个介质上。

总之,串并转换原理是计算机领域中非常重要的一种技术,它在很多应用领域都具有广泛的应用前景。

- 1 -。

并行输入串行输出移位寄存器原理移位寄存器是一种常见的数字电路元件,用于将数据进行移位操作。

它具有并行输入和串行输出的特点,可以将多个输入同时加载到寄存器中,并按照一定的顺序输出。

本文将介绍并行输入串行输出移位寄存器的原理及其工作方式。

一、移位寄存器的基本原理移位寄存器是由一组触发器组成的,每个触发器都具有数据输入D、时钟输入CLK和数据输出Q。

在并行输入串行输出移位寄存器中,触发器的数据输入D与并行输入数据相连,时钟输入CLK相连,数据输出Q与下一个触发器的数据输入D相连,最后一个触发器的数据输出Q为寄存器的串行输出。

当时钟信号到达时,触发器会将输入数据加载到自身,并将输出作为下一个触发器的输入。

通过多个触发器的串联,数据可以在寄存器中进行移位操作。

当所有输入数据加载完成后,通过寄存器的串行输出可以得到移位后的结果。

二、移位寄存器的工作方式1. 并行输入:将要移位的数据同时输入到寄存器的多个触发器中。

每个触发器都会将输入数据保存到自身。

这样可以实现一次性输入多个数据,提高了数据输入的效率。

2. 串行输出:通过触发器的串行输出将移位后的数据输出。

每当时钟信号到达时,触发器将自身的数据输出,并将输出作为下一个触发器的输入。

这样数据就会从一个触发器传递到下一个触发器,最终得到移位后的结果。

3. 移位操作:通过时钟信号的不断触发,移位寄存器中的数据可以进行移位操作。

每当时钟信号到达,数据会从一个触发器传递到下一个触发器,实现数据的移位。

当所有数据都完成移位后,可以通过最后一个触发器的串行输出得到移位后的结果。

三、应用场景并行输入串行输出移位寄存器常用于串行通信中的数据传输。

在串行通信中,数据需要按照一定的顺序进行传输,而移位寄存器可以实现数据的有序移位,保证数据的正确传输。

例如,在串行通信中,发送端需要将要发送的数据按照一定的格式进行编码,并通过串行方式发送出去。

接收端则需要将接收到的数据进行解码并按照相应的格式进行处理。

并行输入串行输出移位寄存器原理以并行输入串行输出移位寄存器原理为标题,下面将详细介绍该原理及其应用。

移位寄存器是一种常用的数字电路元件,可以实现数据的平行输入和串行输出。

它由多个触发器组成,每个触发器都可以存储一个位的信息。

在并行输入时,数据可以同时输入到每个触发器中,而在串行输出时,触发器之间的数据按照一定的顺序传递,从而实现数据的移位。

在移位寄存器中,最常见的是串行输入并行输出的移位寄存器,即数据按照一位一位的顺序输入到移位寄存器中,而输出则可以同时输出多个位的数据。

这种移位寄存器的应用非常广泛,例如在串行通信中,可以使用移位寄存器将并行数据转换为串行数据进行传输,而在显示器中,也可以使用移位寄存器逐行扫描显示像素点。

移位寄存器的工作原理基于触发器的特性。

触发器是一种存储状态的元件,它可以根据时钟信号的变化来改变输出状态。

在移位寄存器中,触发器之间通过时钟信号进行串行数据传输。

当时钟上升沿到来时,触发器将其输入数据更新到输出中,并将原来的输出传递给下一个触发器,从而实现数据的移位。

在移位寄存器中,有两种常见的触发器,分别是D触发器和JK触发器。

D触发器是最简单的触发器,它有一个数据输入端D和一个时钟输入端CLK,当时钟信号发生变化时,D触发器将D端的数据更新到输出端Q中。

而JK触发器是一种更复杂的触发器,它有两个数据输入端J和K,以及一个时钟输入端CLK。

当时钟信号发生变化时,JK触发器根据J和K的值来更新输出端Q。

通过组合不同类型的触发器,可以构建出不同类型的移位寄存器,满足不同的应用需求。

除了串行输入并行输出的移位寄存器外,还有并行输入串行输出的移位寄存器。

这种移位寄存器可以同时输入多个位的数据,并将其串行输出。

在这种移位寄存器中,每个触发器都有一个数据输入端,当时钟信号发生变化时,触发器将输入端的数据更新到输出端,并将原来的输出传递给下一个触发器。

通过这种方式,多个位的数据就可以按照一定的顺序进行移位输出。

74hc595芯片驱动数码管的工作原理

74HC595 是一种串行输入、并行输出的移位寄存器芯片,常被用于驱动数码管、LED 等输出设备。

它的工作原理基于串行-并行转换和移位操作。

以下是使用74HC595 驱动数码管的基本工作原理:

一、串行输入:74HC595 芯片具有三个输入引脚,分别是:

DS(Data Input):串行数据输入

SHCP(Shift Register Clock Input):移位寄存器时钟输入

STCP(Storage Register Clock Input):存储寄存器时钟输入

通过串行数据输入引脚DS,可以将一个字节的数据(8位)串行输入到74HC595 中。

二、移位操作:在输入完一个字节数据后,通过向SHCP 引脚提供时钟信号,数据将从串行输入DS 移位到移位寄存器中。

三、并行输出:74HC595 还有8 个并行输出引脚,分别是Q0 到Q7。

这些输出引脚可以连接到数码管的段或LED 灯的正极。

通过向STCP 引脚提供时钟信号,移位寄存器中的数据会并行输出到存储寄存器中。

四、存储寄存器:存储寄存器中的数据在时钟信号到达STCP 时被锁存,此时数据会被保持在存储寄存器中,不再改变。

通过不断重复以上的移位和存储操作,可以将多个字节的数据依次输出到74HC595 的并行输出引脚,从而实现对多个数码管或LED 灯的控制。

总的来说,74HC595 通过串行输入、移位操作和并行输出的方式,实现了对大量输出设备的控制。

这种级联的方式可以有效地减少需要的引脚数量,适用于有限的GPIO 资源的情况。

74hc595的工作原理

74HC595是一款8位移位寄存器,用于串行输入并行输出数

据的传输。

其工作原理如下:

1. 序列输入:数据首先通过串行输入(SER)引脚依次输入到

74HC595移位寄存器的内部寄存器中。

可以通过将数据位的

电平依次输入SER引脚,或者通过移位寄存器引脚(SRCLK)

提供的时钟信号实现。

每个数据位都会依次被移入内部寄存器。

2. 移位:当所有数据位都被输入后,通过一个移位寄存器引脚(SRCLK)提供的时钟信号,将内部寄存器中的数据进行右移。

此时,新输入的数据位会被移至最低位,而原有数据位则向更高位移动。

3. 输出:移位完成后,将内部寄存器中的数据同时传输到并行输出引脚(Q0-Q7)上。

这些并行输出引脚可以驱动外部设备或

其他电路。

4. 控制:在移位和输出过程中,通过锁存寄存器引脚(RCLK)

提供的锁存信号,可以选择性地决定是否将数据传输到并行输出引脚上。

当锁存信号为高电平时,数据被锁存;当锁存信号为低电平时,数据则可以更新。

总之,74HC595的工作原理就是通过串行输入、移位、并行

输出和锁存控制四个步骤实现从串行到并行的数据传输。

通过输入的数据和时钟信号进行移位操作,最终将数据并行输出到多个引脚上。

单片机常见输入输出模式单片机(Microcontroller,简称MCU)是一种集成电路,集中了处理器、内存、输入输出接口和定时器等功能模块,广泛应用于各种电子设备中。

输入输出(Input/Output,简称I/O)是单片机与外部环境进行信息交互的重要方式。

本文将介绍单片机常见的几种输入输出模式。

1. 并行输入输出模式并行输入输出模式是最常见的单片机与外设进行数据交互的方式。

在并行输入输出模式下,单片机与外设之间通过多个数据线同时传输多位数据。

这种模式的好处是传输速度快,但需要较多的引脚资源,适用于对传输速度要求较高的应用。

2. 串行输入输出模式串行输入输出模式是一种将数据逐位进行传输的方式。

在串行输入输出模式下,单片机与外设之间通过单个数据线逐位传输数据。

这种模式的好处是占用较少的引脚资源,适用于空间有限且对传输速度要求不高的应用。

3. 通用异步收发器模式通用异步收发器(UART)是一种单片机常用的输入输出模式。

UART内部有一个缓冲区,可以接收和发送数据。

在使用UART进行数据传输时,单片机通过配置相关寄存器的参数来设置波特率、数据位数、停止位等通信参数,然后可以通过读写缓冲区来进行数据的收发。

4. 并行输入捕获/输出比较模式并行输入捕获(Input Capture)和输出比较(Output Compare)是单片机中常用的定时器功能模式。

在这种模式下,单片机可以通过定时器模块捕获外部信号的边沿触发事件,并记录下触发事件的时间戳。

同时,单片机还可以通过定时器模块产生输出信号,并与外部信号进行比较。

这种模式适用于需要对时间进行精确控制的应用,如测量脉冲宽度、频率测量等。

5. 脉冲宽度调制模式脉冲宽度调制(Pulse Width Modulation,简称PWM)是一种将数字信号转化为模拟信号的技术。

在PWM模式下,单片机通过定时器模块产生周期固定的脉冲信号,并通过改变脉冲的占空比来模拟出不同的电平信号。

单片机移位寄存器1. 什么是单片机移位寄存器单片机移位寄存器(Shift Register)是一种具有移位功能的寄存器,在数字电子电路中被广泛应用。

它由一组触发器(Flip-Flop)组成,可以将数据按照特定的方式进行移位操作。

2. 移位寄存器的工作原理移位寄存器通常由串行输入、串行输出、并行输入和并行输出四个主要部分组成。

其工作原理如下:•串行输入:数据输入信号逐位地经过寄存器,通过串行输入端口输入。

每当输入一个新的数据位时,原有的数据位将向左移位,腾出位置存放新的数据位。

•串行输出:从移位寄存器的串行输出端口输出数据。

当整个移位寄存器被移位后,最右边的数据位将从串行输出端口输出,同时,原有数据位向右移位填充空出的位置。

•并行输入:通过并行输入端口将整个数据一次性输入到移位寄存器中,不进行移位操作。

•并行输出:通过并行输出端口将整个移位寄存器的内容一次性输出。

3. 移位寄存器的应用场景移位寄存器在数字电子电路中具有广泛的应用,例如:3.1. 数据传输与存储移位寄存器可以用于将数据从一个地方传输到另一个地方,实现数据的序列化和反序列化。

在通信系统中,可以使用移位寄存器将并行数据转换为串行数据进行传输,或者将串行数据转换为并行数据进行处理。

3.2. 并行输入/输出扩展通过移位寄存器,可以将单片机的并行输入/输出引脚扩展为更多的输入/输出引脚。

通过将多个移位寄存器级联,可以实现更多的输入/输出引脚扩展。

3.3. 状态存储移位寄存器可以用于存储状态信息,例如程序计数器(Program Counter)和状态寄存器(Status Register)等。

4. 移位寄存器的类型根据移位寄存器的工作方式和结构特点,常见的移位寄存器包括以下几种类型:4.1. 并行入/串行出移位寄存器(PISO)并行入/串行出移位寄存器有多个并行输入引脚和一个串行输出引脚。

多个并行输入信号可以一次性并行输入到寄存器中,然后按位进行移位,输出到串行输出引脚上。

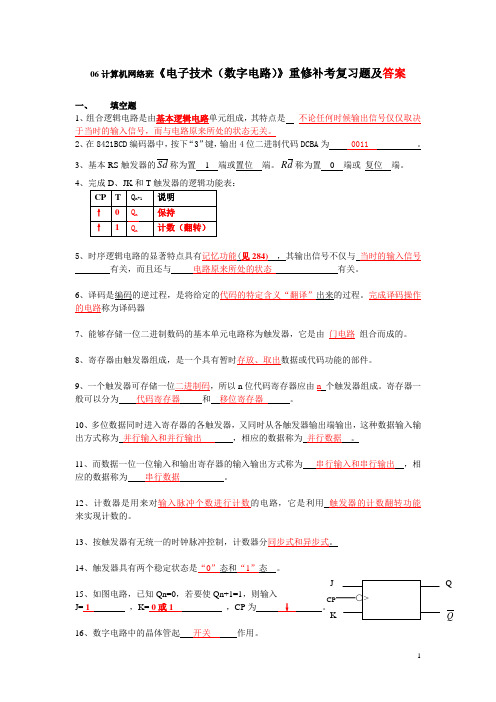

QQ 06计算机网络班《电子技术(数字电路)》重修补考复习题及答案一、 填空题 1、组合逻辑电路是由基本逻辑电路单元组成,其特点是 不论任何时候输出信号仅仅取决于当时的输入信号,而与电路原来所处的状态无关。

2、在8421BCD 编码器中,按下“3”键,输出4位二进制代码DCBA 为 0011 。

3、基本RS 触发器的Sd 称为置 1 端或置位 端。

d R 称为置 0 端或 复位 端。

45、时序逻辑电路的显著特点具有记忆功能(见284) ,其输出信号不仅与 当时的输入信号 有关,而且还与 电路原来所处的状态 有关。

6、译码是编码的逆过程,是将给定的代码的特定含义“翻译”出来的过程。

完成译码操作的电路称为译码器7、能够存储一位二进制数码的基本单元电路称为触发器,它是由 门电路 组合而成的。

8、寄存器由触发器组成,是一个具有暂时存放、取出数据或代码功能的部件。

9、一个触发器可存储一位二进制码,所以n 位代码寄存器应由n 个触发器组成。

寄存器一般可以分为 代码寄存器 和 移位寄存器 。

10、多位数据同时进入寄存器的各触发器,又同时从各触发器输出端输出,这种数据输入输出方式称为 并行输入和并行输出 ,相应的数据称为 并行数据 。

11、而数据一位一位输入和输出寄存器的输入输出方式称为 串行输入和串行输出 ,相应的数据称为 串行数据 。

12、计数器是用来对输入脉冲个数进行计数的电路,它是利用 触发器的计数翻转功能 来实现计数的。

13、按触发器有无统一的时钟脉冲控制,计数器分同步式和异步式。

14、触发器具有两个稳定状态是“0”态和“1”态 。

15、如图电路,已知Qn=0,若要使Qn+1=1,则输入 J= 1 ,K= 0或1 ,CP 为 ↓ 。

16、数字电路中的晶体管起 开关 作用。

二、 选择题1、在下列电路中,属于组合逻辑电路的是( A ) A 、编码器 B 、计数器 C 、寄存器2、对17个输入信号编码,应选用( C )位二进制编码器 A 、3 B 、4 C 、53、在分段式显示原理中,七段线段的排列为( A )4、在二进制编码器中若输出端有3个,则输入端的数目最多为( C ) A )10 ; B )6 ; C)85、能从多个输入数据中选择一路输出的逻辑电路,是(A )。

74ls194功能

74LS194是一种具有四个主要功能的16位边缘触发通用串行-

并行移位寄存器。

以下是74LS194的主要功能:

1. 并行输入:74LS194有16个并行输入引脚,称为A0-A15,

可以同时将16位数据并行输入到寄存器中。

2. 串行输入:74LS194有一个串行输入引脚,称为D。

通过串

行输入,可以逐位输入的方式将数据输入到寄存器中。

3. 串行输出:74LS194有一个串行输出引脚,称为Q。

通过串

行输出引脚,可以逐位输出寄存器中的数据。

4. 并行输出:74LS194有16个并行输出引脚,称为Q0-Q15。

可以同时从寄存器中将16位数据并行输出。

5. 移位功能:74LS194具有向左和向右移位的能力。

通过控制

引脚,可以选择移位方向。

6. 边缘触发:74LS194是边缘触发器件,这意味着它只在时钟

信号的边沿触发数据输入和输出。

可以通过时钟引脚控制寄存器的操作。

7. 计数功能:74LS194可以用作计数器。

通过适当连接控制引脚,可以将多个74LS194级联,以实现更大范围的计数器。

8. 加载功能:74LS194可以将并行输入的数据加载到寄存器中,

而不进行移位操作。

总而言之,74LS194是一个功能强大的通用寄存器,可以实现并行输入、并行输出、串行输入、串行输出、移位和计数等多种功能。

它适用于广泛的应用,如数据存储和计数器设计。

16-bit Serial-In/Parallel-Out Constant-Current LED Driver Product DescriptionThe SCT5020 serial-interfaced LED driver sinks 16 LED clusters with constant current to keep the uniform intensity of LED displays. In applications, an external resistor is used to set the full-scale constant output current from 5mA up to 45mA. The SCT5020 guarantees each output can endure maximum 17V DC voltage stress. The built-in shift registers and data latches making the SCT5020 effective solution in driving LED display. The output enable function gates all 16 outputs on and off, and is fast enough to be used as PWM input for LED intensity control. Since the serial data input rate can be reached up to 25MHz, the SCT5020 will satisfy system which needs high volume data transmission to control the LED display.Furthermore, the SCT5020 provides excellent temperature regulation thus it can be applied to varied of operating temperature.Features◆Finest grayscale response with 40ns PWM pulse width◆16 robust constant current sinker with LED power-supply voltage up to 17V◆Constant output current : 5 –30/********/5V◆Wide power supply voltages: 3.3V to 5V◆Excellent regulation to load, supply voltage and temperatureLoad regulation: ±0.1%/VLine regulation: ±0.5%/V◆High current matching accuracy: ±1% between outputs, ±2% between ICs◆Dropout voltage 0.5V@20mA, V DD=5V◆CMOS Schmitt trigger inputs with clock rate up to 25MHz @ cascade connection◆The constant current value of 16 outputs is set by a single external resistor◆Built-in power on reset(POR) circuit forces all the outputs off while power on◆Package: SSOP24, SSOP24-1, SOP24 and TQFN24◆Applications: LED Displays, Variable Message Signs, Illumination, LED Traffic SignsPin ConfigurationsTerminal DescriptionVDD REXT SDO OE/ OUT15 OUT14 OUT13 OUT12 OUT11 OUT10 OUT9 OUT8OUT14 OUT13 OUT12 OUT11 OUT5OUT6 OUT7 OUT8 OUT9 OUT15 OE/ OUT10 OUT13 OUT12 OUT11 OUT10OUT5OUT6 OUT7 GND OUT8 OUT14 OUT15 OUT9Block DiagramEquivalent Circuits of Inputs (1) Equivalent Circuits of Inputs (2)Equivalent Circuits of Inputs (3) Equivalent Circuits of OutputSDOSCT 5020GND GND GNDGND GND GNDGND GND GNDOrdering InformationStarChips Technology, Inc.5F, No.5, Technology Rd., Science-Based Industrial Park, Hsin-Chu, Taiwan, R.O.C. Tel : +886-3-577-5767 Ext.555, Fax: +886-3-577-6575,E-mail : *********************.twTruth TableTiming DiagramCLKSDI LA/ OE/ OUT0 OUT1 OUT15 SDOOFF ON OFF ON ON OFF (LSB) (MSB) OUT2 OUT3- OUT12 OUT13 OUT14 ON OFF ONOFF ON OFF OFF ONMaximum Ratings (T A = 25°C)may cause the device breakdown, deterioration even permanent damage. Exposure to the maximum rating conditions for extended periods may affect device reliability.Recommended Operating Conditions(T A= -40 to 85°C unless otherwise noted)1. The output current keep constant in range of 5-45mA if V OUT=1V.However, user can minimize V OUT to reduce power dissipation according to used current, e.g., set V OUT to 0.6V if I OUT=20mA.2. The maximum Vout is package thermal limited, user should keep Vout under maximum power dissipation.Electrical Characteristics (V DD =3.3/5V, T A =25°C unless otherwise noted)1. Bit skew=(I OUT -I AVG ) / I AVG , where I AVG =(I OUT(max)+ I OUT(min))/22. Chip skew=(I AVG -I CEN ) / I CEN *100(%), where I CEN is the statistics distribution center of output currents.3. Line regulation=[I OUT (V DD =5.5V)-I OUT (V DD =3V)] / {[I OUT (V DD =5.5V)+I OUT (V DD =3V)]/2} / (5.5V-3V)*100(%/V)4.Load regulation=[I OUT (V OUT =4V)-I OUT (V OUT =1V)] / {[I OUT (V OUT =4V)+I OUT (V OUT =1V)]/2} / (4V-1V)*100(%/V)Test Circuit for Electrical CharacteristicsC LED =10uF C 1Switching Characteristics (T A =25°C unless otherwise noted)Test Circuit for Switching CharacteristicsV ILV IH t R = t F LED *Timing WaveformLA/ Control OutputOE/ Control OutputOE/CLKSDISDOLA/OE/OUTnAdjusting Output CurrentThe SCT5020’s output current (I OUT ) are set by one external resistor at pin REXT. The output current I OUT versus resistance of R EXT is shown as the following figure.SCT 5020 I O UT vs. R E XT @5V,T A =25°C01020304050607000.511.52 2.53 3.54R EXT (K Ω)I O U T (m A )1V<V OUT <4VAccording to I-V curve of the output of SCT5020, the output voltage should be larger than 1V to get 45 mA constant current. By applying proper output voltage, the output current set by an external resistor is approximate to: I OUT = 30(615 / REXT) (mA) (chip skew < ±3%). Thus the output current is set to be about 20.5mA at REXT = 900Ω.Output CharacteristicsThe current characteristic of output curve is flat. The output current can be kept constant regardless of the variations of LED forward voltage when V OUT > V DO (Drop-Out voltage). The relationship between I OUT and V OUT is shown below. The output voltage should be kept as low as possible to prevent the SCT5020 from being overheated.SCT 5020 Ivs. V @5V,T =25°C01020304050607001234V OUT (V)I O U T (m A )SCT 5020 I O UT vs. V O UT @3.3V,T A =25°C0510********35404501234V OUT (V)I O U T (m A )Power DissipationThe maximum power dissipation (P D(max)) of a semiconductor chip varies with different packages and ambient temperature. It ’s determined as P D(max)=(T J(max) –T A )/R TH(j-a) where T J(max): maximum chip junction temperature is usually considered as 150°C, T A : ambient temperature, R TH(j-a): thermal resistance. Since P=IV, for sinking larger I OUT , users had better add proper voltage reducers on outputs to reduce the heat generated from the SCT5020.SCT 5050 P vs. T 0.511.52P D (m a x )(W )Limitation on Maximum Output CurrentThe maximum output current vs. duty cycle is estimated by:I OUT(max)=(((T J(max)-T A )/R TH(j-a))-(V DD *I DD ))/V OUT /Duty/N where T J(max)=150°C, N=16(all ON)O 1015202530354045500102030405060708090100Duty(%)I O U T (m a x )(m A )O 1015202530354045500102030405060708090100Duty(%)I O U T (m a x )(m A )O 1015202530354045500102030405060708090100Duty(%)I O U T (m a x )(m A )O 1015202530354045500102030405060708090100Duty(%)I O U T (m a x )(m A )Load Supply Voltage (V LED )The SCT5020 can be operated very well when V OUT ranges from 1V to 4V. However, it is recommended to use the lowest possible supply voltage or set a voltage reducer to reduce the V OUT voltage, at the same time reduce the power dissipation of the SCT5020. Suggested V OUT is to be set greater than V DO and less than 1V. The V DO is dependent on the I OUT current as indicated in section “Output Characteristics ”. Follow the diagram instructions shown below to lower down the output voltage. This can be done by adding additional resistor or zener diode, thus V OUT =V LED -V DROP -V F .Typical Application Circuits.VLEDPCB Design ConsiderationsUse the following general guide-line when designing printed circuit boards (PCB ):Decoupling CapacitorPlace a decoupling capacitor e.g. 1uF between VDD and GND pins of SCT5020. Locate the capacitor as close to the SCT5020 as possible. This is normally adequate for static LED driving. For dynamic scan or PWM applications, it is suggested to add an additional capacitor of 4.7uF or more to each supply for every SCT5020. The necessary capacitance depends on the LED load current, PWM switching frequency, and serial-in data speed. Inadequate VDD decoupling can cause timing problems, and very noisy LED supplies can affect LED current regulation.External Resistor (R EXT )Locate the external resistor as close to the REXT pin as possible to avoid the noise influence.Power and GroundMaximizing the width and minimizing the length of VDD and GND trace improves efficiency and ground bouncing by effect of reducing both power and ground parasitic resistance and inductance. A small value of resistor, e.g., 10Ω (higher if I OUT is larger) series in power input of the SCT5020 in conjunction with decoupling capacitor shunting the IC is recommended. Separating and feeding the LED power from another stable supply terminal V LED , furthermore adding a capacitor C LED greater than 10uF beside the LED are recommended. Please adapt C LED according to total system current consumption.EMI ReductionTo reduce the EMI radiation from system, an economical solution of RC low pass filter (LPF) is suggested to be used to lower the transient edge of clock input signal, as shown in the figure above. Using at least four layers PCB board with two interior power and ground planes is a good scheme to decrease the signal current path which is the source of radiation emission. As a result, EMI radiation can be decreased.LEDClockThermal Pad ConsiderationThe “thermal pad” (also named as “exposed pad”) TQFN package beneath used to increase the heat dissipation capability is grounded. User should be aware of this electrical connection when designing the PCB board, and make provisions for its use. In most of application, the thermal pad is electrically connected to ground plane or conduction. This makes the IC operated with more stable condition.In general, the heat generated from an IC is conducted to the PCB then radiates to the ambient. Thermal pad specifically increases the maximum power dissipation capability of the IC packages. To provide lower thermal resistance from the IC to the ambient air, PCB designers should layout larger thermal conduction areas on top layer (component side) and bottom layer (solder side) as well as thermal vias, the more the better. In addition, connecting thermal via to the ground plane also increases thermal conduction areas, this improves the heat transfer efficiency at the same time greatly dissipates heat generated from the package. Furthermore, coating solder on bottom layer and selecting, e.g., 2 oz. copper which will increase the total thickness of thermal conduction is an alternative.When making the solder paste screen, an opening should be created for the thermal pad. This way the thermal pad can be electrically and thermally connected to the PCB. As the thermal pad is soldered on copper polygon, the chance of inadvertently shorting the thermal pad to traces routed underneath it could be eliminated.Package DimensionSSOP24(check up-to-date version)SSOP24-1 (check up-to-date version)SOP24 (check up-to-date version)Revision History(check up-to-date version)Information provided by StarChips Technology is believed to be accurate and reliable. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Starchips can not assume responsibility and any problem raising out of the use of the circuits. Starchips reserves the right to change product specification without prior notice.StarChips Technology 5F, No.5, Technology Rd.,Science-Based Industrial Park, Hsin-Chu,Taiwan, R.O.C. Tel: +886-3-577-5767 # 555。

74HC595中文资料1. 引言74HC595是一款非常常用的串行输入并行输出(Serial-in Parallel-out)移位寄存器。

它具有广泛的应用场景,在数字电路设计、控制器和驱动器等领域发挥着重要作用。

本文将介绍74HC595的基本信息、功能特点、电气参数以及使用方法。

2. 产品概述74HC595是一款8位移位寄存器,它采用了串行输入、并行输出的方式。

它具有以下主要特点:•输入端采用串行方式,输出端采用并行方式。

•支持数据级联,可以通过多个74HC595进行级联扩展输出。

•内部集成串行至并行转换电路,具有较高的工作频率。

•采用CMOS技术,具有低功耗特点。

•提供了灵活的控制引脚,可根据需要进行编程。

3. 功能特点3.1 输入输出74HC595的输入端包括以下信号线:•SER(串行数据输入):用于输入要移位的数据。

•SRCLK(移位寄存器时钟):用于触发数据移位操作。

•RCLK(存储寄存器时钟):用于将移位寄存器的数据更新到并行输出。

•OE(输出使能):控制并行输出的使能与禁止。

输出端包括以下信号线:•Qa-Qh(并行输出):共8个输出引脚,用于输出存储在移位寄存器中的数据。

3.2 数据级联74HC595支持数据级联,可以通过多个74HC595进行级联扩展输出。

在级联模式下,从第一个74HC595的SER引脚输入的数据,经过多级移位后,最终在最后一个74HC595的并行输出引脚上显示。

3.3 时序控制通过控制时钟信号的触发,可以实现74HC595的不同工作状态。

具体的时序控制包括以下几个方面:•数据移位时钟:通过SRCLK信号触发,将SER输入的数据逐位移入移位寄存器。

•数据存储时钟:通过RCLK信号触发,将移位寄存器中的数据存入存储器,并行输出。

•输出使能控制:通过OE信号控制,并行输出的使能与禁止。

4. 电气参数以下是74HC595的一些重要电气参数:•工作电源:2V至6V•工作电流:20mA(典型值)•运行频率:最高68MHz•静态电流:1μA(典型值)•输出电流:±35mA(典型值)•输入电压:-0.5V至VCC+0.5V需要注意的是,以上参数仅为一般情况下的典型值,具体的应用环境和使用条件可能会有所不同。

串行出入并行输出寄存器实验1.步骤:

(1)新建工程SHIFT8

(2)新建VHDL文件,编写程序如下:

--串行输入并行输出寄存器:

LIBRARY IEEE;

USE Shift8 IS

PORT( DI ,CLK : IN STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY Shift8;

ARCHITECTURE BEHA OF SHIFT8 IS

SIGNAL TMP : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK='1') THEN

TMP(7)<=DI;

FOR I IN 1 TO 7 LOOP

TMP(7-I)<=TMP(8-I);

END LOOP;

END IF;

END PROCESS;

DOUT<=TMP;

END ARCHITECTURE BEHA;

(3)保存后编译;

(4)新建波形图,编辑输入波形;

(5)进行功能仿真;

(6)进行时序仿真;

(7)资源分配;

(8)编译后,生成可以配置到CPLD的POF文件。

2.功能仿真结果及分析:

输入:DI为串行输入信号

输出:DOUT[7:0]为并行输出信号

控制:CLK为时钟信号

(1)功能仿真

波形分析:DI串行输入“01010101”

DOUT[0:7]并行输出“01010101”

因此,该设计能够实现串行输出并行输出的功能。

(2)时序仿真

从波形图看出来,并行输出中两条相邻输出时间延迟为.

3.资源分配。