EDA技术与VHDL_汇总

- 格式:ppt

- 大小:418.50 KB

- 文档页数:40

eda技术与vhdl设计答案eda技术与vhdl设计答案【篇一:eda技术与vhdl复习练习题】/p> 一、填空题1、pld的中文含义是:________。

2、asic的中文含义是:________。

3、“与-或”结构的可编程逻辑器件主要由四部分构成:________、________、____________和____________。

4、可编程逻辑器件结构图中一般用“x”表示此编程单元为________。

6、可编程逻辑器件结构图中无任何标记表示此编程单元为________。

7、可编程逻辑器件按规模的大小一般分为________和_________。

8、低密度可编程逻辑器件的主要有________和_________。

9、gal器件________取代全部pal器件。

10、pal器件只能________次编程。

11、gal器件能________次编程。

12、gal器件________取代ttl器件。

13、gal器件采用________擦除。

14、pal和gal器件________在系统编程。

15、pal和gal器件需要使用________编程。

二、选择题1、可编程逻辑器件pld的基本结构形式是_______:a:与——与b:与——或c:或——与d:或——或2、可以多次编程的器件是_______:a:prom b:plac:pal d:gal3、pld器件未编程时_______:a:有逻辑功能 b:没有逻辑功能c:pal器件有逻辑功能d:gal 器件有逻辑功能 4、gal器件可以用擦除:a:普通光 b:紫外线c:红外线 d:电5、gal16v8器件的输出引脚最多有______:a:16b:4 c:8 d:206、pal16v8器件的输入引脚最多有_______:a:16 b:4 c:8 d:207、gal16v8不能取代_________:a:pal16v b:74ls138c:74ls373 d:isplsi1032e-70plcc848、gal16v8的_______不可编程:a:与阵列b:或阵列c:输出逻辑宏单元olmc d:a、b都三、判断题1、gal器件的输出逻辑宏单元olmc不能实现pal器件的所有输出形式。

EDA技术与VHDL复习练习题探<习题一>一、填空题1、PLD的中文含义是: _______ 。

2、ASIC的中文含义是: _______ 。

3、“与-或”结构的可编程逻辑器件主要由四部分构成:________ 、 ________ 、 ___________ 和____________ 。

4、可编程逻辑器件结构图中一般用“ x ”表示此编程单元为________ 。

5、可编程逻辑器件结构图中一般用“ •”表示此编程单元为________ 06可编程逻辑器件结构图中无任何标记表示此编程单元为____________ 07、可编程逻辑器件按规模的大小一般分为________ 和 _________ o8、低密度可编程逻辑器件的主要有_______ 和9、GAL器件 _______ 代全部PAL器件。

10、PAL器件只能 _______ 编程。

11、GAL器件能 _______ 编程。

12、GAL器件 _______ 代TTL器件。

13、GAL器件采用 _____ 擦除。

14、PAL和GAL器件_______ 系统编程。

15、PAL和GAL器件需要使用_______ 程二、选择题1、可编程逻辑器件PLD的基本结构形式是A :与——与B:与——或C :或---- 与D:或---- 或2、可以多次编程的器件是______ :A : PROMB : PLAC : PALD : GAL3、PLD器件未编程时 ______ :A :有逻辑功能B :没有逻辑功能C : PAL器件有逻辑功能D : GAL器件有逻辑功能4、GAL器件可以用 ____ 擦除:A :普通光B :紫外线C :红外线D :电5、GAL16V8器件的输出引脚最多有______ :A : 16B : 4C : 8D : 206 PAL16V8器件的输入引脚最多有_________A : 16B : 4C : 8D : 207、GAL16V环能取代___________ :A : PAL16V B: 74LS138C : 74LS373D : ispLSI1032E-70PLCC848、GAL16V8勺________ 可编程:A :与阵列B :或阵列C :输出逻辑宏单元OLMCD : A、B都三、判断题1、GAL器件的输出逻辑宏单元OLM不能实现PAL 器件的所有输出形式。

EDA知识点汇总

一、VHDL基本概念

1、VHDL概念

VHDL(VHSIC(Very High Speed Integrated Circuit)Hardware Description Language)是用于描述硬件结构的高级语言,也是一种数字

系统设计语言,可以描述系统的逻辑结构,数据流,与特定硬件的映射实现,包括模块化,可重用,可综合和可测试特性,是精密,功能强大,拥

有仿真功能的高级硬件描述语言。

2、VHDL的作用

VHDL是一门语言,用它描述数字系统,使用它可以实现在抽象结构

与物理实现间的转换,也就是说VHDL把模型描述作为数字逻辑设计的一

部分,它把数字电路设计与电路的描述分离,实现了电路的抽象化,VHDL

作为一个设计语言,它既可以描述电路,也可以用于设计新的电路

3、VHDL的基本结构

VHDL由三部分组成,包括类型定义部分,声明部分,以及功能实现

部分;

(1)类型定义部分

类型定义部分提供了VHDL语言中的语法,包括数据类型、常量声明、变量声明、信号声明、类型定义等。

(2)声明部分

声明部分提供了用于定义数据类型和信号的描述,包括定义数据类型、变量声明、信号声明等。

(3)功能实现部分

功能实现部分描述了如何将信号和变量连接起来形成所需的逻辑功能。

EDA技术与VHDL_汇总EDA(电子设计自动化)技术与VHDL(可编程硬件描述语言)是在电子设计领域中广泛应用的两种技术。

EDA技术是指利用计算机辅助设计软件来帮助工程师进行电子电路的设计和验证,提高设计效率和降低成本。

而VHDL是一种硬件描述语言,用于描述电子系统的行为和结构,是EDA技术的重要工具之一、本文将针对EDA技术和VHDL进行综述。

EDA技术是电子设计流程中的重要环节,包括电路设计、电路模拟、布局与布线、物理验证等多个方面。

其中,电路设计主要关注电路行为和结构的设计,通过EDA软件可以对电路进行逻辑综合、时序优化等操作,从而生成最终的电路结构。

电路模拟是对设计电路进行仿真和验证的过程,通过EDA软件可以模拟电路的工作状态,检查设计是否符合预期要求。

布局与布线是将逻辑电路转化为物理电路的过程,在电路板上布置元件并进行连线,以满足电路的功能和性能要求。

物理验证则是根据设计规则和约束对布局和布线结果进行验证,确保电路能够正常工作。

VHDL是一种硬件描述语言,用于描述电子系统的行为和结构。

VHDL提供了抽象层次,可以描述从逻辑门到整个系统的各个层次。

使用VHDL,设计者可以对系统进行模块化描述,将整个系统分解为多个模块并进行独立设计。

VHDL还提供了丰富的工具和语法,用于描述电路的结构、时序、数据流等信息。

通过VHDL描述的电路可以通过EDA软件进行综合、仿真、布局与布线等操作。

VHDL还具有良好的可移植性,设计者可以在不同EDA软件和不同平台上进行开发和验证。

EDA技术与VHDL的结合可以提高电子设计的效率和质量。

通过EDA软件,设计者可以利用图形界面进行电路设计,快速搭建和验证电路结构。

在设计过程中,VHDL可以使设计者在高层次上描述电路功能和结构,提高设计抽象和可重用性。

此外,通过EDA软件可以进行电路的仿真和验证,帮助设计者对电路进行性能、时序等方面的优化,减少设计错误的风险。

在布局与布线阶段,EDA软件可以自动完成复杂的布局与布线操作,优化电路的尺寸和信号传输路径,提高电路的可靠性和性能。

EDA技术与VHDL_汇总EDA(Electronic Design Automation,电子设计自动化)技术是一类软件和工具的总称,用于帮助设计师在集成电路设计过程中进行系统分析、系统设计、电路设计、物理布局、验证等工作。

EDA技术在现代集成电路设计中起着至关重要的作用。

VHDL(VHSIC Hardware Description Language,可编程硬件描述语言)是一种用于描述数字电路和系统的硬件描述语言。

VHDL通过以人类可读的方式描述电路结构和行为,然后使用EDA工具将VHDL代码转换为实际的电路图和布局。

首先,EDA技术提供了各种工具和环境,可以帮助设计者对电路进行分析和模拟,以验证电路的性能和功能。

设计者可以使用EDA工具对电路进行仿真,以便在实际制造之前发现并消除潜在问题。

在这个过程中,VHDL作为一个硬件描述语言,提供了一种方式来描述和验证电路的行为和功能。

其次,EDA技术还可以帮助设计者将VHDL代码转换为物理布局。

设计者可以使用EDA工具进行逻辑合成、布局布线等操作,根据VHDL代码生成实际的电路图。

这些工具可以通过综合技术将高级抽象描述转换为底层的物理结构,从而提高电路设计的效率和准确性。

此外,EDA技术还可以辅助设计者进行电路的优化。

设计者可以使用EDA工具对电路进行优化,并进行不同级别的折中。

例如,可以通过选择不同的元件、更改电路结构或参数来改善电路性能。

这些优化过程需要设计者对VHDL代码进行分析和修改,以达到更好的性能和功耗表现。

最后,EDA技术还可以帮助设计者进行电路的验证。

使用EDA工具可以对已实现的电路进行验证,确保其符合设计要求。

这些工具可以通过测试用例和仿真来验证电路的正确性,并提供分析报告和调试工具,以便设计者快速定位和修复问题。

VHDL作为硬件描述语言,可以提供详细的功能和行为描述,有助于验证过程的进行。

总而言之,EDA技术与VHDL密切相关,通过提供各种工具和环境,帮助设计者完成集成电路设计的各个阶段。

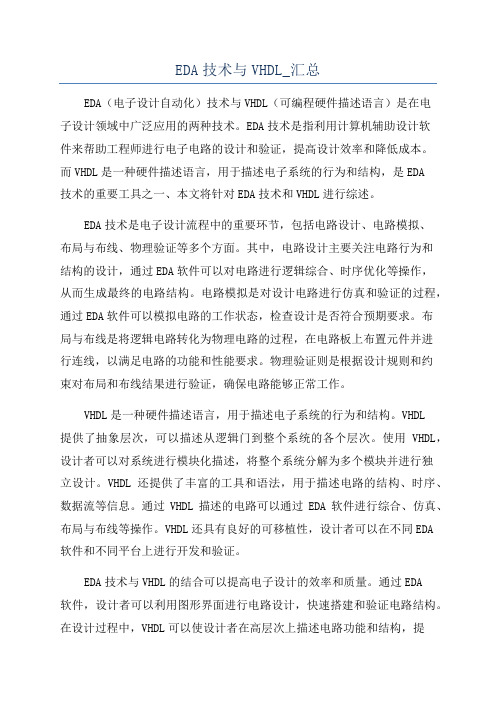

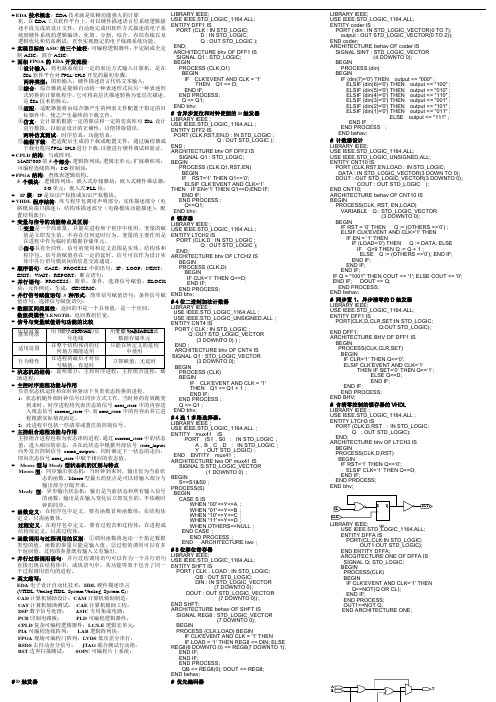

1.下降沿与上升沿的描述。

a)上升沿:clock’event and clock=’1’ rising_edge()b)下降沿:clock’event and clock=’0’ falling_edge()2.信号与变量的区别3.实体中有哪些端口,及其含义。

in: 输入型,此端口为只读型。

out: 输出型,只能在实体内部对其赋值。

inout:输入输出型,既可读也可赋值。

buffer: 缓冲型,与 out 相似,但可读。

4.编程,配置。

通常,将对CPLD的下载称为编程,对FPGA中的SRAM进行直接下载的方式称为配置,但对于OTP FPGA的下载和对FPGA的专用配置ROM的下载仍称为编程5.3-8译码器真值表,写程序LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL; Array ENTITY coder ISPORT(A : IN STD_LOGIC_VECTOR(1 TO 3)Y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END coder ;ARCHITECTURE a1 or coder ISBeginIF A=“000” THEN Y<=“00000001”;ELSIF A=“001” THEN Y<=“00000010”;ELSIF A=“010” THEN Y<=“00000100”;ELSIF A=“011” THEN Y<=“00001000”;ELSIF A=“100” THEN Y<=“00010000”;ELSIF A=“101” THEN Y<=“00100000”;ELSIF A=“110” THEN Y<=“01000000”;ELSE Y<=“10000000”;END IF;END a1;6.CPLD,FPGA的中文含义CPLD:(Complex Programmable Logic Device)复杂可编程逻辑器件FPGA:(Field Programmable Gate Array)现场可编程门阵列ASIC:(Application Specific Integrated Circuit)专用集成电路7.常用的库、包library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_Arith.all;use ieee.std_logic_Unsigned.all;8.一个完整的程序由哪几部分构成。

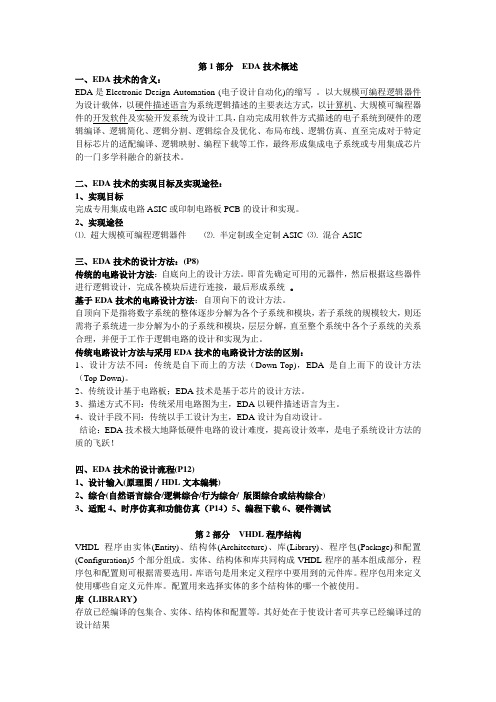

第1部分EDA技术概述一、EDA技术的含义:EDA是Electronic Design Automation (电子设计自动化)的缩写。

以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程器件的开发软件及实验开发系统为设计工具,自动完成用软件方式描述的电子系统到硬件的逻辑编译、逻辑简化、逻辑分割、逻辑综合及优化、布局布线、逻辑仿真、直至完成对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门多学科融合的新技术。

二、EDA技术的实现目标及实现途径:1、实现目标完成专用集成电路ASIC或印制电路板PCB的设计和实现。

2、实现途径⑴. 超大规模可编程逻辑器件⑵. 半定制或全定制ASIC ⑶. 混合ASIC三、EDA技术的设计方法:(P8)传统的电路设计方法:自底向上的设计方法。

即首先确定可用的元器件,然后根据这些器件进行逻辑设计,完成各模块后进行连接,最后形成系统。

基于EDA技术的电路设计方法:自顶向下的设计方法。

自顶向下是指将数字系统的整体逐步分解为各个子系统和模块,若子系统的规模较大,则还需将子系统进一步分解为小的子系统和模块,层层分解,直至整个系统中各个子系统的关系合理,并便于工作于逻辑电路的设计和实现为止。

传统电路设计方法与采用EDA技术的电路设计方法的区别:1、设计方法不同:传统是自下而上的方法(Down-Top),EDA是自上而下的设计方法(Top-Down)。

2、传统设计基于电路板;EDA技术是基于芯片的设计方法。

3、描述方式不同:传统采用电路图为主,EDA以硬件描述语言为主。

4、设计手段不同:传统以手工设计为主,EDA设计为自动设计。

结论:EDA技术极大地降低硬件电路的设计难度,提高设计效率,是电子系统设计方法的质的飞跃!四、EDA技术的设计流程(P12)1、设计输入(原理图/HDL文本编辑)2、综合(自然语言综合/逻辑综合/行为综合/ 版图综合或结构综合)3、适配4、时序仿真和功能仿真(P14)5、编程下载6、硬件测试第2部分VHDL程序结构VHDL程序由实体(Entity)、结构体(Architecture)、库(Library)、程序包(Package)和配置(Configuration)5个部分组成。

1.EDA即Electronic Design Automation(电子设计自动化),就是以计算机为工作平台,以EDA 软件工具为开发环境,以硬件描述语言(HDL)为设计语言,以可编程逻辑器件为实验载体,以ASIC(Application Specific Integrated Circuit)、SOC(System On a Chip)芯片为目标器件,以电子系统设计为应用方向的电子产品自动化设计过程。

2.EDA最后实现的目标:全定制或半定制ASIC设计,FPGA/CPLD开发应用。

3.作为EDA技术最终实现目标的ASIC,通过三种途径来完成:(1)超大规模可编程逻辑器件:实现这一途径的主流器件是FPGA/CPLD。

直接面向用户,具有极大的灵活性和通用性,使用方便,开发效率高,成本低,技术维护简单,工作可靠性好。

(2)半定制或全定制ASIC:根据实现工艺,可统称为掩膜ASIC,可编程的ASIC具有灵活多样的编程功能。

掩膜ASIC分为:门阵列、标准单元、全定制三类。

(3)混合ASIC:具有面向用户的编程功能和逻辑资源,同时也含有可方便调用和配置的硬件标准单元模块。

4.EDA设计分五级进行分层次设计:(1)系统级即行为级;(2)RTL级;(3)门级:即逻辑设计,以电路或触发器作基本部件,表达各种逻辑关系;(4)电路级:可看作分离的元件为基本元件,具体表达电路在时域的伏安特性或频域的响应等性能;(5)器件级:即板图级。

5.面向FPGA的开发流程:设计输入(图形输入、文本输入)、综合、布线布局(适配)、仿真(时序仿真、功能仿真)、下载和硬件测试。

6.综合的概念:电子设计中,将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程称为综合。

事实上,设计过程中的每一步都可称为一个综合环节。

7.综合的分类:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

# EDA 技术概念:EDA 技术就是依赖功能强大的计算机,在EDA 工具软件平台上,对以硬件描述语言位系统逻辑描述手段完成的设计文件,自动地完成用软件方式描述的电子系统到硬件系统的逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

# 实现目标的ASIC 的三个途径:可编程逻辑器件;半定制或全定制ASIC ;混合ASIC ;# 面相FPGA 的EDA 开发流程:①设计输入:将电路系统以一定的表达方式输入计算机,是在EDA 软件平台对FPGA/CPLD 开发的最初步骤。

两种类型:图形输入;硬件描述语言代码文本输入;②综合:综合器就是能够自动将一种表述形式向另一种表述形式转换的计算机程序,它可将高层次描述转换为低层次描述,是EDA 技术的核心。

③适配:适配器能将由综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件。

④仿真:让计算机根据一定的算法和一定的仿真库对EDA 设计进行模拟,以验证设计的正确性,以便排除错误。

两种仿真测试:时序仿真;功能仿真;⑤编程下载:把适配后生成的下载或配置文件,通过编程器或下载电缆向FPGA/CPLD 进行下载,以便进行硬件调试和验证。

# CPLD 结构:与或阵列。

MAX7000的5个部分:逻辑阵列块;逻辑宏单元;扩展乘积项;可编程连线阵列;I/O 控制块; # FPGA 结构:查找表逻辑结构。

5个模块:逻辑阵列块;嵌入式存储器块;嵌入式硬件乘法器;I/O 单元;嵌入式PLL 块;# IP 核:IP 是知识产权核或知识产权模块。

# VHDL 程序结构:库与程序包调用声明部分;实体描述部分(电路模块端口描述);结构体描述部分(电路模块功能描述);配置结构部分;# 变量与信号的功能特点及区别:①变量是一个局部量,只能在进程和子程序中使用。

变量的赋值是立即发生的,不存在任何延时行为。

变量的主要作用是在进程中作为临时的数据存储单元。