半导体制程介绍

- 格式:ppt

- 大小:957.50 KB

- 文档页数:97

半导体的生产工艺流程1.晶圆制备:晶圆制备是半导体生产的第一步,通常从硅片开始。

首先,取一块纯度高达99.9999%的单晶硅,然后经过脱氧、精炼、单晶生长和棒状晶圆切割等步骤,制备出硅片。

这些步骤的目的是获得高纯度、无杂质的单晶硅片。

2.晶圆加工:晶圆加工是将硅片加工成具有特定电子器件的过程。

首先,通过化学机械抛光(CMP)去除硅片上的表面缺陷。

然后,利用光刻技术将特定图案投射到硅片上,并使用光刻胶保护未被刻蚀的区域。

接下来,使用等离子刻蚀技术去除未被保护的硅片区域。

这些步骤的目的是在硅片上形成特定的电子器件结构。

3.器件制造:器件制造是将晶圆上的电子器件形成完整的制造流程。

首先,通过高温扩散或离子注入方法向硅片中掺杂特定的杂质,以形成PN结。

然后,使用化学气相沉积技术在硅片表面沉积氧化层,形成绝缘层。

接下来,使用物理气相沉积技术沉积金属薄膜,形成电压、电流等电子元件。

这些步骤的目的是在硅片上形成具有特定功能的电子器件。

4.封装测试:封装测试是将器件封装成实际可使用的电子产品。

首先,将器件倒装到封装盒中,并连接到封装基板上。

然后,通过线缆或焊接技术将封装基板连接到主板或其他电路板上。

接下来,进行电极焊接、塑料封装封装,形成具有特定外形尺寸和保护功能的半导体芯片。

最后,对封装好的半导体芯片进行功能性测试和质量检查,以确保其性能和可靠性。

总结起来,半导体的生产工艺流程包括晶圆制备、晶圆加工、器件制造和封装测试几个主要步骤。

这些步骤的有机组合使得我们能够生产出高性能、高效能的半导体器件,广泛应用于电子产品和信息技术领域。

半导体制程

半导体制程是指将芯片从设计到生产的完整流程,包括晶圆加工、芯片制造、封装测试等诸多环节。

目前,半导体制程已经成为现代科

技产业中不可或缺的重要组成部分。

半导体制程一般分为前端工艺和后端工艺。

前端工艺指晶圆加工

和芯片制造的整个过程,是半导体制程中投入物料最多、工艺最复杂

的一个环节。

后端工艺一般指芯片封装和测试等环节,目的是将芯片

封装好之后,测试其性能是否符合要求。

半导体制程是非常复杂的,需要高度的技术水平和严格的质量控制。

在制程中,任何一个环节的失误都可能会导致整个产品的质量下降,甚至完全报废。

因此,半导体制程需要高度自动化的生产线进行

生产,以保证质量的一致性和产品的稳定性。

总的来说,半导体制程是一个高难度的制造过程,需要科技人员

通过不断的技术创新和工艺改进,始终保持着制程的高精度和高质量。

随着科技不断发展,半导体制程也在不断地演化和升级,为未来科技

领域的发展提供了坚实的基础。

半导体制造流程及生产工艺流程半导体是一种电子材料,具有可变电阻和电子传导性的特性,是现代电子器件的基础。

半导体的制造流程分为两个主要阶段:前端工艺(制造芯片)和后端工艺(封装)。

前端工艺负责在硅片上制造原始的电子元件,而后端工艺则将芯片封装为最终的电子器件。

下面是半导体制造流程及封装的主要工艺流程:前端工艺(制造芯片):1.晶片设计:半导体芯片的设计人员根据特定应用的需求,在计算机辅助设计(CAD)软件中进行晶片设计,包括电路结构、布局和路线规划。

2.掩膜制作:根据芯片设计,使用光刻技术将电路结构图转化为光刻掩膜。

掩膜通过特殊化学处理制作成玻璃或石英板。

3.芯片切割:将晶圆切割成单个的芯片,通常使用钻孔机或锯片切割。

4.清洗和化学机械抛光(CMP):芯片表面进行化学清洗,以去除表面杂质和污染物。

然后使用CMP技术平整芯片表面,以消除切割痕迹。

5.纳米技术:在芯片表面制造纳米结构,如纳米线或纳米点。

6.沉积:通过化学气相沉积或物理气相沉积,将不同材料层沉积在芯片表面,如金属、绝缘体或半导体层。

7.重复沉积和刻蚀:通过多次沉积和刻蚀的循环,制造多层电路元件。

8.清洗和干燥:在制造过程的各个阶段,对芯片进行清洗和干燥处理,以去除残留的化学物质。

9.磊晶:通过化学气相沉积,制造晶圆上的单晶层,通常为外延层。

10.接触制作:通过光刻和金属沉积技术,在芯片表面创建电阻或连接电路。

11.温度处理:在高温下对芯片进行退火和焙烧,以改善电子器件的性能。

12.筛选和测试:对芯片进行电学和物理测试,以确认是否符合规格。

后端工艺(封装):1.芯片粘接:将芯片粘接在支架上,通常使用导电粘合剂。

2.导线焊接:使用焊锡或焊金线将芯片上的引脚和触点连接到封装支架上的焊盘。

3.封装材料:将芯片用封装材料进行保护和隔离。

常见的封装材料有塑料、陶瓷和金属。

4.引脚连接:在封装中添加引脚,以便在电子设备中连接芯片。

5.印刷和测量:在封装上印刷标识和芯片参数,然后测量并确认封装后的器件性能。

半导体制作流程半导体制作流程是指将半导体晶体材料加工成芯片的一系列工艺过程。

具体流程包括晶圆制备、晶圆清洗、晶圆扩散、光刻、蚀刻、沉积、蚀刻、梯度扩散、封装测试等步骤。

首先是晶圆制备。

晶圆是制作芯片的基础材料,一般由单晶硅材料制成。

制备过程涉及到几百个步骤,主要包括材料预处理、单晶生长、切割及铣削等步骤。

这些步骤的目的是得到高质量,无杂质的单晶硅晶圆。

接下来是晶圆清洗。

晶圆上表面可能残留有颗粒、有机物等杂质,会影响到后续工艺的进行。

为此,晶圆需要进行精细清洗,包括热鹼清洗、超声清洗、离子清洗等步骤。

然后是晶圆扩散。

晶圆表面通过高温扩散过程,将特定元素(如硼、砷、磷等)掺杂到晶圆中,改变晶圆的电性能。

这个步骤是形成半导体器件的关键步骤之一。

接下来是光刻。

光刻是指通过光刻胶,将所需的图案传递到晶圆上。

首先,在晶圆上涂上一层光刻胶,然后使用掩膜和曝光机将所需的图案投射到光刻胶上,再通过显影和固化等步骤,将图案进行转移。

然后是蚀刻。

蚀刻是利用化学物质对晶圆表面进行腐蚀,去除不需要的材料。

根据所需图案的要求,可以选择干法蚀刻和湿法蚀刻两种方式。

通过蚀刻可以形成电路图案、孔洞等。

接下来是沉积。

沉积是指将所需材料沉积在晶圆表面,以形成不同的层次结构。

常见的沉积方式有化学气相沉积(CVD)和物理气相沉积(PVD)等。

沉积可以用于生成导电层、绝缘层、金属层等。

然后是梯度扩散。

梯度扩散是一种针对晶圆中特定区域掺杂的工艺。

通过调节不同区域的一些参数,可以实现区域性掺杂,从而形成不同的电子器件。

最后是封装测试。

芯片的制作完成后,需要进行封装和测试。

封装是指将芯片封装在封装盒中,保护芯片并提供外部电气连接。

测试是对封装后的芯片进行功能、电性能等方面的测试,以确保芯片质量。

以上就是半导体制作的基本流程。

需要注意的是,半导体制作是一个高精度、高度自动化的制造过程,涉及到很多物理、化学、工程等学科的知识。

随着技术的不断发展,制作流程也在不断改变和更新,以满足科技发展的需求。

半导体制造详细流程介绍半导体制造是现代电子产业中至关重要的一环,它涉及到了许多复杂而精细的工艺和流程。

本文将详细介绍半导体制造的整个流程。

半导体制造的流程可以分为六个主要步骤:晶圆生长、晶圆切割、晶圆清洗、光刻、离子注入和封装测试。

第一步是晶圆生长。

在这个过程中,纯度极高的硅材料通过化学气相沉积或单晶生长技术被制成硅单晶。

晶圆生长的质量对后续制造工艺至关重要。

第二步是晶圆切割。

在这个步骤中,硅单晶被切割成非常薄的圆片,即晶圆。

晶圆的厚度通常为几毫米到几十微米,这要求切割工艺非常精确。

第三步是晶圆清洗。

在这个过程中,晶圆被放入酸碱溶液中进行清洗,以去除表面的杂质和污染物。

这是为了确保晶圆表面的纯净度,以便后续工艺的顺利进行。

第四步是光刻。

在这个步骤中,光刻胶被涂覆在晶圆表面,然后通过光刻机将光刻胶上的芯片图案转移到晶圆上。

这个过程需要使用紫外线或电子束照射,并使用掩膜来控制芯片图案的形成。

第五步是离子注入。

在这个过程中,离子注入机器将所需的杂质注入晶圆中,以改变晶圆的电学性质。

这个步骤非常关键,因为它决定了晶圆上芯片的导电性能。

最后一步是封装测试。

在这个步骤中,晶圆上的芯片被切割成单个芯片,并封装到芯片包装中。

然后,芯片将被连接到电路板上,并进行各种测试,以确保其正常工作。

整个半导体制造过程需要非常严格的控制和监测,以确保每个步骤都能达到所需的质量标准。

同时,制造过程中的设备和环境条件也需要精确控制,以避免对晶圆的污染或损坏。

除了上述主要步骤外,半导体制造还涉及到许多其他辅助工艺和步骤,如薄膜沉积、化学机械研磨、电镀和退火等。

这些步骤都是为了改善芯片的性能和可靠性。

总结起来,半导体制造是一个高度复杂和精细的过程,涉及到多个步骤和工艺。

每个步骤都需要严格的控制和监测,以确保最终芯片的质量和性能。

随着科技的不断进步,半导体制造也在不断演进和改进,以满足电子产品对于更高性能和更小尺寸的需求。

半导体制程简介半导体制程是一种用于制造半导体器件的工艺过程,是现代电子工业不可或缺的关键部分。

半导体制程可以将硅等材料转化为半导体晶片,进而制造出各种集成电路、微处理器、存储芯片和其他电子器件。

在半导体制程中,首先需要选择合适的半导体材料,最常用的是硅。

硅具有优异的半导体特性和良好的物理特性,成为了制造半导体器件的首选材料。

其他半导体材料如化合物半导体和有机半导体也应用于特定的器件。

接下来是晶片的制备过程,主要包括晶体生长、切割和抛光。

晶体生长是通过高温熔炼和快速冷却,使单晶硅生长为大块晶体。

然后,晶体经过切割成薄片,再通过抛光和平整的过程使其表面光洁平整。

接着是半导体器件的制备过程。

这包括了沉积层、光刻、蚀刻、离子注入和金属化等步骤。

沉积层是通过物理气相沉积(PECVD)或热熔腐蚀(CVD)将薄膜材料沉积在晶片上。

光刻是将光敏胶覆盖在晶片上,然后用紫外线照射到其中的图案模板上,最后通过蚀刻去除未被曝光的区域。

离子注入是将离子通过加速器注入晶片中,改变材料的导电性和电阻率。

金属化是在晶片上涂覆金属,形成电线和电极,用于电子器件的连接。

最后是芯片封装和测试。

封装是将半导体器件连接到外部引脚和包装中,以保护器件并提供适当的电连接。

测试是对芯片进行电性能和可靠性的检查,以确保其正常工作并符合规格要求。

半导体制程是一项复杂而精细的工艺过程,需要严格的控制和高度的精确度。

不断的技术创新和工艺改进使得半导体器件的制造变得越来越高效和可靠。

半导体制程的进步不仅推动了电子技术的发展,还广泛应用于通信、计算机、汽车、医疗和工业等各个领域,为现代社会的科技进步和生活便利做出了巨大贡献。

在半导体制程中,制造芯片的关键技术之一是微影技术。

微影技术是一种将光刻或电子束曝光技术应用于半导体制程中的方法,用于将非常小的结构图案精确地转移到半导体表面,从而实现微小而密集的电子元件。

微影技术的进步极大地促进了半导体技术的发展,使得芯片的功能更加强大、体积更小。

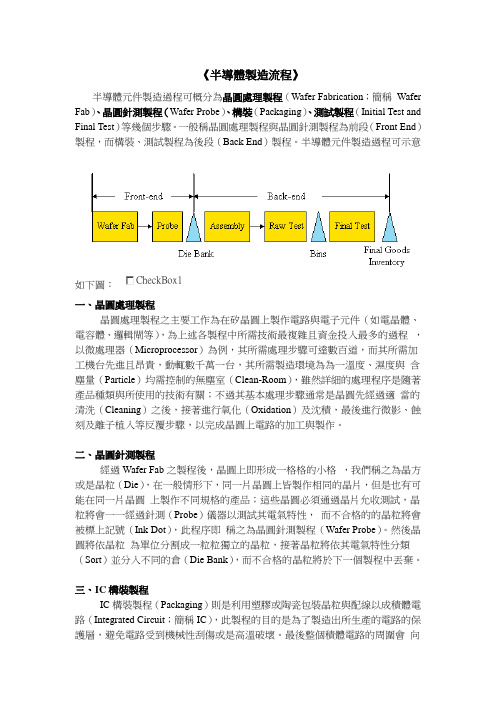

《半導體製造流程》半導體元件製造過程可概分為晶圓處理製程(Wafer Fabrication;簡稱Wafer Fab)、晶圓針測製程(Wafer Probe)、構裝(Packaging)、測試製程(Initial Test and Final Test)等幾個步驟。

一般稱晶圓處理製程與晶圓針測製程為前段(Front End)製程,而構裝、測試製程為後段(Back End)製程。

半導體元件製造過程可示意如下圖:C h e c k B o x1一、晶圓處理製程晶圓處理製程之主要工作為在矽晶圓上製作電路與電子元件(如電晶體、電容體、邏輯閘等),為上述各製程中所需技術最複雜且資金投入最多的過程,以微處理器(Microprocessor)為例,其所需處理步驟可達數百道,而其所需加工機台先進且昂貴,動輒數千萬一台,其所需製造環境為為一溫度、濕度與含塵量(Particle)均需控制的無塵室(Clean-Room),雖然詳細的處理程序是隨著產品種類與所使用的技術有關;不過其基本處理步驟通常是晶圓先經過適當的清洗(Cleaning)之後,接著進行氧化(Oxidation)及沈積,最後進行微影、蝕刻及離子植入等反覆步驟,以完成晶圓上電路的加工與製作。

二、晶圓針測製程經過Wafer Fab之製程後,晶圓上即形成一格格的小格,我們稱之為晶方或是晶粒(Die),在一般情形下,同一片晶圓上皆製作相同的晶片,但是也有可能在同一片晶圓上製作不同規格的產品;這些晶圓必須通過晶片允收測試,晶粒將會一一經過針測(Probe)儀器以測試其電氣特性,而不合格的的晶粒將會被標上記號(Ink Dot),此程序即稱之為晶圓針測製程(Wafer Probe)。

然後晶圓將依晶粒為單位分割成一粒粒獨立的晶粒,接著晶粒將依其電氣特性分類(Sort)並分入不同的倉(Die Bank),而不合格的晶粒將於下一個製程中丟棄。

三、IC構裝製程IC構裝製程(Packaging)則是利用塑膠或陶瓷包裝晶粒與配線以成積體電路(Integrated Circuit;簡稱IC),此製程的目的是為了製造出所生產的電路的保護層,避免電路受到機械性刮傷或是高溫破壞。

半导体制程简介一、洁净室一般的机械加工是不需要洁净室(clean room)的,因为加工分辨率在数十微米以上,远比日常环境的微尘颗粒为大。

但进入半导体组件或微细加工的世界,空间单位都是以微米计算,因此微尘颗粒沾附在制作半导体组件的晶圆上,便有可能影响到其上精密导线布局的样式,造成电性短路或断路的严重后果,为此,所有半导体制程设备,都必须安置在隔绝粉尘进入的密闭空间中,这就是洁净室的来由。

洁净室的洁净等级,有一公认的标准,以class 10为例,意谓在单位立方英尺的洁净室空间内,平均只有粒径0.5微米以上的粉尘10粒。

所以class后头数字越小,洁净度越佳,当然其造价也越昂贵。

为营造洁净室的环境,有专业的建造厂家,及其相关的技术与使用管理办法如下:1、内部要保持大于一个大气压的环境,以确保粉尘只出不进。

所以需要大型鼓风机,将经滤网的空气源源不绝地打入洁净室中。

2、为保持温度与湿度的恒定,大型空调设备须搭配于前述之鼓风加压系统中。

换言之,鼓风机加压多久,冷气空调也开多久。

3、所有气流方向均由上往下为主,尽量减少突兀之室内空间设计或机台摆放调配,使粉尘在洁净室内回旋停滞的机会与时间减至最低程度。

4、所有建材均以不易产生静电吸附的材质为主。

5、所有人事物进出,都必须经过空气吹浴(air shower) 的程序,将表面粉尘先行去除。

6、人体及衣物的毛屑是一项主要粉尘来源,为此务必严格要求进出使用人员穿戴无尘衣,除了眼睛部位外,均需与外界隔绝接触(在次微米制程技术的工厂内,工作人员几乎穿戴得像航天员一样。

) 当然,化妆是在禁绝之内,铅笔等也禁止使用。

7、除了空气外,水的使用也只能限用去离子水(DI water, de-ionized water)。

一则防止水中粉粒污染晶圆,二则防止水中重金属离子,如钾、钠离子污染金氧半(MOS,以金属-氧化物-半导体场效应晶体管为主要元件构成的集成电路) 晶体管结构之带电载子信道(carrier channel),影响半导体组件的工作特性。

半导体制程及原理介绍半导体是一种介于导体和绝缘体之间的材料,具有优良的电气特性。

在现代电子技术中,半导体材料被广泛应用于电子器件和集成电路中。

半导体器件的制造过程被称为半导体制程,本文将介绍半导体制程的工艺流程,以及制作半导体器件时涉及到的原理和技术。

半导体工艺流程半导体制程包含多个工序,一般分为六个步骤:1.前工艺:前工艺包含晶圆清洗、分切、抛光和衬底烘烤。

在这一阶段,旨在确保晶圆表面光滑无瑕疵,为后续的工艺提供良好的基础。

2.沉积工艺:沉积工艺主要包括化学气相沉积和物理气相沉积。

这个步骤的主要目的是对晶圆表面进行原子层沉积,形成薄膜,如硅酸盐。

3.光刻工艺:光刻工艺是在晶圆上印刷图案的过程,主要利用紫外光照射。

这个步骤的目的是在晶圆表面添加一层遮光剂,以保护晶圆的某些区域,防止化学腐蚀。

4.蚀刻工艺:蚀刻工艺是“刻蚀”晶圆表面的化学过程,一般利用氢氟酸蚀刻掉不需要的部分。

这个步骤的目的是通过蚀刻去除遮光剂之外的区域,形成所需的结构。

5.离子注入:离子注入工艺是向晶圆表面注入离子,以改变其电学性质。

这个步骤的目的是在特定区域(如接线)注入特定的材料,从而改变半导体的导电性能。

6.后工艺:后工艺包括切割晶圆、清洗、烧结蓝宝石和金属连接。

这个步骤的目的是完成器件的制造过程,并确保器件能够正常工作。

半导体器件的制作原理半导体制程中的制作原理是在半导体材料内部控制杂质浓度,从而控制其导电性能,从而制造高性能的半导体器件。

半导体材料通常分为p型半导体和n型半导体。

p型半导体中掺杂的杂质主要是硼、铝和镓,n型半导体中掺杂的杂质主要是砷、锑和磷。

在p型半导体和n型半导体中,杂质浓度的差异导致了不同的载流子浓度和导电性能。

当p型半导体和n型半导体结合时,形成了PN结构。

在PN结构中存在一个空间电荷区,该区域是导体和绝缘体之间的过渡区域,称为“耗尽层”。

PN结构中的电子可以从n型半导体流向p型半导体,形成电流。

半导体的工艺制程

半导体的工艺制程指的是将半导体材料转化为电子器件的过程。

一般而言,半导体的工艺制程包括以下几个步骤:

1. 衬底制备:选择合适的衬底材料,如硅(Si),并进行化学处理和晶体生长,以获得高纯度的单晶硅片。

2. 清洗和薄化:将硅片进行化学清洗,去除表面杂质和氧化物,然后使用机械方法将硅片变薄。

3. 晶圆上刻蚀掩膜:在硅片表面上涂覆一层光刻胶,然后使用光刻技术,将预先设计好的图案投射在光刻胶上。

经过显影和蚀刻,将图案转移到硅片上。

4. 氧化和扩散:使用化学气相沉积(CVD)技术,在硅片表面生成氧化硅层。

然后,通过高温扩散,将所需的杂质(如磷、硼等)引入硅片表面,形成所需的电性区域。

5. 金属沉积和刻蚀:使用物理气相沉积(PVD)或化学气相沉积(CVD)技术,在硅片表面上沉积金属层(如铝或铜)作为导线。

然后,通过蚀刻技术,去除无用的金属,形成导线。

6. 制备更多的层:重复以上步骤,制备更多的杂质和金属层。

7. 封装和测试:将芯片切割成单个的器件,并使用封装技术将它们封装到塑料或陶瓷封装中。

然后,进行测试,以确保器件的功能和性能符合设计要求。

这些是半导体的典型工艺制程步骤,不同类型的半导体器件可能会有一些特殊的制程步骤。

半导体制程简介半导体制程是指制造半导体器件所需的一系列工艺步骤和设备。

它是将材料转换为具有特定功能的半导体器件的过程,多数情况下是芯片制造的关键部分。

半导体制程通常分为六个主要步骤:前道工艺、IC 设计、曝光与衬底处理、薄膜沉积、刻蚀与清洗、以及后道工艺。

前道工艺是半导体制程的起始阶段。

在这个阶段,制造商会选择适合的衬底材料(通常是硅),并使用一系列的物理和化学方法准备它,以便于后续的加工。

IC 设计是将半导体器件的功能、结构和电路设计成电子文件的过程。

这些文件将被用于后续的曝光与衬底处理。

曝光与衬底处理是半导体制程的关键步骤之一。

在这个步骤中,使用光刻机将设计好的电子文件投射到光敏材料上,形成模式。

然后,通过化学方法去除暴露的材料,从而得到衬底上的所需结构。

这些步骤会多次重复,以逐渐形成多层结构。

在薄膜沉积阶段,使用化学蒸气沉积(CVD)或物理蒸镀(PVD)等方法将薄膜材料沉积到衬底上。

这些膜层将用于实现器件的不同功能,如导电层、绝缘层和隔离层等。

刻蚀与清洗是将多余的材料从衬底上去除的过程。

使用化学或物理方法,将不需要的材料刻蚀掉,并进行清洗和检查,确保器件的质量和一致性。

后道工艺是半导体制程的最后阶段。

在这个阶段中,制造商会进行结构和线路的连接,以及器件的测试和封装等。

这些步骤将半导体器件转换为实际可用的芯片。

半导体制程是一个复杂而精细的过程。

通过精确的控制和不断的优化,制造商可以获得高质量、高性能的半导体器件。

这些器件在现代技术中发挥着重要的作用,包括计算机、通信设备、消费电子产品等。

因此,半导体制程在推动科技进步和社会发展中扮演着重要的角色。

半导体制程在现代科技领域扮演着极为重要的角色。

随着信息技术的发展和人们对高性能电子设备的需求不断增长,半导体制程成为了现代社会的基石之一。

在这方面,特别值得一提的是摩尔定律。

摩尔定律是一种经验规律,它指出在相同面积上可以容纳的晶体管数量每隔大约18-24个月将翻一番,同时造价也会下降50%。

半导体制程半导体制程是指将半导体材料加工成电子器件的过程。

半导体材料是一种介于导体和绝缘体之间的材料,具有良好的电子传导性能和电子隔离性能。

半导体制程是半导体工业的核心技术之一,其重要性不言而喻。

半导体制程的主要步骤包括晶圆制备、光刻、蚀刻、沉积、清洗等。

晶圆制备是半导体制程的第一步,其目的是制备出高质量的半导体晶圆。

晶圆制备的过程包括晶圆生长、切割、抛光等步骤。

晶圆生长是指将半导体材料生长成晶体,常用的方法有Czochralski法、分子束外延法等。

晶圆切割是指将生长好的晶体切割成薄片,常用的方法有线锯切割、切割盘切割等。

晶圆抛光是指将切割好的晶圆进行抛光处理,以获得高质量的表面。

光刻是半导体制程中的重要步骤之一,其目的是将芯片上的电路图案转移到晶圆表面。

光刻的过程包括涂覆光刻胶、曝光、显影等步骤。

涂覆光刻胶是指将光刻胶涂覆在晶圆表面,以便进行曝光。

曝光是指将光刻胶暴露在紫外线下,以形成芯片上的电路图案。

显影是指将曝光后的光刻胶进行显影处理,以去除未曝光的部分,形成芯片上的电路图案。

蚀刻是半导体制程中的另一个重要步骤,其目的是将芯片上的电路图案转移到晶圆表面。

蚀刻的过程包括干法蚀刻、湿法蚀刻等步骤。

干法蚀刻是指将晶圆表面暴露在高能离子束下,以去除未被光刻胶保护的部分。

湿法蚀刻是指将晶圆表面暴露在化学溶液中,以去除未被光刻胶保护的部分。

沉积是半导体制程中的另一个重要步骤,其目的是在晶圆表面沉积一层薄膜,以形成芯片上的电路元件。

沉积的过程包括物理气相沉积、化学气相沉积、物理溅射沉积等步骤。

物理气相沉积是指将材料蒸发在真空中,以形成薄膜。

化学气相沉积是指将材料在化学反应中沉积在晶圆表面,以形成薄膜。

物理溅射沉积是指将材料溅射在晶圆表面,以形成薄膜。

清洗是半导体制程中的最后一步,其目的是去除晶圆表面的杂质和残留物,以保证芯片的质量。

清洗的过程包括化学清洗、超声波清洗等步骤。

化学清洗是指将晶圆浸泡在化学溶液中,以去除表面的杂质和残留物。

半导体制造主要流程

半导体制造是现代电子工业的重要组成部分,它涉及到从原材料到成品的多个环节和复杂的工艺流程。

下面我们将介绍半导体制造的主要流程。

1. 原材料准备。

半导体的制造过程通常以硅为主要原材料。

硅是地壳中丰富的资源,通过提炼和精炼,可以得到高纯度的硅片。

此外,还需要其他材料如磷、硼等作为杂质掺杂剂。

2. 单晶生长。

通过化学气相沉积(CVD)或者其他方法,将高纯度的硅材料生长成单晶圆片。

这个过程需要高温高压环境,确保单晶的结构和纯度。

3. 晶圆加工。

将单晶硅圆片进行多道工艺加工,包括切割、抛光、清洗等步

骤,最终得到薄而均匀的晶圆。

4. 掺杂。

通过掺入磷、硼等杂质,改变硅的导电性质,形成N型和P型

半导体材料。

5. 晶体管制造。

在晶圆上制造晶体管,包括光刻、蚀刻、沉积等工艺,将导电

性区域和绝缘区域精确地形成。

6. 封装测试。

将晶体管封装到芯片内,进行测试和封装成最终的半导体器件。

以上就是半导体制造的主要流程,这是一个高度精密和复杂的

过程,需要先进的设备和技术,同时也需要严格的质量控制和环境

管理。

半导体制造的发展推动了现代电子科技的进步,也为人类社

会的发展带来了巨大的便利和进步。

半导体生产流程半导体是一种能够在一定条件下导电或者绝缘的材料,它在现代电子工业中扮演着非常重要的角色。

半导体的生产流程经过多道工序,需要高度的精密和技术。

下面,我们将详细介绍半导体的生产流程。

第一步,原料准备。

半导体的主要原料是硅,而硅又需要经过提纯处理,以保证半导体的质量。

在这一步,硅原料会经过多道净化工序,包括溶解、结晶、凝固等过程,最终得到高纯度的硅单晶。

第二步,晶圆生产。

经过原料准备的硅单晶会被切割成薄片,形成所谓的晶圆。

晶圆的表面需要进行化学处理和机械抛光,以确保表面的平整和纯净度。

第三步,光刻。

光刻是半导体生产中的关键工序,它使用光刻胶和掩膜来定义芯片上的图形。

通过光刻,可以在晶圆表面形成微小的电路图案。

第四步,离子注入。

在离子注入工序中,半导体晶圆会被注入掺杂物质,以改变其电学特性。

这一步骤能够在晶体内部形成p型和n型半导体区域,从而形成晶体管和二极管等元件。

第五步,薄膜沉积。

在薄膜沉积工序中,半导体晶圆会被涂覆上一层薄膜,通常是氧化层或者氮化层。

这些薄膜可以用来隔离不同的电路元件,或者作为绝缘层。

第六步,金属化。

在金属化工序中,半导体晶圆的表面会被涂覆上金属层,通常是铝或者铜。

这些金属层可以用来连接不同的电路元件,形成完整的电路结构。

第七步,封装测试。

最后,半导体芯片会被封装在塑料或者陶瓷封装体中,以保护其免受外部环境的影响。

之后,芯片会被进行测试,以确保其性能和质量符合标准要求。

总的来说,半导体的生产流程经过多道工序,需要高度的精密和技术。

每一个工序都对半导体的质量和性能有着重要的影响,因此在生产过程中需要严格控制每一个环节,以确保最终产品的质量和可靠性。

半导体六大制造工艺流程

半导体制造通常涉及六大制造工艺流程,它们是晶体生长、晶

圆加工、器件加工、器件封装、测试和最终组装。

让我逐一详细解

释这些工艺流程。

首先是晶体生长。

在这一阶段,晶体生长炉中的硅原料被加热

至高温,然后通过化学反应使其结晶成为硅单晶棒。

这些单晶棒随

后被切割成薄片,即晶圆。

接下来是晶圆加工。

在这个阶段,晶圆表面被涂覆上光敏树脂,并通过光刻技术进行图案转移,然后进行腐蚀、沉积和离子注入等

步骤,以形成电路图案和器件结构。

第三个阶段是器件加工。

在这个阶段,晶圆上的器件结构被形成,包括晶体管、二极管和其他电子元件。

这一过程通常包括清洗、光刻、腐蚀、沉积和离子注入等步骤。

接下来是器件封装。

在这一阶段,芯片被封装在塑料或陶瓷封

装中,并连接到外部引脚。

这一过程旨在保护芯片并为其提供连接

到电路板的手段。

第五个阶段是测试。

在这一阶段,封装的芯片将被测试以确保

其功能正常。

这可能涉及电学测试、可靠性测试和其他类型的测试。

最后一个阶段是最终组装。

在这一阶段,封装的芯片被安装到

电路板上,并连接到其他组件,如电源、散热器等。

这一阶段也包

括整个产品的最终组装和包装。

总的来说,半导体制造的六大工艺流程涵盖了从原材料到最终

产品的整个生产过程,每个阶段都至关重要,对最终产品的质量和

性能都有着重要的影响。

半導體製程簡介半导体制程是指用于制造半导体材料和器件的工艺流程。

半导体器件是现代电子技术的基础,几乎所有的电子产品都离不开半导体器件的应用。

半导体制程的发展对提升电子产品的性能和功能至关重要。

半导体制程包括前工艺和后工艺两个部分。

前工艺是指对硅片进行刻蚀、沉积、掺杂、光刻等工艺,用于形成各种晶体管、电容器和传感器等器件。

后工艺是指将切割得到的芯片进行封装、测试和贴片等工艺,以便进行成品制造和使用。

首先,前工艺的第一步是进行清洗和化学机械抛光,以去除表面的污染物和缺陷。

清洗后,需要进行氧化处理,形成一层薄的氧化硅层,用于保护硅片表面和形成绝缘层。

接下来是光刻工艺,利用光刻胶和掩膜模具进行曝光和显影,将所需器件的图案转移到硅片上。

通过光刻工艺,可以制造出微小的结构和线路。

光刻的精度与分辨率决定了芯片的性能和功能。

在光刻后,需要进行刻蚀和沉积工艺。

刻蚀是利用化学或物理手段去除不需要的材料或形成凹凸结构。

沉积是将一层薄的材料沉积在硅片表面,如金属、氧化物或多晶硅。

刻蚀和沉积工艺的选择和优化,可以控制器件的形状、性能和功能。

掺杂是半导体制程中的重要步骤。

通过掺入杂质原子,可以改变半导体材料的导电性质。

常用的掺杂元素有硼、磷和砷等。

掺杂后,需要进行退火处理,以激活和固定杂质原子。

完成了前工艺后,需要进行后工艺。

首先是切割芯片,将硅片切割成小的芯片单元,以便进行后续的封装。

然后是封装工艺,将芯片焊接到外部引脚和封装底座上,以便进行电路连接。

封装工艺的设计和调试,对产品的可靠性和稳定性有着重要影响。

最后是芯片测试和贴片工艺。

芯片测试是对芯片进行性能和功能的验证和测量。

贴片工艺是将芯片封装到电子产品中,如手机、笔记本电脑和汽车等。

贴片工艺要求精细和高效,以满足大规模生产的需求。

半导体制程的发展经历了多个技术革新和突破。

从最初的二极管、晶体管到现在的集成电路和纳米器件,半导体制程不断创新和进步,推动了电子技术的发展。

半导体工艺制程

半导体制程是指制造一片芯片的流程,从最简单的硅晶圆片开始,经过设计、制造、封装等步骤,再加上测试,才能制成一块完整的芯片。

半导体制程可分为三个主要步骤:第一是“硅晶圆片”,第

二是“晶圆”,第三是“芯片”。

硅晶圆片是指制造IC芯片所用

的硅片。

1.“硅晶圆片”:制造半导体芯片需要大量的硅片,这些硅

片通常由硅、石墨、氧化硅等材料制成。

制作硅晶圆片的方法有很多种,其中最常用的是光刻。

光刻技术是用光来控制物质和气体的流动方向,利用光照射在硅片上形成的薄膜来刻蚀图形。

2.晶圆:把晶圆(也称晶圆片)上一层一层地剥离开来就可以得到半导体芯片了。

晶圆表面上有很多微小的孔洞,这些孔洞就叫栅极。

这些栅极就像是一块磁铁,把电子吸引到这些孔洞中去,然后通过半导体材料的性质让电子穿过栅极从而实现电路功能。

3.芯片:将栅极上的电子通过晶体管等电路元件转化为电流,并以一定频率进行周期性的流动。

(因此产生了开关效应)从而

实现信号的产生和传输。

—— 1 —1 —。