3位十进制循环计数器

- 格式:doc

- 大小:166.50 KB

- 文档页数:23

班级09111学号09111008本科毕业设计论文题目基于CD4553三位数显计数器的设计学院长安学院专业通信工程学生姓名李凡导师姓名陈晓毕业设计(论文)诚信声明书本人声明:本人所提交的毕业设计论文《基于CD4553三位数显计数器的设计》是本人在指导教师指导下独立研究、写作的成果,论文中所引用他人的无论以何种方式发布的文字、研究成果,均在论文中加以说明:有关教师、同学和其他人员的写作、修订提出过并为我在论文中加以采纳的意见、建议,均已在我的致谢辞中加以说明并深致谢意。

本论文和资料若有不实之处,本人承担一切相关责任。

论文作者:(签字)时间:2013年5月25日指导教师已阅:(签字)时间:2013年5月25日西安电子科技大学长安学院毕业设计(论文)任务书学生姓名李凡学号09111008指导教师陈晓职称副教授学院长安学院专业通信工程题目名称基于CD4553三位数显计数器的设计任务与要求:任务:1、围绕毕业设计任务调研、查资料;2、汇总资料,完成调研报告;3、设计固态源。

要求:1、windows2000以上为计算机平台必须;2、论文立论,设计过程要求明晰;3、书写美观大方。

开始日期2013年1月10日完成日期2013年5月25日院长(签字)2013年月日注:本任务书一式两份,一份交学院,一份学生自己保存。

西安电子科技大学长安学院毕业设计(论文)工作计划学生姓名李凡学号09111008指导教师陈晓职称副教授学院长安学院专业通信工程题目名称基于CD4553三位数显计数器的设计一、毕业设计(论文)进度起止时间工作内容2013.1.10~2013.3.10 调研目前计数器的内外状况,查资料2013.3.11~2013.4.10 构建系统模型,画框图,流程图,进行初步设计,准备材料2013.4.1~2013.4.30 设计具体电路,进行装备、调试2013.5.1~2013.5.15 整理文档,撰写论文,送审论文初稿2013.5.15~2013.5.25 修改完成论文、幻灯片,准备答辩二、主要参考书目(资料)[1] 康华光,电子技术基础:模电部分(第四版)[M],北京:高等教育出版社;[2] 何东健,耿楠,张一宽,《数字图像处理》,西安电子科技大学出版社,2008;[3] 江晓安,董秀峰,《模拟电子技术》,西安电子科技大学出版社,2008;[4] 江晓安,董秀峰,杨颂华,《数字电子技术》,西安电子科技大学出版社,2008;三、主要仪器设备及材料硬件:计算机、三用表、电烙铁等四、教师的指导安排情况(场地安排、指导方式等)每周指导、汇报一次工作西电C教学楼,C-523教室五、对计划的说明注:本计划一式两份,一份交学院,一份学生自己保存(计划书双面打印)。

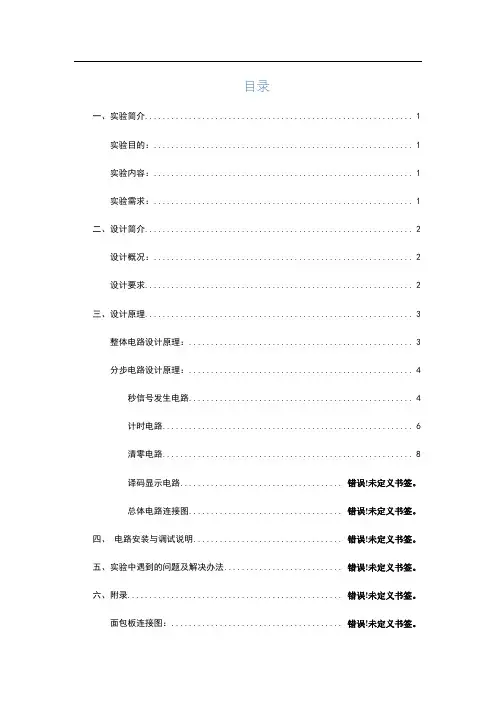

目录1课程设计的目的与作用...................................... 错误!未定义书签。

2设计任务.................................................. 错误!未定义书签。

2.1加法计数器........................................... 错误!未定义书签。

2.2序列信号发生器....................................... 错误!未定义书签。

2.3 256进制的加法器..................................... 错误!未定义书签。

3设计原理.................................................. 错误!未定义书签。

3.1加法计数器........................................... 错误!未定义书签。

3.2序列信号发生器 (2)3.3用集成芯片设计一个256进制的加法器 (2)4实验步骤 (3)4.1加法计数器 (3)4.2序列信号发生器 (7)4.3用集成芯片设计一个256进制的加法器 (9)5仿真结果与分析 (11)6设计总结与体会 (11)7参考文献.................................................. 错误!未定义书签。

1课程设计的目的与作用1.了解同步计数器及序列信号发生器工作原理;2.掌握计数器电路的分析,设计方法及应用;3.掌握序列信号发生器的分析,设计方法及应用2 设计任务2.1加法计数器1.设计一个循环型3位2进制加法计数器,其中无效状态为(000,001),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

2.2序列信号发生器1.设计一个能循环产生给定序列的序列信号发生器,其中发生序列(0001),组合电路选用与门和与非门等。

十进制计数器简介十进制计数器是一种常见的计数器类型,用于在电子设备和计算机中记录和显示数字。

它由一组数字显示单元和逻辑电路构成,能够按照十进制系统的规则进行计数。

本文将介绍十进制计数器的工作原理、应用领域以及常见的实现方法。

工作原理十进制计数器的工作原理基于十进制数字系统。

十进制系统是一种计数和计量的方法,使用0-9这10个数字,每个数字的值代表了一定的数量。

十进制计数器通过逐个增加计数器中的数字,从0递增到9,然后再回到0,形成一个循环。

十进制计数器通常由多个数字显示单元组成,每个显示单元可以显示一个数字。

例如,一个四位的十进制计数器可以显示0至9999的数值。

计数器中的逻辑电路能够根据当前的计数值控制各个显示单元的状态,使其按照正确的顺序显示相应的数字。

应用领域十进制计数器在很多领域都有广泛的应用,特别是在计算机技术和电子设备中。

以下是一些常见的应用领域:1. 计算机在计算机中,十进制计数器用于记录和控制程序的执行次数、计时器和时钟。

例如,计算机中的时钟电路经常使用十进制计数器来实现时间的计算和显示。

2. 电子设备在许多电子设备中,如数字电子表、计算器、计数器、时钟等,都使用了十进制计数器。

它们能够以人类可读的方式显示数字,方便用户进行数值的输入和查看。

3. 工业自动化在工业自动化领域,十进制计数器可以用于对生产线上的产品数量进行计数和控制。

当计数器达到预设的数量时,可以触发相应的操作,如停止生产线或自动分拣产品。

4. 计量仪器在科学实验和工程测量中,十进制计数器被广泛用于记录和显示测量结果。

例如,在温度计、压力计、计时器等仪器中,都使用了十进制计数器来显示测量的数值。

实现方法十进制计数器可以使用不同的电子元件和逻辑电路进行实现。

以下是一些常见的实现方法:1. 逻辑门电路通过组合逻辑门电路,可以实现简单的十进制计数器。

例如,使用4个D型触发器和若干个与、或、非门,可以构建一个四位的十进制计数器。

EDA实验报告实验三、4位十进制的频率计设计班级115学号姓名日期2010.11.2一、实验目的1、设计4位十进制频率计,学习较复杂的数字系统设计方法,熟悉对Quartus II 软件的使用。

2、用4位十进制计数器对用户输入时钟UCLK进行记数二、实验原理:根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值被锁入锁存器,计数器清零,为下一测频计数周期作准备。

这3个信号可以由一个测频控制信号发生器产生下图中的TESTCTL,它的设计要求是:TESTCTL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进各锁存器REG4B中,并由外部的7段译码器译出,显示计数值。

设置锁存器的好处是:显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号之后,必须有一清零信号RST_CNT对计数器进行清零,为下1秒钟的计数操作作准备。

4位十进制频率计设计的原理框图四、实验步骤及结果五、1破解软件2、新建工程3、程序输入及编译新建文件并输入程序并进行编译。

实验VHDL程序代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY EX10 ISPORT (clk1Hz : IN STD_LOGIC; -- 1 Hz clockuclk : IN STD_LOGIC; -- user clock inputled0 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); led1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); led2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); led3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);p_cnt_en : OUT STD_LOGIC; -- IO01p_rst_cnt: OUT STD_LOGIC; -- IO00p_load : OUT STD_LOGIC -- IO02);END EX10;ARCHITECTURE behv OF EX10 ISCOMPONENT cnt10PORT (clk : IN STD_LOGIC;rst : IN STD_LOGIC;ena : IN STD_LOGIC;outy: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);cout: OUT STD_LOGIC);END COMPONENT;COMPONENT reg4bPORT (load: IN STD_LOGIC;din : IN STD_LOGIC_VECTOR(3 DOWNTO 0);dout: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT testctlPORT (clkk : IN STD_LOGIC;cnt_en : OUT STD_LOGIC;rst_cnt: OUT STD_LOGIC;load : OUT STD_LOGIC);END COMPONENT;SIGNAL cnt_en : STD_LOGIC;SIGNAL rst_cnt : STD_LOGIC;SIGNAL load : STD_LOGIC;SIGNAL dout0, dout1, dout2, dout3: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL cout0, cout1, cout2, cout3: STD_LOGIC;BEGINp_cnt_en <= cnt_en ;p_rst_cnt <= rst_cnt;p_load <= load ;u_testctl:testctl PORT MAP (clkk => clk1Hz ,cnt_en => cnt_en ,rst_cnt => rst_cnt,load => load); u_cnt10_0:cnt10 PORT MAP (clk => uclk ,rst => rst_cnt,ena => cnt_en ,outy => dout0 ,cout => cout0 );u_cnt10_1:cnt10 PORT MAP (clk => cout0 ,rst => rst_cnt,ena => cnt_en ,outy => dout1 ,cout => cout1 );u_cnt10_2:cnt10 PORT MAP (clk => cout1 ,rst => rst_cnt,ena => cnt_en ,outy => dout2 ,cout => cout2 );u_cnt10_3:cnt10 PORT MAP (clk => cout2 ,rst => rst_cnt,ena => cnt_en ,outy => dout3 ,cout => cout3 );u_reg4b_0:reg4b PORT MAP (load => load ,din => dout0, dout => led0);u_reg4b_1:reg4b PORT MAP (load => load ,din => dout1,dout => led1);u_reg4b_2:reg4b PORT MAP (load => load ,din => dout2,dout => led2);u_reg4b_3:reg4b PORT MAP (load => load ,din => dout3,dout => led3);END behv;TESTCTL.VHD 程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY testctl ISPORT (clkk : IN STD_LOGIC;cnt_en : OUT STD_LOGIC;rst_cnt: OUT STD_LOGIC;load : OUT STD_LOGIC);END testctl;ARCHITECTURE behv OF testctl IS SIGNAL div2clk: STD_LOGIC;BEGINPROCESS(clkk)BEGINIF clkk'EVENT AND clkk = '1' THENdiv2clk <= NOT div2clk;END IF;END PROCESS;PROCESS(clkk, div2clk) BEGINIF clkk = '0' AND div2clk = '0' THENrst_cnt <= '1';ELSErst_cnt <= '0';END IF;load <= NOT div2clk;cnt_en <= div2clk;END PROCESS;END behv;LIBRARY IEEE;USEIEEE.STD_LOGIC_1164.ALL; USEIEEE.STD_LOGIC_UNSIGNED. ALL;ENTITY cnt10 ISPORT (clk : IN STD_LOGIC;rst : IN STD_LOGIC;ena : IN STD_LOGIC; outy: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);cout: OUT STD_LOGIC);END cnt10;ARCHITECTURE behv OF cnt10 ISSIGNAL cqi: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk, rst, ena) BEGINIF rst = '1' THENcqi <= "0000";cout <= '0';ELSIF clk'EVENT AND clk = '1' THENIF ena = '1' THENIF cqi = "1001" THENcqi <= "0000";cout <= '1';ELSEcqi <= cqi + 1;cout <= '0';END IF;END IF;END IF;outy <= cqi;END PROCESS;END behv;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY reg4b ISPORT (load: IN STD_LOGIC;din : IN STD_LOGIC_VECTOR(3 DOWNTO 0); dout: OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END reg4b;ARCHITECTURE behv OF reg4b ISBEGINPROCESS(load)BEGINIF load'EVENT AND load = '1' THENdout <= din;END IF;END PROCESS;END behv;打开RTL图形时序仿真:打开“assignments”中的“assignments editor”打开EDA,装入模式10.根据EDA 管脚进行指定保存,并下载“sof”文件到EDA启动EDA软件。

在数字系统中,常需要对时钟脉冲的个数进行计数,以实现测量、运算和控制等功能。

具有计数功能的电路,称为计数器。

计数器是一种非常典型、应用很广的时序电路,计数器不仅能统计输入时钟脉冲的个数,还能用于分频、定时、产生节拍脉冲等。

计数器的类型很多,按计数器时钟脉冲引入方式和触发器翻转时序的异同,可分为同步计数器和异步计数器;按计数体制的异同,可分为二进制计数器、二—十进制计数器和任意进制计数器;按计数器中的变化规律的异同,可分为加法计数器、减法计数器和可逆计数器。

二进制加法计数器运用起来比较简洁方便,结构图和原理图也比其它进制的简单明了,但二进制表示一个数时,位数一般比较长。

十进制是我们日常生活中经常用到的,不用转换,所以设计十进制加法计数器比设计二进制加法计数器应用广泛,加法器是以数据的累加过程,日常生活中,数据的累加普遍存在,有时候需要一种计数器对累加过程进行运算处理,所以设计十进制加法计数器应广大人们生活的需要,对我们的生活有一个积极地促进作用,解决了生活中许多问题,所以会设计十进制加法计数器使我们对数字电路的理论和实践知识的充分结合,也使我们对电子技术基础有了深刻的了解,而且增强了我们对电子技术基础产生了浓厚的兴趣,这次课程设计使我受益匪浅!一、设计题目 (3)二、设计目的 (3)三、设计依据 (3)四、设计内容 (3)五、设计思路 (4)六、设计方案 (7)七、改进意见 (10)八、设计总结 (11)九、参考文献 (12)一、设计题目十进制加法计数器二、设计目的1.学习电子电路设计任务。

2.通过课程设计培养学生自学能力和分析问题、解决问题的能力。

3.通过设计使学生具有一定的计算能力、制图能力以及查阅手册、使用国家技术标准的能力和一定的文字表达能力。

三、设计依据1.用JK触发器组成。

2.实现同步或异步加法计数。

四、设计内容1.复习课本,收集查阅资料,选定设计方案;2.绘制电气框图、电气原理图;3.对主要元器件进行计算选择,列写元器件的规格及明细表;4.设计总结及改进意见;5.参考资料;6.编写说明书。

现代电子设计实验报告实验名称:3位十进制循环计数器的设计系(科):信息科学与技术系班级:学号:姓名:完成时间:2012年4月24日. 1 .一、实验内容(一)设计要求1.设计一个3位十进制循环计数器,从0加到999,再恢复到0,循环往复。

每秒计数器加1。

2.有复位功能,当复位端reset为高时,计数器清零,停止计数。

3.可以控制计数的开始start和停止stop。

当计数开始start信号有效时,计数器开始计数;当计数停止stop信号有效时,计数停止;当start信号再次有效时,继续计数。

4.计数器的计数值采用动态显示方式在数码管上显示出来。

5.进行设计,仿真并下载程序到实验箱的CPLD模块板进行验证。

(二)电路模块cyclecntsysclk reset startSE G[6. SCAN[7.★提示:reset信号可以使用拨动开关来产生。

start和stop信号使用按键来实现输入信号:sysclk:基准时钟,50MHz;reset:异步复位信号,高有效;start,stop:计数开始和计数停止信号输入;. 2 .输出信号:SEG[6..0]:段码信号输出。

SCAN[7..0]:位码信号输出。

二、实验原理此系统的核心为一个三位循环计数器,将此计数器的输出结果通过分位电路动态显示到三个数码管上面。

另外的辅助电路分别为四个不同频率的分频器和按键去抖电路。

三、设计方案四、原理图. 3 .. 4 .五、模块设计(一)分频电路1.设计原理分频器就是对较高频率的信号进行分频,得到较低频率的信号。

定义一个计数器对输入时钟进行计数,在计数的前一半时间里,输出高电平,在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

例如,6分频,计数值为0~2输出高电平,计数值为3~5输出低电平。

2.VHDL程序代码输出为1HZ分频电路N=50MHZ/1HZ=50000000Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv1 isgeneric(N: integer:=50000000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv1;Architecture a of fdiv1 is. 5 .signal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为10HZ分频电路N=50MHZ/10HZ=5000000. 6 .Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=5000000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 issignal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;. 7 .process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为200HZ分频电路N=50MHZ/200HZ=250000Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=250000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 is. 8 .signal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为1000HZ分频电路N=50MHZ/1000HZ=50000Library ieee;. 9 .Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=50000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 issignal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平. 10 .beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;(二)扫描电路1.设计原理当reset和stop信号起作用时,输出到计数器的信号为低电平,只有当start 和脉冲信号起作用时,输出才为高。

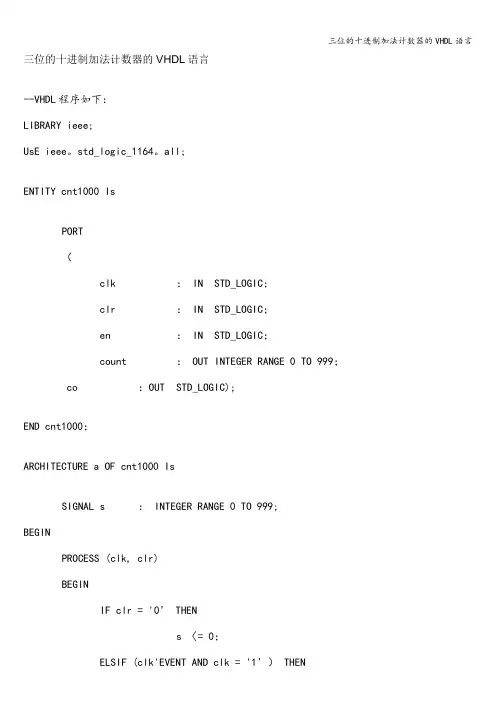

三位的十进制加法计数器的VHDL语言--VHDL程序如下:LIBRARY ieee;UsE ieee。

std_logic_1164。

all;ENTITY cnt1000 IsPORT(clk : IN STD_LOGIC;clr : IN STD_LOGIC;en : IN STD_LOGIC;count : OUT I NTEGER RANGE 0 TO 999; co :OUT STD_LOGIC);END cnt1000;ARCHITECTURE a OF cnt1000 IsSIGNAL s : INTEGER RANGE 0 TO 999;BEGINPROCESS (clk, clr)BEGINIF clr = '0’ THENs 〈= 0;ELSIF (clk'EVENT AND clk = '1’) THENIF en = '1' THENIF s<999 THENs <= s + 1;ELSE s<=0;END IF;ELSEs <= s;END IF;IF s = 999 THEN co 〈='1’;ELSE co <=’0';END IF;END IF;END PROCESS;count 〈= s;END a;摘要:根据教学实践, 介绍了VHDL 硬件描述语言进行工程设计的优点。

他既是一种与实际技术相独立的语言, 不束缚于某一特定的模拟程序或数字装置上,也不把设计方法强加于设计者,他允许设计者在其使用范围内选择工艺和方法,描述能力极强, 覆盖了逻辑设计的诸多领域和层次,并支持众多的硬件模型;也是一种在数字电路教学中全新的理论联系实际的教学方法和全新的培养学生实际动手能力的有效工具。

同时简要地说明VHDL 硬件描述语言的支撑软件M ax+ Plus.并结合实例详细阐明VHDL 语言在M ax+ Plus 软件的环境下对数字电路的设计、应用方法及使用时需注意的几个方面事项。

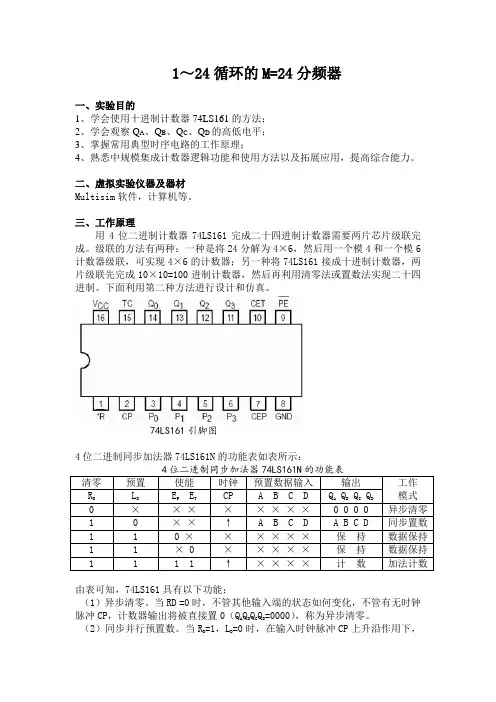

1~24循环的M=24分频器一、实验目的1、学会使用十进制计数器74LS161的方法;2、学会观察Q A 、Q B 、Q C 、Q D 的高低电平;3、掌握常用典型时序电路的工作原理;4、熟悉中规模集成计数器逻辑功能和使用方法以及拓展应用,提高综合能力。

二、虚拟实验仪器及器材 Multisim 软件,计算机等。

三、工作原理用4位二进制计数器74LS161完成二十四进制计数器需要两片芯片级联完成。

级联的方法有两种:一种是将24分解为4×6,然后用一个模4和一个模6计数器级联,可实现4×6的计数器;另一种将74LS161接成十进制计数器,两片级联先完成10×10=100进制计数器,然后再利用清零法或置数法实现二十四进制。

下面利用第二种方法进行设计和仿真。

74LS161引脚图4位二进制同步加法器74LS161N 的功能表如表所示:4位二进制同步加法器74LS161N 的功能表清零 预置 使能 时钟 预置数据输入 输出 工作 模式 R D L D E P E T CP A B C D Q A Q B Q C Q D 0 × × × × × × × × 0 0 0 0 异步清零 1 0 × × ↑ A B C D A B C D 同步置数 1 1 0 × × × × × × 保 持 数据保持 1 1 × 0 × × × × × 保 持 数据保持 1 11 1↑× × × ×计 数加法计数由表可知,74LS161具有以下功能:(1)异步清零。

当RD =0时,不管其他输入端的状态如何变化,不管有无时钟脉冲CP,计数器输出将被直接置0(QA QBQCQD=0000),称为异步清零。

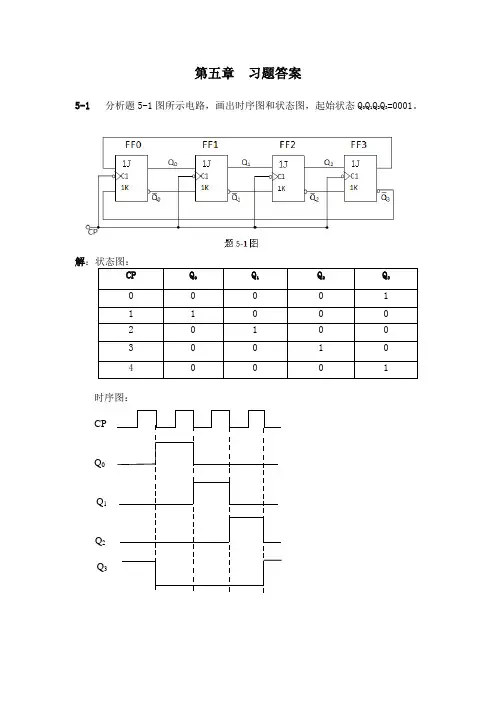

第五章习题答案5-1分析题5-1图所示电路,画出时序图和状态图,起始状态Q0Q1Q2Q3=0001。

解时序图:CPQ0Q1Q2Q35-2分析题5-2图所示电路,画出电路的状态图。

解5-3 JK触发器组成5-3图所示电路。

分析该电路为几进制计数器,并画出电路的状态图。

该电路为五进制计数器5-4JK触发器促成如图5-4图所示的电路。

(1)分析该电路为几进制计数器,画出状态图。

= 1,电路为几进制计数器,画出其状态图。

(2)若令K3解:(1为7进制计数器5-5 试画出题5-5图(a)所示电路中B,C端的波形。

输入端A,CP波形如题5-5图(b)所示,触发器的起始状态为零。

1 5 6 123456789 10 11 12 13 14 15 16 17 18 19CPAQ0Q1BC5-6分析题5-6图所示电路,画出电路的状态图,说明电路能否自启动。

该电路能够自启动5-7 分析题5-7图所示电路,画出电路的状态图,说明电路能否自启动。

由状态图可见,电路图能够自启动5-8画出题5-8图所示电路的状态图和时序图,简要说明电路的基本功能。

解:状态图:功能分析:根据状态图可知:电路为三位格雷码发生器。

5-9 画出题5-9图所示的状态图和时序图。

解:状态图:时序图:5-10 如题5-10图所示,FF0为下降沿触发的JK触发器,FF1为上升沿触发的D触发器,试对应给定的RD ,CP,J,K的波形,画出Q,Q1的波形。

5-11图所示。

解:电路图:态图如题5-12图所示。

解:电路图如下:5-13 试用下降沿触发的边沿型JK触发器和与非门,设计一个按自然态序进行的七进制同步加法计数器。

解:电路图:5-14 试用上升沿触发的边沿型D触发器和与非门,设计一个按自然态序进行计数的十进制同步加法计数器。

解:电路图:5-15 试用JK触发器设计一个同步十进制计数器,要实现的状态图如题5-15图所示。

解:电路图如下:5-16 试设计一个具有如题5-16图所示功能的计数器电路,图中M为控制变量。

EDA实验报告CNT9999计数器的设计指导老师:***班级:电技1503学号:***********姓名:***交通工程学院2017.10.15实验一0~9999的计数器电路的设计1.实验目的(1)进一步熟悉和掌握Quartus II软件的使用。

(2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的使用。

(3)学习和掌握VHDL进程语句和元件例化语句的使用。

2.实验内容设计并调试好一个计数范围为0~9999的4位十进制计数器电路CNT9999,并用GW48-CK或其他EDA实验开发系统进行硬件验证。

3实验条件(1)开发软件:Quartus II 13.0。

(2)实验设备:GW48-CK EDA 实验开发系统。

(3)拟用芯片:EP3C55F484C7。

4.实验设计1)系统原理框图为了简化设计并便于显示,本计数器电路CNT9999的设计分为两个层次,其中底层电路包括四个十进制计数器模块CNT10,再由这四个模块按照图1.1所示的原理图构成顶层电路CNT9999.图1.1 CNT9999电路原理图2)VHDL程序计数器CNT9999的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。

CNT10的VHDL源程序:--CNT10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA: IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO: OUT STD_LOGIC );END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA) ISBEGINIF CLR='1' THEN CQI<="0000";ELSIF CLK'EVENT AND CLK='1' THENIF ENA='1' THENIF CQI="1001" THEN CQI<="0000";ELSE CQI<=CQI+'1';END IF;END IF;END IF;END PROCESS;PROCESS(CQI) ISBEGINIF CLK'EVENT AND CLK='1' THENIF CQI<"1001" THEN CO<='0';ELSE CO<='1';END IF;END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;CNT9999的VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;--使用IEEE.STD_LOGIC_1164程序包PORT(CLR: IN STD_LOGIC;CLK: IN STD_LOGIC;CLK2:IN STD_LOGIC;ENA: IN STD_LOGIC;COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY DCNT9999;ARCHITECTURE ART OF DCNT9999 ISCOMPONENT CNT10 IS --CNT10元件定义语句PORT(CLK, CLR, ENA: IN STD_LOGIC;CQ: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO: OUT STD_LOGIC);END COMPONENT CNT10;COMPONENT CTRLS IS --元件定义语句PORT(CLK: IN STD_LOGIC;--端口说明语句(端口名:端口模式数据类型)SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT CTRLS;COMPONENT DISPLAY IS --元件定义语句PORT(SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);DATAIN: IN STD_LOGIC_VECTOR(15 DOWNTO 0);COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT DISPLAY;SIGNAL S0,S1,S2: STD_LOGIC; --信号的定义,定义了3个标准位的单值信号SIGNAL SEL: STD_LOGIC_VECTOR(2 DOWNTO 0);--定义1个标准位矢量的位矢量信号SEL,含有3个元素SIGNAL DOUT:STD_LOGIC_VECTOR(15 DOWNTO 0);--定义1个标准位矢量的位矢量信号DOUT,有16个数组元素BEGINU0: CNT10 PORT MAP(CLK,CLR, ENA, DOUT(3 DOWNTO 0), S0); --元件例化语句,位置关联的方式U1: CNT10 PORT MAP(S0, CLR, ENA, DOUT(7 DOWNTO 4), S1);U2: CNT10 PORT MAP(S1, CLR, ENA, DOUT(11 DOWNTO 8), S2);U3: CNT10 PORT MAP(S2, CLR, ENA, DOUT(15 DOWNTO 12));U4: CTRLS PORT MAP(CLK2,SEL);U5: DISPLAY PORT MAP(SEL(2 DOWNTO 0),DOUT(15 DOWNTO 0),COM(7 DOWNTO 0),SEG(7 DOWNTO 0));--位置关联方式END ARCHITECTURE ART;3)仿真波形设置本设计包括两个层次,因此先进行底层的十进制计数器CNT10的仿真,再进行顶层CNT9999的仿真。

长沙学院数电课程设计说明书题目三位十进制计数器系(部) 电子与通信工程系专业(班级) 光电信息工程专业一班姓名***学号**********指导教师***起止日期06.11-06.15010级光电信息工程专业课程设计任务书(课题)系(部):电子与通信工程系专业:光电信息工程长沙学院课程设计鉴定表目录一.课程设计的目的 (6)二.课程设计课题 (6)三.课程设计内容 (7)四、设计步骤: (7)五.设计要点: (7)六.设计原理: (8)1.部分器件介绍: (8)2.+5V直流电源工作原理: (13)3.三位十进制计数器工作原理: (13)七:电路仿真 (14)1.M ULTISIM仿真图 (14)2.P ROTEL原理图: (16)3.PCB板: (18)八:心得体会 (19)九:参考文献 (19)三位十进制计数器的设计摘要本次课程设计的课题是三位十进制计数器,就设计所选用的器材而言,主要用到了3个74LS192,3个CD4511,3个七段数码管,1个555芯片以及一些电阻和电容。

74LS192是双时钟方式的十进制可逆计数器,这使得设计本身简单了许多。

设计中采用555芯片制成一脉冲发生器,为电路提供连续脉冲。

CD4511是7段数码管译码器,将74LS192的输出信号译码成数码管可识别的信号。

然后Multisim仿真软件测试和分析电路性能,并用protel软件绘制原理图,设计pcb板,本次设计的计数器是三位十进制加计数器,由上升沿触发,通过CO输出与其他的芯片级联。

达到进位输出!另外,本设计要求自己设计一个直流+5v电源,故用到了LM7805,以及变压器和整流桥堆!关键词:三位十进制计数器,74LS192芯片,555芯片,脉冲发生器,加计数器,上升沿触发,+5v直流电源,Multisim仿真,Protel原理图,PCB板。

一.课程设计的目的1.激发学生的学习热情,最大限度的发挥学生的潜能。

2.对所学过的知识进行强化加深,了解设计一般数电产品的基本程序,方法及过程。

任意进制计数器置零法

任意进制计数器置零法是指将一个任意进制的计数器初始化为0的方法。

在十进制中,将一个计数器初始化为0的方法非常简单,只需要将计数器的值赋为0即可。

但在其他进制中,需要使用置零法实现。

假设我们有一个n进制的计数器,n为任意正整数。

计数器有若干个位,每一位的取值范围为0到(n-1)。

我们可以将计数器每一位的值依次置为0,从低位到高位。

具体步骤如下:

1. 初始化一个空列表result,用于存储计数器每一位的值。

2. 初始化一个变量count为0,用于记录计数器的位数。

3. 循环计数器的每一位,从低位向高位依次进行以下操作:

- 将当前位的值置为0。

- 将当前位的值添加到result列表中。

- count加1。

4. 返回result列表作为初始化后的计数器值。

例如,我们有一个二进制的计数器,包含3位。

我们可以使用置零法将其初始化为0,具体步骤如下:

1. 初始化result为一个空列表。

2. 初始化count为0。

3. 从低位到高位依次进行以下操作:

- 将当前位的值置为0。

- 将当前位的值添加到result列表中。

- count加1。

4. 返回result列表,即为初始化后的计数器值。

在本例中,返回的结果为[0, 0, 0]。

通过置零法,我们可以将任意进制的计数器初始化为0,使得计数器可以从0开始计数。

十进制计数器CD4553/CC4553/MC14553中文资料

十进制计数器CD4553/CC4553/MC14553中文资料

CD4553/CC4553是3位十进制计数器,但只有1个输出端,要完成3位输出,采用扫描输出方式,通过它的选通脉冲信号,依次控制3位十进制的输出,从而实现扫描显示方式。

CD4553/CC4553引脚功能:

CLOCK:计数脉冲输入端,下调沿有效。

CIA、CIB:内部振荡器的外界电容端子。

MR:计数器清零(只清计数器部分),高电平有效。

LE:锁定允许。

当该端为低电平时,3组计数器的内容分别进入3组锁存器,当该端为高电平时,锁存器锁定,计数器的值不能进入。

DIS:该端接地时,计数脉冲才能进行计数。

DS1、DS2、DS3:位选通扫描信号的输出,这3端能循环地输出低电平,供显示器作为位通控制。

Q0、Q1、Q2、Q3:BCD码输出端,它能分时轮流输出3组锁存器的BCD码。

CD4553内部虽然有3组BCD码计数器(计数最大值为999),但BCD的输出端却只有一组Q0~Q3通过内部的多路转换开关能分时输出个、十、百位的BCD码,相应地,也输出3位位选通信号。

例如:当Q0~Q3输出个位的BCD码时,DS1端输出低电平;当Q0~Q3输出十位的BCD码时,DS2端输出低电平;当Q0~Q3输出百位的BCD码时,DS3端输出低电平时,周而复始、循环不止。

图1 CD4553引脚图。

现代电子设计实验报告实验名称:3位十进制循环计数器的设计系(科):信息科学与技术系班级:学号:姓名:完成时间:2012年4月24日. 1 .一、实验内容(一)设计要求1.设计一个3位十进制循环计数器,从0加到999,再恢复到0,循环往复。

每秒计数器加1。

2.有复位功能,当复位端reset为高时,计数器清零,停止计数。

3.可以控制计数的开始start和停止stop。

当计数开始start信号有效时,计数器开始计数;当计数停止stop信号有效时,计数停止;当start信号再次有效时,继续计数。

4.计数器的计数值采用动态显示方式在数码管上显示出来。

5.进行设计,仿真并下载程序到实验箱的CPLD模块板进行验证。

(二)电路模块cyclecntsysclk reset startSE G[6. SCAN[7.★提示:reset信号可以使用拨动开关来产生。

start和stop信号使用按键来实现输入信号:sysclk:基准时钟,50MHz;reset:异步复位信号,高有效;start,stop:计数开始和计数停止信号输入;. 2 .输出信号:SEG[6..0]:段码信号输出。

SCAN[7..0]:位码信号输出。

二、实验原理此系统的核心为一个三位循环计数器,将此计数器的输出结果通过分位电路动态显示到三个数码管上面。

另外的辅助电路分别为四个不同频率的分频器和按键去抖电路。

三、设计方案四、原理图. 3 .. 4 .五、模块设计(一)分频电路1.设计原理分频器就是对较高频率的信号进行分频,得到较低频率的信号。

定义一个计数器对输入时钟进行计数,在计数的前一半时间里,输出高电平,在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

例如,6分频,计数值为0~2输出高电平,计数值为3~5输出低电平。

2.VHDL程序代码输出为1HZ分频电路N=50MHZ/1HZ=50000000Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv1 isgeneric(N: integer:=50000000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv1;Architecture a of fdiv1 is. 5 .signal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为10HZ分频电路N=50MHZ/10HZ=5000000. 6 .Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=5000000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 issignal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;. 7 .process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为200HZ分频电路N=50MHZ/200HZ=250000Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=250000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 is. 8 .signal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为1000HZ分频电路N=50MHZ/1000HZ=50000Library ieee;. 9 .Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=50000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 issignal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平. 10 .beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;(二)扫描电路1.设计原理当reset和stop信号起作用时,输出到计数器的信号为低电平,只有当start 和脉冲信号起作用时,输出才为高。

2.VHDL程序代码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity saomiao isport (clk: in std_logic;reset: in std_logic;start,stop: in std_logic;seg: out std_logic);end saomiao;architecture behave of saomiao isbeginprocess(start,stop,reset,clk)beginif(reset = '1') thenseg <='0';elsif(clk'event and clk = '1') thenif(start='0') thenseg <= '1';elsif(stop='0') thenseg <= '0';end if;end if;end process;end behave;(三)计数器电路1.设计原理复位信号起作用时,输出数值为0,时钟信号为上升沿且为有效的计数状态时(计数器的输入seg值为高电平),加一循环计数。

2.VHDL程序代码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity count isport(reset: in std_logic;seg: in std_logic;clk1000: in std_logic;q: out integer range 0 to 999);end count;architecture a of count isbeginprocess (clk1000,reset,seg)variable temp:integer range 0 to 999;beginif (reset = '1') thentemp :=0;elsif(clk1000'event and clk1000 = '1') thenif(seg= '0') thentemp := temp;elseif(temp=999) thentemp := 0;elsetemp := temp + 1;end if;end if;end if;q <= temp;end process;end a;(四)分位电路1.设计原理对输入的一个三位数进行分位处理,取出他的个位、十位和白位。