实验一四位串行进位加法器的设计实验报告

- 格式:doc

- 大小:162.50 KB

- 文档页数:7

EDA实验报告一.实验任务设计四位串行进位加法器,并以此为基础设计输入输出带寄存器的四位加法电路二.实验内容(一)设计思路1.输入a,b两个四位二进制数,输入进位cin为一位二进制数,输出s为四位二进制数,输出进位cout为一位二进制数。

2.A,b,s,cout的每一位需用d触发器锁存,那么一共需要13个d触发器。

(二)。

源程序和电路图1.d触发器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DFF1 ISPORT (CLK,D:IN STD_LOGIC;Q:OUT STD_LOGIC );END;ARCHITECTURE bhv OF DFF1 ISSIGNAL Q1 : STD_LOGIC;BEGINPROCESS(CLK,Q1)BEGINIF CLK'EVENT AND CLK ='1'THEN Q1<=D;END IF;END PROCESS;Q<=Q1;END bhv;2.一位二进制进位加法器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_adder ISPORT (a,b,c0:IN STD_LOGIC;s,c1:OUT STD_LOGIC);END ENTITY f_adder;ARCHITECTURE one OF f_adder ISSIGNAL abc:STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL ain,bin,c0in:STD_LOGIC;BEGINain<=a;bin<=b;c0in<=c0;abc<=ain&bin&c0in;PROCESS(abc)BEGINCASE abc ISWHEN"000"=>s<='0';c1<='0';WHEN"001"=>s<='1';c1<='0';WHEN"010"=>s<='1';c1<='1';WHEN"011"=>s<='0';c1<='0';WHEN"100"=>s<='1';c1<='0';WHEN"101"=>s<='0';c1<='1';WHEN"110"=>s<='0';c1<='1';WHEN"111"=>s<='1';c1<='1';WHEN OTHERS =>NULL;END CASE;END PROCESS;END ARCHITECTURE one;3.四位二进制加法计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_4adder ISPORT(A,B:IN STD_LOGIC_VECTOR(3 DOWNTO 0); S:OUT STD_LOGIC_VECTOR(3DOWNTO 0); cin:IN STD_LOGIC;cout:OUT STD_LOGIC);END ENTITY;ARCHITECTURE one OF f_4adder IS COMPONENT f_adderPORT(a,b,c0:IN STD_LOGIC ;c1,s:OUT STD_LOGIC);END COMPONENT ;SIGNAL c2,c3,c4:STD_LOGIC;BEGIN u1:f_adder PORT MAP (a=>A(0),b=>B(0),c0=>cin,c1=>c2,s=>S(0));u2:f_adder PORT MAP (a=>A(1),b=>B(1),c0=>c2,c1=>c3,s=>S(1));u3:f_adder PORT MAP (a=>A(2),b=>B(2),c0=>c3,c1=>c4,s=>S(2));u4:f_adder PORT MAP (a=>A(3),b=>B(3),c0=>c4,c1=>cout,s=>S(3)); END ARCHITECTURE one;4.带寄存器的四位二进制加法器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY h_4adder ISPORT(A,B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);S:OUT STD_LOGIC_VECTOR(3DOWNTO 0);cin:IN STD_LOGIC;cout:OUT STD_LOGIC;SHIZHONG:IN STD_LOGIC);END ENTITY;ARCHITECTURE one OF h_4adder ISCOMPONENT f_adderPORT(a,b,c0:IN STD_LOGIC ;c1,s:OUT STD_LOGIC);END COMPONENT ;COMPONENT DFF1PORT(CLK,D:IN STD_LOGIC;Q:OUT STD_LOGIC);END COMPONENT ;SIGNAL g,h,f:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL e,c1,c2,c3,c4 : STD_LOGIC;BEGINu1:f_adder PORT MAP (a=>A(0),b=>B(0),c0=>cin,c1=>c2,s=>f(0));u2:f_adder PORT MAP (a=>A(1),b=>B(1),c0=>c2,c1=>c3,s=>f(1));u3:f_adder PORT MAP (a=>A(2),b=>B(2),c0=>c3,c1=>c4,s=>f(2));u4:f_adder PORT MAP (a=>A(3),b=>B(3),c0=>c4,c1=>e,s=>f(3));u5: DFF1 PORT MAP (D=>A(0),Q=>g(0),CLK=>SHIZHONG);u6:DFF1 PORT MAP (D=>A(1),Q=>g(1),CLK=>SHIZHONG);u7:DFF1 PORT MAP (D=>A(2),Q=>g(2),CLK=>SHIZHONG);u8:DFF1 PORT MAP (D=>A(3),Q=>g(3),CLK=>SHIZHONG);u9:DFF1 PORT MAP (D=>B(0),Q=>h(0),CLK=>SHIZHONG);u10:DFF1 PORT MAP (D=>B(1),Q=>h(1),CLK=>SHIZHONG);u11:DFF1 PORT MAP (D=>B(2),Q=>h(2),CLK=>SHIZHONG);u12:DFF1 PORT MAP (D=>B(3),Q=>h(3),CLK=>SHIZHONG);U13:DFF1 PORT MAP (D=>f(0),Q=>S(0),CLK=>SHIZHONG);u14: DFF1 PORT MAP (D=>f(1),Q=>S(1),CLK=>SHIZHONG);u15:DFF1 PORT MAP (D=>f(2),Q=>S(2),CLK=>SHIZHONG);u16:DFF1 PORT MAP (D=>f(3),Q=>S(3),CLK=>SHIZHONG);u17:DFF1 PORT MAP (D=>e,Q=>cout,CLK=>SHIZHONG); END ARCHITECTURE one;(三)时序仿真波形图。

四位串行进位加法器设计集成电路CAD课程设计报告四位串行加法器设计1串行进位加法器简介1.1加法器实现多为二进制数相加的电路,称为加法器。

根据进位方式不同,有串行进位加法器和超前进位加法器之分。

采用串行进位方式,优点是电路简单,连接方便;缺点是运算速度不高。

原理:把四个全加器(例如两片74LS183)依次级联起来,便可构成四位串行进位加法器。

因此四位串行进位加法器的设计可以分以下两步进行:(1)全加器设计;(2)将全加器级联,构成四位串行进位加法器(a)(b)图(1)四位串行加法器74831.2 图2为四位串行加法器7483逻辑图图(2)四位串行加法器2 四位串行进位加法器的设计实现:2.1 输出级电路设计与TTL电路兼容驱动10个TTL①输出高电平时|IoH|<=20uAV oHmin=4.4V②输出低点平时|IoH|<=20mAV oHmax=0.4V③输出级充放电时间tr=tf计算电路如图3所示①以15个PF的电容负载代替10个TTL电路来计算tr、tf②输入V为的前一级的输出被认为是理想的输出,即:ViL=Vss,ViH=Vdd③计算电流时,负载为电流负载,有拉电流的灌电流。

图3(1)CMOS N 管(W/L )N 的计算:当输入为高电平时(Vi=Vdd ),N 管导通后级TTL 电路有较大的灌电流输入,此时(表示成对称形式)使方括号中的值和栅电容Cox 及电子迁移率un 为最小值:o u t00f f[]200200)()(2V V V V V V C L W I tn i s tn oxN ndsn -----?=μm ax0m in 2ox SiOox t C εε=230m ax0m in-=TT n n μμ(2) CMOS P 管(W/P )p 的计算|IoH |<=20uA时有 V oHmin=4.4V tr=tf① 以Ioh<=20uA时V oHmin=4.4V 的条件计算最坏的情况下Vdd=4.5V ,V ohmin=4.4v,Vtp=0.8V ,经计算可得===?233034956.164m inn L W []202)()(2oh tp i dd tp i oxp p ohV V V V V V C L W I -----??? ??=μm ax 0m in 2ox SiOox t C εε=230m ax 0m in-=T T n p μμ??=== 21532227.7pL W②tr=tp 的条件计算:CMOS 中αp=αn所以2.2 输入级设计ddtp p V V =αddtn n V V =αddp L p V k C =τ()-???? ??--+--=p n n n n f arth t αααατ111.011)1.0(2 p pn n pn n p f r LW L W k k t t μμττ===?===233034956.164minn L W ??==275931138minn L W ??===?233034956.164minn L W输入电平Vih 可能为2.4V(1)拉管P2为了节省面积,同时又能使Vih 较快上升,取图4(2)CMOS 反向器的P1管此P1管应取内部基本反向器的尺寸(3)CMOS 反相器的N 管TTL 的输出电平在0.4-2.4之间 V1*=ViLmax+Vihmin=1.4V===?223312p L W==?231.546内p L W式中βk=kn/kp,Vdd=5V ,Vtn=0.7V ,Vi*=1.4V , βk=17.162.3 内部基本反相器中各MOS 管尺寸的计算内部反相器的负载电容:①本级漏极的PN 结电容Cpn ②下级的栅电容Cc1 ③连线杂散电容Cs Cpn+Cc1=10CsCs :铝线宽5um,长100um ,在场区上面,此铝线的电容为1K k V V k V p n TP DD p *I+++=+++=R TP DD TN R TN N V V V V k ββ)(??==??? ??2230W np R pl nl L L W μμβ??==22303345nlL W ??==?231.546plL W ??===?223312p L WCpn 和Cl :N 管其衬底是P 型,所以 NB=2?1016 cm-3 设结深Xi=0.5um R □=20Ω/□对于P 管Cpn=而CC1可以由:Cc1=10Cs-Cpn 求出。

试验一 4位全加器实验1.实验原理.实验原理全加器能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位信号。

该位的进位信号。

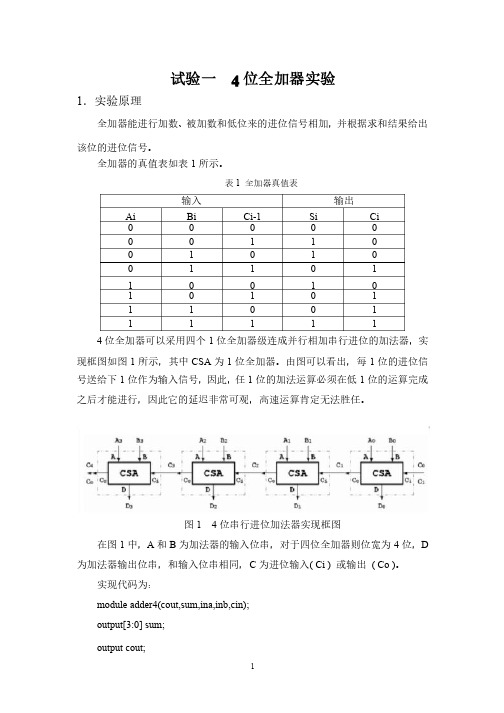

全加器的真值表如表1所示。

所示。

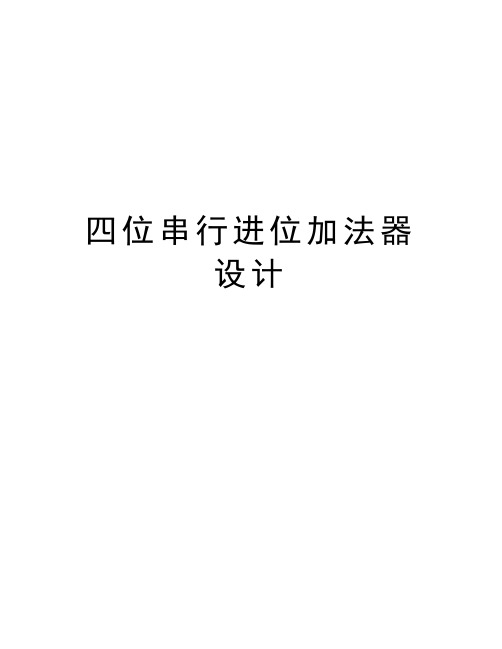

表1 全加器真值表全加器真值表输入输入输出输出AiBi Ci-1 Si Ci0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 111114位全加器可以采用四个1位全加器级连成并行相加串行进位的加法器,位全加器级连成并行相加串行进位的加法器,实实现框图如图1所示,其中CSA 为1位全加器。

由图可以看出,每1位的进位信号送给下1位作为输入信号,因此,任1位的加法运算必须在低1位的运算完成之后才能进行,因此它的延迟非常可观,高速运算肯定无法胜任。

之后才能进行,因此它的延迟非常可观,高速运算肯定无法胜任。

图1 4位串行进位加法器实现框图位串行进位加法器实现框图在图1中,A 和B 为加法器的输入位串,对于四位全加器则位宽为4位,D 为加法器输出位串,和输入位串相同,C 为进位输入( Ci ) 或输出或输出( Co )。

实现代码为:实现代码为:module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout;input[3:0] ina,inb; input cin;assign {cout,sum}=ina+inb+cin; endmodule2.实验目的.实验目的⒈熟悉⒈熟悉 ISE9.1 开发环境,掌握工程的生成方法;开发环境,掌握工程的生成方法; ⒉了解⒉了解 V erilog HDL 语言在语言在 FPGA 中的使用;中的使用; ⒊了解4位全加器的V erilog HDL 语言实现。

语言实现。

3.实验内容.实验内容⒈用V erilog HDL 语言设计4位全加器,进行功能仿真验证。

硬件描述语言实验题目:四位全加器学院数学与计算机学院学科门类xxxxxxxxxx专业xxxxxxxxxx学号姓名x指导教师xxxx20xx年x 月xx日1、实验目的:练习VHDL语言设计工程的建立与仿真的步骤和方法、熟悉VHDL语言行为描述的编写方法。

2、实验环境:PC个人计算机、Windows XP操作系统、Quartus II集成开发环境软件。

3、实验要求:设计一个四位加法器,其引脚及其功能如下表。

4、实验步骤:(1)用RTL描述方式描述4位加法器①RTL描述方式是一种明确规定寄存器描述的方法,它要求在描述时要么采用寄存器硬件的一一对应的直接描述,要么采用寄存器之间的功能描述。

RTL描述方式可以进行逻辑综合,这是其他描述方式所不具备的特点。

②编辑代码这种描述方法详细描述了加法器的计算过程,即写出了每一位的计算和进位方法。

模块内部(构造体说明部分)需要定义三个连接线,定义语句为:signal c0,c1,c2 : std_logic代码如下:library ieee;use ieee.std_logic_1164.all;entity adder4 isport(a,b:in std_logic_vector(3 downto 0);ci:in std_logic;s:out std_logic_vector(3 downto 0);co:out std_logic);end entity;architecture rtl of adder4 issignal c0,c1,c2:std_logic;s(0) <= a (0) xor b(0) xor ci;c0<= (a(0) and b(0)) or (a(0) and ci) or (b(0) and ci);s(1) <= a (1) xor b(1) xor c0;c1<= (a(1) and b(1)) or (a(1) and c0) or (b(1) and c0);s(2) <= a (2) xor b(2) xor c1;c2<= (a(2) and b(2)) or (a(2) and c1) or (b(2) and c1);s(3) <= a (3) xor b(3) xor c2;co<= (a(3) and b(3)) or (a(3) and c2) or (b(3) and c2);end architecture rtl;③仿真结果(2)用行为描述方式描述4位加法器①行为描述是对系统数学模型的描述,其抽象程度比寄存器传输描述方式和结构描述方式更高。

四位串行进位加法器设计集成电路CAD课程设计报告四位串行加法器设计1串行进位加法器简介1.1加法器实现多为二进制数相加的电路,称为加法器。

根据进位方式不同,有串行进位加法器和超前进位加法器之分。

采用串行进位方式,优点是电路简单,连接方便;缺点是运算速度不高。

原理:把四个全加器(例如两片74LS183)依次级联起来,便可构成四位串行进位加法器。

因此四位串行进位加法器的设计可以分以下两步进行:(1)全加器设计;(2)将全加器级联,构成四位串行进位加法器(a)(b)图(1)四位串行加法器74831.2 图2为四位串行加法器7483逻辑图图(2)四位串行加法器2 四位串行进位加法器的设计实现:2.1 输出级电路设计与TTL电路兼容驱动10个TTL①输出高电平时|IoH|<=20uA VoHmin=4.4V②输出低点平时|IoH|<=20mA VoHmax=0.4V③输出级充放电时间tr=tf计算电路如图3所示①以15个PF 的电容负载代替10个TTL 电路来计算tr 、tf ②输入V 为的前一级的输出被认为是理想的输出,即:ViL=Vss,ViH=Vdd③计算电流时,负载为电流负载,有拉电流的灌电流。

图3(1)CMOS N 管(W/L )N 的计算:当输入为高电平时(Vi=Vdd ),N 管导通后级TTL 电路有较大的灌电流输入,此时(表示成对称形式)使方括号中的值和栅电容Cox 及电子迁移率un 为最小值:o u t00f f[]200200)()(2V V V V V V C L W I tn i s tn ox N n dsn -----⎪⎭⎫ ⎝⎛=μm ax0m in 2ox SiO ox t C εε=(2) CMOS P 管(W/P )p 的计算|IoH |<=20uA时有 VoHmin=4.4Vtr=tf① 以Ioh<=20uA时VoHmin=4.4V 的条件计算最坏的情况下Vdd=4.5V,Vohmin=4.4v,Vtp=0.8V,230m ax 0m in -⎪⎪⎭⎫ ⎝⎛=T T n n μμ∆∆===⎪⎭⎫ ⎝⎛233034956.164m in n L W []202)()(2oh tp i dd tp i ox p p oh V V V V V V C L W I -----⎪⎭⎫ ⎝⎛=μm ax 0m in 2ox SiO ox t C εε=230m ax 0m in -⎪⎪⎭⎫ ⎝⎛=T T n p μμ经计算可得②tr=tp 的条件计算:CMOS 中αp=αn所以 ∆∆===⎪⎭⎫ ⎝⎛21532227.7pL W dd tp p V V =αddtn n V V =αdd p L p V k C =τ()⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎣⎡-⎪⎪⎭⎫ ⎝⎛--+--=p n n n n f arth t αααατ111.011)1.0(2p p n n p n n p f r L W L W k k t tμμττ⎪⎭⎫ ⎝⎛⎪⎭⎫ ⎝⎛===⎪⎪⎭⎫ ⎝⎛∆∆===⎪⎭⎫ ⎝⎛233034956.164minn L W ∆∆==⎪⎭⎫ ⎝⎛275931138minn L W2.2 输入级设计输入电平Vih 可能为2.4V(1)拉管P2为了节省面积,同时又能使Vih 较快上升,取图4(2)CMOS 反向器的P1管此P1管应取内部基本反向器的尺寸∆===⎪⎭ ⎝236.164minn L ∆∆===⎪⎭⎫ ⎝⎛223312p L W∆∆==⎪⎭⎫ ⎝⎛231.546内p L W(3)CMOS 反相器的N 管TTL 的输出电平在0.4-2.4之间V1*=ViLmax+Vihmin=1.4V式中βk=kn/kp,Vdd=5V,Vtn=0.7V,Vi*=1.4V, βk=17.162.3 内部基本反相器中各MOS 管尺寸的计算 内部反相器的负载电容:①本级漏极的PN 结电容Cpn1K k V V k V p n TP DD p *I+++=+++=R TP DD TN R TN N V V V V k ββ)(∆∆=⎪⎭⎫ ⎝⎛=⎪⎭⎫ ⎝⎛2230W n p R plnl L L W μμβ∆∆==⎪⎭⎫ ⎝⎛22303345nl L W ∆∆==⎪⎭⎫ ⎝⎛231.546plL W ∆∆===⎪⎭⎫ ⎝⎛223312p L W②下级的栅电容Cc1③连线杂散电容CsCpn+Cc1=10CsCs :铝线宽5um,长100um ,在场区上面,此铝线的电容为Cpn 和Cl :N 管 其衬底是P 型,所以 NB=2⨯1016 cm-3设结深Xi=0.5um R □=20Ω/□对于P 管Cpn= )(10726.1100.19.31085.8101005C 14482014F t A s oxF SiO Al ---⨯=⨯⨯⨯⨯⨯⨯==-εεϕεε2021021C C p jn n jp Si qN C jpn ===++2l n iB n N N q k T =ϕ318õ10862.7R 1N -⨯==cm x q j μ28/10195.2cm F C p jN -+⨯=28/101396.1cm F C N jP -+⨯=Cp n Cn p+++而CC1可以由:Cc1=10Cs-Cpn求出。

集成电路CAD课程设计报告四位串行加法器设计1串行进位加法器简介1.1加法器实现多为二进制数相加的电路,称为加法器。

根据进位方式不同,有串行进位加法器和超前进位加法器之分。

采用串行进位方式,优点是电路简单,连接方便;缺点是运算速度不高。

原理:把四个全加器(例如两片74LS183)依次级联起来,便可构成四位串行进位加法器。

因此四位串行进位加法器的设计可以分以下两步进行:(1)全加器设计;(2)将全加器级联,构成四位串行进位加法器(a)(b)图(1)四位串行加法器74831.2 图2为四位串行加法器7483逻辑图图(2)四位串行加法器2 四位串行进位加法器的设计实现:2.1 输出级电路设计与TTL电路兼容驱动10个TTL①输出高电平时|IoH|<=20uAV oHmin=4.4V②输出低点平时|IoH|<=20mAV oHmax=0.4V③输出级充放电时间tr=tf计算电路如图3所示①以15个PF的电容负载代替10个TTL电路来计算tr、tf②输入V为的前一级的输出被认为是理想的输出,即:ViL=Vss,ViH=Vdd③计算电流时,负载为电流负载,有拉电流的灌电流。

图3(1)CMOS N 管(W/L )N 的计算:当输入为高电平时(Vi=Vdd ),N 管导通后级TTL 电路有较大的灌电流输入,此时(表示成对称形式)使方括号中的值和栅电容Cox 及电子迁移率un 为最小值:o u t00f f[]200200)()(2V V V V V V C L W I tn i s tn oxN ndsn -----⎪⎭⎫ ⎝⎛=μm ax0m in 2ox SiOox t C εε=230m ax0m in-⎪⎪⎭⎫⎝⎛=TT n n μμ(2) CMOS P 管(W/P )p 的计算|IoH |<=20uA时有 V oHmin=4.4V tr=tf① 以Ioh<=20uA时V oHmin=4.4V 的条件计算最坏的情况下Vdd=4.5V ,V ohmin=4.4v,Vtp=0.8V ,经计算可得∆∆===⎪⎭⎫⎝⎛233034956.164m inn L W []202)()(2oh tp i dd tp i oxp p ohV V V V V V C L W I -----⎪⎭⎫ ⎝⎛=μm ax0m in 2ox SiOox t C εε=230m ax 0m in-⎪⎪⎭⎫⎝⎛=T T n p μμ∆∆===⎪⎭⎫⎝⎛21532227.7pL W②tr=tp 的条件计算:CMOS 中αp=αn所以2.2 输入级设计ddtp p V V =αddtn n V V =αddp L p V k C =τ()⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎣⎡-⎪⎪⎭⎫ ⎝⎛--+--=p n n n n f arth t αααατ111.011)1.0(2p pn n pn n p f r LW L W k k t t μμττ⎪⎭⎫⎝⎛⎪⎭⎫⎝⎛===⎪⎪⎭⎫ ⎝⎛∆∆===⎪⎭⎫⎝⎛233034956.164minn L W ∆∆==⎪⎭⎫⎝⎛275931138minn L W ∆∆===⎪⎭⎫⎝⎛233034956.164minn L W输入电平Vih 可能为2.4V(1)拉管P2为了节省面积,同时又能使Vih 较快上升,取图4(2)CMOS 反向器的P1管此P1管应取内部基本反向器的尺寸(3)CMOS 反相器的N 管TTL 的输出电平在0.4-2.4之间 V1*=ViLmax+Vihmin=1.4V∆∆===⎪⎭⎫⎝⎛223312p L W∆∆==⎪⎭⎫ ⎝⎛231.546内p L W式中βk=kn/kp,Vdd=5V ,Vtn=0.7V ,Vi*=1.4V , βk=17.162.3 内部基本反相器中各MOS 管尺寸的计算内部反相器的负载电容: ①本级漏极的PN 结电容Cpn ②下级的栅电容Cc1 ③连线杂散电容Cs Cpn+Cc1=10CsCs :铝线宽5um,长100um ,在场区上面,此铝线的电容为1K k V V k V p n TP DD p *I+++=+++=R TP DD TN R TN N V V V V k ββ)(∆∆=⎪⎭⎫⎝⎛=⎪⎭⎫ ⎝⎛2230W np R pl nl L L W μμβ∆∆==⎪⎭⎫⎝⎛22303345nlL W ∆∆==⎪⎭⎫⎝⎛231.546plL W ∆∆===⎪⎭⎫⎝⎛223312p L WCpn 和Cl :N 管 其衬底是P 型,所以 NB=2⨯1016 cm-3 设结深Xi=0.5um R □=20Ω/□对于P 管Cpn=而CC1可以由:Cc1=10Cs-Cpn 求出。

eda四位全加器实验报告EDA实验报告(四位全加器的实现)实验一四位全加器的实现一、实验目的1、掌握Quartus9.0图形编辑输入法2、掌握Quartus环境下文件的编译、仿真及下载方法3、了解VHDL语言的设计流程4、掌握quartus环境下VHDL的使用方法二、实验内容1、用图形/原理图法实现4位全加器。

2、用VHDL语言实现4位全加器,必须使用元件例化。

3、仿真并通过。

3、下载到实验板,并验收三、实验步骤1、图形编辑发设计4位加法器(1)新建图形文件,设计一位全加器,逻辑电路图如下图(图1-1)所示。

图1-1(2)将设计好的一位全加器进行例化,操作为file?Create/Update?Create symbol files for currentfile,完成此操作后会在元器件符号表里找到刚刚做好的一位全加器。

(3)再新建一个图形文件,用四个已经做好的一位全加器级联成一个四位全加器,其逻辑原理图如图1-2所示。

编辑好后保存文件,在文件列表里找到该文件,右键?Set as Top-level Entity,将其设置为顶层文件,点击编译按钮就行编译。

1图1-2(4)新建波形文件,赋予每个输入端口某种输入信号,保存波形文件,进行功能仿真,观察输出端波形与输入信号关系是否正确。

若不正确,查找问题所在并解决问题;若正确,则进行管脚分配,分配完毕后再编译一次使分配生效,连接DE2开发板到电脑,将文件下载到开发板进行验证。

2、用VHDL语言设计4位加法器(1)新建一个VHDL源文件,文件名为adder1.vhd,使用VHDL 实现一位全加器,其VHDL代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY adde1r ISPORT(A,B,Ci:IN STD_LOGIC;S,Co:OUT STD_LOGIC);END adder1;ARCHITECTURE qadder OF adder1 ISBEGINPROCESS(A,B,Ci)VARIABLE n1,n2,n3:STD_LOGIC;BEGINn1:=A AND B;n2:=A XOR B;2n3:=Ci AND n2;Co=n3 OR n1;S=n2 XOR Ci;END PROCESS;END qadder;(2)再新建一个VHDL源文件,命名为adder4.vhd,在这里将adder一位全加器例化并使用它,做成四位全加器,代码如下:library ieee;use ieee.std_logic_1164.all;entity adder4 isport(A,B:in std_logic_vector(3 downto 0); S:out std_logic_vector(3 downto 0);Co:out std_logic;Ci:in std_logic);end adder4;architecture adder_4 of adder4 iscomponent adderport(A:in std_logic;B:in std_logic;Ci:in std_logic;Co:out std_logic;S:out std_logic);end component;signal c1,c2,c3:std_logic;beginu1:adder port map(A(0),B(0),Ci,c1,S(0)); u2:adder port map(A(1),B(1),c1,c2,S(1)); u3:adder port map(A(2),B(2),c2,c3,S(2)); u4:adder port map(A(3),B(3),c3,Co,S(3)); end adder_4;(3)保存文件后将adder4设置为顶层文件并编译,编译通过后按照与图形编辑发一样的仿真、管脚分配方式进行操作,最后下载到开发板验证四、实验现象两种方式实现的四位加法器下载到DE2开发板后都可正常工作,其中使用SW0作为低位的进位,SW4~1作为数据B,SW8~5作为数据A,LDG3~0作为输出的结果,LEDG4作为输出的进位。

实验一利用原理图输入法设计4位全加器一、实验目的:掌握利用原理图输入法设计简单组合电路的方法,掌握MAX+plusII的层次化设计方法。

通过一个4位全加器的设计,熟悉用EDA软件进行电路设计的详细流程。

二、实验原理:一个4位全加器可以由4个一位全加器构成,全加器的进位以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的低位进位输入信号cin相接。

1位全加器f-adder由2个半加器h-adder和一个或门按照下列电路来实现。

半加器h-adder由与门、同或门和非门构成。

四位加法器由4个全加器构成1234三、实验内容:1. 熟悉QuartusII软件界面,掌握利用原理图进行电路模块设计的方法。

QuartusII设计流程见教材第五章:QuartusII应用向导。

2.设计1位全加器原理图(1)生成一个新的图形文件(file->new->graphic editor)(2)按照给定的原理图输入逻辑门(symbol->enter symbol)(3)根据原理图连接所有逻辑门的端口,并添加输入/输出端口(4)为管脚和节点命名:在管脚上的PIN_NAME处双击鼠标左键,然后输入名字;选中需命名的线,然后输入名字。

(5)创建缺省(Default)符号:在File菜单中选择Create Symbol Files for Current File项,即可创建一个设计的符号,该符号可被高层设计调用。

3.利用层次化原理图方法设计4位全加器(1)生成新的空白原理图,作为4位全加器设计输入(2)利用已经生成的1位全加器的缺省符号作为电路单元,设计4位全加器的原理图.4.新建波形文件(file->new->Other Files->Vector Waveform File),保存后进行仿真(Processing ->Start Simulation),对4位全加器进行时序仿真。

EDA实验报告(四选一、四位比较器、加法器、计数器、巴克码发生器)EDA实验报告实验14选1数据选择器的设计一、实验目的1.学习EDA软件的基本操作。

2.学习使用原理图进行设计输入。

3.初步掌握器件设计输入、编译、仿真和编程的过程。

4.学习实验开发系统的使用方法。

二、实验仪器与器材1.EDA开发软件一套2.微机一台3.实验开发系统一台4.打印机一台三、实验说明本实验通过使用基本门电路完成4选1数据选择器的设计,初步掌握EDA设计方法中的设计输入、编译、综合、仿真和编程的过程。

实验结果可通过实验开发系统验证,在实验开发系统上选择高、低电平开关作为输入,选择发光二极管显示输出电平值。

本实验使用Quartus II 软件作为设计工具,要求熟悉Quartus II 软件的使用环境和基本操作,如设计输入、编译和适配的过程等。

实验中的设计文件要求用原理图方法输入,实验时,注意原理图编辑器的使用方法。

例如,元件、连线、网络名的放置方法和放大、缩小、存盘、退出等命令的使用。

学会管脚锁定以及编程下载的方法等。

四、实验要求1.完成4选1数据选择器的原理图输入并进行编译;2.对设计的电路进行仿真验证;3.编程下载并在实验开发系统上验证设计结果。

五、实验结果4选1数据选择器的原理图:仿真波形图:管脚分配:实验2 四位比较器一、实验目的1.设计四位二进制码比较器,并在实验开发系统上验证。

2.学习层次化设计方法。

二、实验仪器与器材1.EDA 开发软件 一套 2.微机 一台 3.实验开发系统 一台 4.打印机 一台 5.其它器件与材料 若干 三、实验说明本实验实现两个4位二进制码的比较器,输入为两个4位二进制码0123A A A A 和0123B B B B ,输出为M(A=B ),G (A>B )和L (A<B )(如图所示)。

用高低电平开关作为输入,发光二极管作为输出,具体管脚安排可根据试验系统的实际情况自行定义。

![实验一四位串行进位加法器的设计实验报告[详细讲解]](https://img.taocdn.com/s1/m/b8d0677b59fafab069dc5022aaea998fcc2240b2.png)

实验一四位串行进位加法器的设计一、实验目的1.理解一位全加器的工作原理2.掌握串行进位加法器的逻辑原理3.进一步熟悉Quartus软件的使用,了解设计的全过程,二、实验内容1.采用VHDL语言设计四位串行进位的加法器2.采用画原理图的方法设计四位串行进位加法器三、实验步骤1、使用VHDL语言设计1.打开File—>New Project Wizard输入文件名adder4保存在D盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use 语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后保存、编译。

打开File—>New—>Other File—>V ectorW aveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。

从Assignments—>Settings—>Simulator Settings—>Functional然后Processing—>Generate Functional Simnlation Netlist —>确定。

选择Start Simulation保存最后的波形图,打开File—>close 关闭工程。

底层文件:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY fadder ISPORT(a, b,cin : IN STD_LOGIC;s, co : OUT STD_LOGIC);END fadder;ARCHITECTURE arc1 OF fadder ISBEGINs<=a xor b xor cin;co<=((a xor b)and cin)or(a and b);END arc1;顶层文件:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY adder4 ISPORT(c0: IN STD_LOGIC;a,b : IN STD_LOGIC_VECTOR(3 DOWNTO 0);s : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);c4 : OUT STD_LOGIC);END adder4;ARCHITECTURE arc2 OF adder4 ISCOMPONENT fadderPORT(a, b,cin : IN STD_LOGIC;s, co : OUT STD_LOGIC);END COMPONENT;SIGNAL carry : STD_LOGIC_VECTOR(3 DOWNTO 1);BEGINu1 : fadder PORT MAP (a=>a(0), b=>b(0),cin=>c0,s=>s(0),co=>carry (1));u2 : fadder PORT MAP (a=>a(1),b=>b(1),cin=>carry(1),s=>s(1),co=>carry (2));u3 : fadder PORT MAP (a=>a(2),b=>b(2),cin=>carry(2),s=>s(2),co=>carry (3));u4 : fadder PORT MAP(a=>a(3),b=>b(3),cin=>carry(3),s=>s(3),co=>c4);END arc2;2、使用原理图的方法设计打开File—>New Project Wizard输入文件名adder4保存在D盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use 语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后选择File-->Create/Update-->Create Symbol Files for Current File,选择File-->New-->Other File-->V ector W aveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。

4位alu设计实验报告引言阿里巴巴淘宝研发部需要一个高效的算术逻辑单元(ALU),用于处理复杂的计算任务。

本实验旨在设计并实现一个4位ALU,以满足淘宝研发部的需求。

设计思路功能需求根据淘宝研发部的需求,4位ALU需实现以下基本功能:1. 加法运算2. 减法运算3. 与门运算4. 或门运算5. 异或门运算6. 比较两个数的大小(等于、大于、小于)设计方案为了实现这些功能,我们将使用以下组件:1. 4位全加器电路- 用于加法运算2. 4位比较器电路- 用于比较运算3. 4位逻辑门电路- 用于与门、或门、异或门运算设计方案如下:实验步骤1. 设计并实现4位全加器电路2. 设计并实现4位比较器电路3. 设计并实现4位逻辑门电路4. 使用以上电路组件实现4位ALU电路5. 进行基本运算和比较测试,验证ALU功能是否正确实验结果通过实验验证,4位ALU完成了预期的功能需求。

以下是一些测试样例及输出结果:加法运算- 输入:A=1010,B=0011- 输出:Sum=1101减法运算- 输入:A=1010,B=0011- 输出:Diff=0111与门运算- 输入:A=1010,B=0011- 输出:A&B=0010或门运算- 输入:A=1010,B=0011- 输出:A B=1011异或门运算- 输入:A=1010,B=0011- 输出:A^B=1001比较运算- 输入:A=1010,B=0011- 输出:A>B=0001结论本实验成功设计并实现了一个功能齐全的4位ALU电路,能够满足淘宝研发部的需求。

经过测试,ALU能够正确执行加法、减法、与门、或门、异或门以及比较运算。

这个高效的ALU电路将在处理复杂计算任务时发挥巨大作用。

4位全加器实验报告篇一:四位全加器实验报告实验一:四位全加器实验报告实验日期:学生姓名:陆小辉(学号:25)指导老师:黄秋萍加法器是数字系统中的基本逻辑器件,是构成算数运算电路的基本单元。

1位加法器有全加器和半加器两种。

多位加法器构成方式有并行进位方式和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度较快;串行进位加法器是将全加器级联构成多位加法器。

并行进位加法器通常比串行进位加法器占用更多的资源,随着位数的增多,相同位数的并行进位加法器比串行进位加法器的资源占用差距快速增大。

因此,在工程中使用加法器时,要在速度与容量之间寻求平衡。

一、设计要求:设计四位全加器,完成相应的功能。

可采用并行进位方式和串行进位方式,可采用三种常用建模方式中的任意一种。

三、测试代码如(转载自:小草范文网:4位全加器实验报告)下: module text_fulladd4; 二、设计代码如下:(此处采用数据流建模)wire [3:0]sum; module fulladd4(sum,cout,a,b,cin); wire cout; output [3:0]sum; reg [3:0]a,b; output cout; reg cin; input [3:0]a,b; fulladd4 f1(sum,cout,a,b,cin);input cin; initial assign {cout,sum}=a+b+cin; begin endmodule a=4'b0; b=4'b0; cin=1'b0; #210 $stop; end always #10 a=a+1; always #5 b=b+1; always #100 cin=cin+1;endmodule 四、仿真波形如下:续图篇二:4位全加器实验报告数电第一次实验通信1402 程杰 UXX13468【实验目的】采用ISE集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四进制全加器。

EDA实验报告(四选⼀、四位⽐较器、加法器、计数器、巴克码发⽣器)实验1 4选1数据选择器的设计⼀、实验⽬的1.学习EDA软件的基本操作。

2.学习使⽤原理图进⾏设计输⼊。

3.初步掌握器件设计输⼊、编译、仿真和编程的过程。

4.学习实验开发系统的使⽤⽅法。

⼆、实验仪器与器材1.EDA开发软件⼀套2. 微机⼀台3. 实验开发系统⼀台4. 打印机⼀台三、实验说明本实验通过使⽤基本门电路完成4选1数据选择器的设汁,初步掌握EDA设计⽅法中的设汁输⼊、编译、综合、仿真和编程的过程。

实验结果可通过实验开发系统验证,在实验开发系统上选择⾼、低电平开关作为输⼊,选择发光⼆极管显⽰输出电平值。

本实验使⽤Quartus II软件作为设计⼯具,要求熟悉Quartus II软件的使⽤环境和基本操作,如设计输⼊、编译和适配的过程等。

实验中的设计⽂件要求⽤原理图⽅法输⼊,实验时,注意原理图编辑器的使⽤⽅法。

例如,元件、连线、⽹络爼的放巻⽅法和放⼤、缩⼩、存盘、退岀等命令的使⽤。

学会管脚锁定以及编程下载的⽅法等。

四、实验要求1.完成4选1数据选择器的原理图输⼊并进⾏编译;2.对设计的电路进⾏仿真验证:3.编程下载并在实验开发系统上验证设计结果。

五、实验结果管脚分配:N;如kne DteOwn LccatMi Pwecgj G【c^p I/ODo-l 2 GC6P I ifo Xfl-c t nk A Igt PHJ V21Bl NO AS-VLUTrifd2?B Irpjt PIW.VI DJ_W ^>VLVTTl(d 3? co1r(xt P1M IPS5a^Lumid 庐Cl Irpul P1W.KC654a>vivin(d 5* C213P1KLP2S M」JO a>vLum(d 6* C3Inpjt叽⼼:■? ^3-VLVTn(d I* GK incut PJWJtfH7B7JJ1 a>VLUTn(d8o v O J U X A7B7 M J S3-VLVTn(d9<wvx4fr?实验2 四位⽐较器⼀、实验⽬的1. 设计四位⼆进制码⽐较器,并在实验开发系统上验证。

四位加法器实验报告1.实验目的:掌握组合逻辑电路的基本分析与设计方法;理解半加器和全加器的工作原理并掌握利用全加器构成不同字长加法器的各种方法;学习元件例化的方式进行硬件电路设计;学会利用软件仿真实现对数字电路的逻辑功能进行验证和分析。

2.实验仪器:数字逻辑实验箱3.实验内容:A. 设计实现逐次进位加法器,进行软件仿真并在实验平台上测试。

B. 设计实现超前进位加法器,进行软件仿真并在实验平台上测试。

C.使用VHDL自带加法运算实现一个4位全加器。

4.实验代码:A. 逐次进位加法器:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity FDFA is#定义串行加法器总体接口port(A,B:in std_logic_vector(3 downto 0);Ci:in std_logic;S:out std_logic_vector(3 downto 0);Co:out std_logic);end entity;architecture struct of FDFA iscomponent fadder is#基于一位全加器port(a,b,ci:in std_logic;s,co:out std_logic);end component fadder;signal c0,c1,c2:std_logic;beginU0:fadder port map(A(0),B(0),Ci,S(0),c0);U1:fadder port map(A(1),B(1),c0,S(1),c1);U2:fadder port map(A(2),B(2),c1,S(2),c2);U3:fadder port map(A(3),B(3),c2,S(3),Co);end architecture struct;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fadder is #定义一位全加器port(a,b,ci:in std_logic;s,co:out std_logic);end entity;architecture func of fadder isbeginco<=(a and b) or (ci and ( a xor b));s<=a xor b xor ci;end architecture func;B. 超前进位加法器:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity LAC is#定义超前进位加法器总体接口port(A,B:in std_logic_vector(3 downto 0);Ci:in std_logic;Co:out std_logic;S:out std_logic_vector(3 downto 0));end entity;architecture struct of LAC issignal wirep, wireg:std_logic_vector(3 downto 0);signal wirec:std_logic_vector(2 downto 0);component fadder is#基于一位全加器port(Ai,Bi:in std_logic;c:in std_logic;si:out std_logic;pi:out std_logic;gi:out std_logic);end component fadder;component Ker is#Ker总理进位传递信号P与进位产生信号G,以及进位信号C port(ci:in std_logic;P:in std_logic_vector(3 downto 0);G:in std_logic_vector(3 downto 0);C:out std_logic_vector(3 downto 0));end component Ker;beginU0:fadder port map(Ai=>A(0),Bi=>B(0),c=>Ci,si=>S(0),pi=>wirep(0),gi=>wireg(0));U1:fadder port map(Ai=>A(1),Bi=>B(1),c=>wirec(0),si=>S(1),pi=>wirep(1),gi=>wireg(1));U2:fadder port map(Ai=>A(2),Bi=>B(2),c=>wirec(1),si=>S(2),pi=>wirep(2),gi=>wireg(2));U3:fadder port map(Ai=>A(3),Bi=>B(3),c=>wirec(2),si=>S(3),pi=>wirep(3),gi=>wireg(3));L:Ker port map(ci=>Ci,P(0)=>wirep(0),P(1)=>wirep(1),P(2)=>wirep(2),P(3)=>wirep(3),G(0)=>wireg(0),G(1)=>wireg(1),G(2)=>w ireg(2),G(3)=>wireg(3),C(0)=>wirec(0),C(1)=>wirec(1),C(2)=>wirec(2),C(3)=>Co);end architecture struct;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fadder is #定义一位全加器port(Ai,Bi:in std_logic;c:in std_logic;si:out std_logic;pi:out std_logic;gi:out std_logic);end entity;architecture func of fadder isbeginpi<=Ai xor Bi;gi<=Ai and Bi;si<=Ai xor Bi xor c;end architecture func;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity Ker is#定义Ker port(ci:in std_logic;P:in std_logic_vector(3 downto 0);G:in std_logic_vector(3 downto 0);C:out std_logic_vector(3 downto 0));architecture func of Ker isbeginC(0)<=G(0) or ( P(0) and ci );C(1)<=G(1) or ( P(1) and G(0) ) or ( P(1) and P(0) and ci );C(2)<=G(2) or ( P(2) and G(1) ) or ( P(2) and P(1) and G(0) ) or ( P(2) and P(1) and P(0) and ci );C(3)<=G(3) or ( P(3) and G(2) ) or ( P(3) and P(2) and G(1) ) or ( P(3) and P(2) and P(1) and G(0) ) or ( P(3) and P(2) and P(1) and P(0) and ci );end architecture func;C. VHDL自带加法运算实现4位全加器:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity VHDLAD is#定义VHDL自带加法运算实现4位全加器总体接口,如果加和比原来和少,则会进位port(A,B:in std_logic_vector(3 downto 0);Ci:in std_logic;Co:out std_logic;S:out std_logic_vector(3 downto 0));end VHDLAD;architecture bhv of VHDLAD issignal D:std_logic_vector(3 downto 0);beginprocess(A,B,Ci,D)beginD <= A + B;if(Ci = '1') thenD <= D + 1;end if;if(D >= A) thenS <= D;Co <= '0';elseS <= D;Co <= '1';end if;end process;end bhv;5.软件仿真结果说明下面图片每幅有14条信号线,从上到下依次为A的低位到高位(共4条)、B的低位到高位(共4条)、输入的进位信号、和的低位到高位(共4条)、输出进位信号。

电子设计自动化课程实验报告学号:08291117姓名: 图尔荪。

依明班级:电气0804任课老师:李景新第二次实验报告组合电路设计(一)课题:设计一个四位全加器,进位输出是快速进位位一、 实验内容设计一个四位的全加器,进位输出是快速进位位;二、 实验设计及过程(1) 设计思路快速进位加法器,也就是超前进位加法器,其原理简单地说就是使各位的进位直接由加数和被加数来决定,即有如下逻辑表达式:111)(---++=++=i i i i i i i i i i i i C B A B A C B C A B A C而不需要依赖低位进位。

逻辑表达式解释:当第i 位被加数A i 和加数B i 均为1时,有1=i i B A ,由“或”的原理可知,不论低位运算1)(-+i i i C B A 结果如何,本位必然有进位输出(1=iC )。

当A i 和B i 中只有一个为1时,有0=i i B A 且1=+i i B A ,因此1-=i i C C 。

所以,四位二进制全加器的“和”与“进位”相结合,可得到表达式:1-⊕⊕=i i i i C B A S从而构成快速进位加法器。

(2) 流程图(3)程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY quanjiaqi ISPORT(A0,A1,A2,A3,B0,B1,B2,B3,Ci:IN STD_LOGIC;S0,S1,S2,S3,Co:OUT STD_LOGIC );END quanjiaqi;ARCHITECTURE beth OF quanjiaqi ISBEGINPROCESS(A0,A1,A2,A3,B0,B1,B2,B3,Ci)V ARIABLE U0,U1,U2:STD_LOGIC;BEGINS0<=(A0 xor B0) xor Ci;U0:=(A0 AND B0) OR ((A0 OR B0) AND Ci);S1<=(A1 xor B1) xor U0;U1:=(A1 AND B1) OR ((A1 OR B1) AND A0 and B0) or ((A1 or B1) and (A0 or B0) and Ci);S2<=(A2 xor B2) xor U1;U2:=(A2 and B2) or ((A2 or B2) and A1 and B1) or ((A2 or B2) and (A1 or B1) and A0 and B0) or ((A2 or B2)and (A1 or B1) and (A0 or B0) and Ci);S3<=(A3 xor B3) xor U2;Co<=((A3 xor B3) and (A2 xor B2) and (A1 xor B1) and (A0 xor B0) and Ci) or ((A3 xor B3) and (A2 xor B2) and(A1 xor B1) and A0 and B0 ) or ((A3 xor B3) and (A2xor B2) and A1 and B1 ) or ((A3 xor B3) and A2 andB2) or (A3 and B3);END PROCESS;END beth;(4)仿真波形波形解释:1、0——10ns:1+1+1=3;2、10——20ns:6+10=16;3、20——30ns:1+10+5=16;4、30——40ns:1+15+15=31.(注:Ci是借位位,Co是进位位,A与B是加数,S为和)由此可知,该仿真波形说明设计的正确性。

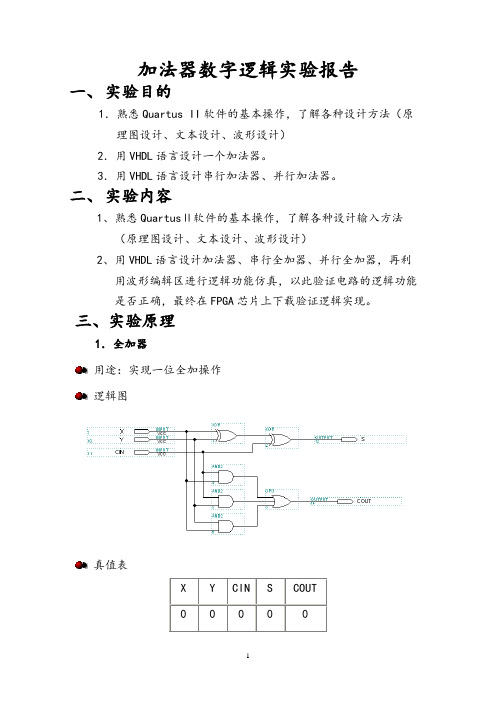

加法器数字逻辑实验报告一、实验目的1.熟悉Quartus II软件的基本操作,了解各种设计方法(原理图设计、文本设计、波形设计)2.用VHDL语言设计一个加法器。

3.用VHDL语言设计串行加法器、并行加法器。

二、实验内容1、熟悉QuartusⅡ软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、波形设计)2、用VHDL语言设计加法器、串行全加器、并行全加器,再利用波形编辑区进行逻辑功能仿真,以此验证电路的逻辑功能是否正确,最终在FPGA芯片上下载验证逻辑实现。

三、实验原理1.全加器用途:实现一位全加操作逻辑图真值表X Y CIN S COUT0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1 VHDL程序数据流描述:波形图2.四位串行加法器逻辑图波形图3.74283:4位先行进位全加器(4-Bit Full Adder)逻辑框图逻辑功能表注:1、输入信号和输出信号采用两位对折列表,节省表格占用的空间,如:[A1/A3]对应的列取值相同,结果和值[Σ1/Σ3]对应的运算是Σ1=A1+B1和Σ3=A3+B3。

请自行验证一下。

2、C2是低两位相加产生的半进位,C4是高两位相加后产生的进位输出,C0是低位级加法器向本级加法器的进位输入。

四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA电路板。

实验步骤:1、建立工程project,并命名顶层文件为JFQ,按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assignment/Device,选取芯片的类型。

选择“FLEX10K——EPF10K20TI144_4”2、编写VHDL源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个VHDL文件。

安徽大学计科院《计算机组成原理》课程设计实验设计报告设计题目:四位并行加法器设计班级:08软件二班小组成员:黄德宏(E20814116)胡从建(E20814110)指导老师:周勇完成日期:2011-3-15一.任务概述1.1设计题目概述:四位并行加法器采用“超前进位产生电路”来同时形成各位进位,从而实现快速加法。

超前进位产生电路是根据各位进位的形成条件来实现的。

它不需要依靠低位进位来到后在进行高位进位,而是根据各位输入同时产生进位,改变了进位逐位传送的方式,明显提高了加法器的工作速度。

1.2设计任务:通过小组合作讨论,利用MuxPlus2软件设计画出四位并行加法器原理图,在实验箱上连线,实现4位二进制数相加并得到正确的结果.1.3设计目的:○1掌握MaxPlus2软件的使用方法,并以此为工具进行设计电路原理图.○2了解加法器的工作原理,掌握超前进位产生电路的设计方法.○3正确将电路原理图下载到试验箱中.○4正确通过实验箱连线实现4位二进制数的相加并得到正确结果.○5增强小组协作的能力以及对知识探求的兴趣。

○6完成设计实验报告.1.4设计思路:加法器是计算机的基本运算部件之一。

若不考虑进位输入,两数码Xn,Yn相加称为半加,如下图为半加其功能表:(b)半加器逻辑图(c)用异或门实现半加器将Xn Yn以及进位输入Cn-1相加称为全价,其功能表如下图:a.(全加器功能表)(b)全加器的逻辑图(c)全加器的全加和Fn也可用异或门表示由功能表可得全加和Fn和进位输出Cn表达式:F n=X n Y n C n-1+ X n Y n C n-1+ X n Y n C n-1+ X n Y n C n-1C n= X n Y n C n-1+ X n n C n-1+n Y n C n-1+ X n Y n C n-1F n还可以用两个半加器来形成:F n=X n○+Y n○+C n-1如此,将n个全加器相连可得n位加法器,如图:但加法时间较长,只是因为其位间进位使串行的传送的,本位全加和Fi必须等低位进位Ci-1来到后才能进行,加法时间与位数有关,只有改变进位逐位传送,才能提高加法器的工作速度。

EDA技术实验报告实验⼀利⽤原理图输⼊法设计4位全加器⼀、实验⽬的:掌握利⽤原理图输⼊法设计简单组合电路的⽅法,掌握MAX+plusII 的层次化设计⽅法。

通过⼀个4位全加器的设计,熟悉⽤EDA 软件进⾏电路设计的详细流程。

⼆、实验原理:⼀个4位全加器可以由4个⼀位全加器构成,全加器的进位以串⾏⽅式实现,即将低位加法器的进位输出cout 与相邻的⾼位加法器的低位进位输⼊信号cin 相接。

1位全加器f-adder 由2个半加器h-adder 和⼀个或门按照下列电路来实现。

半加器h-adder 由与门、同或门和⾮门构成。

四位加法器由4个全加器构成三、实验内容:1. 熟悉QuartusII 软件界⾯,掌握利⽤原理图进⾏电路模块设计的⽅法。

QuartusII 设计流程见教材第五章:QuartusII 应⽤向导。

2.设计1位全加器原理图(1)⽣成⼀个新的图形⽂件(file->new->graphic editor )(2)按照给定的原理图输⼊逻辑门(symbol ->enter symbol)COCO 1S 2S 3S 4(4)为管脚和节点命名:在管脚上的PIN_NAME处双击⿏标左键,然后输⼊名字;选中需命名的线,然后输⼊名字。

(5)创建缺省(Default)符号:在File菜单中选择Create Symbol Files for Current File项,即可创建⼀个设计的符号,该符号可被⾼层设计调⽤。

3.利⽤层次化原理图⽅法设计4位全加器(1)⽣成新的空⽩原理图,作为4位全加器设计输⼊(2)利⽤已经⽣成的1位全加器的缺省符号作为电路单元,设计4位全加器的原理图.4.新建波形⽂件(file->new->Other Files->Vector Waveform File),保存后进⾏仿真(Processing ->Start Simulation),对4位全加器进⾏时序仿真。

实验一四位串行进位加法器的设计

一、实验目的

1.理解一位全加器的工作原理

2.掌握串行进位加法器的逻辑原理

3.进一步熟悉Quartus软件的使用,了解设计的全过程,

二、实验内容

1.采用VHDL语言设计四位串行进位的加法器

2.采用画原理图的方法设计四位串行进位加法器

三、实验步骤

1、使用VHDL语言设计

1.打开File—>New Project Wizard输入文件名adder4保存在D盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后保存、编译。

打开File—>New—>Other File—>Vector Waveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。

从Assignments—>Settings—>Simulator Settings —>Functional

然后Processing—>Generate Functional Simnlation Netlist —>确定。

选择Start Simulation保存最后的波形图,打开File —>close关闭工程。

底层文件:

LIBRARY ieee;

USE fadder IS

PORT

(

a, b,cin : IN STD_LOGIC;

s, co : OUT STD_LOGIC

);

END fadder;

ARCHITECTURE arc1 OF fadder IS

BEGIN

s<=a xor b xor cin;

co<=((a xor b)and cin)or(a and b);

END arc1;

顶层文件:

LIBRARY ieee;

USE adder4 IS

PORT

(

c0: IN STD_LOGIC;

a,b : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

s : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

c4 : OUT STD_LOGIC

);

END adder4;

ARCHITECTURE arc2 OF adder4 IS

COMPONENT fadder

PORT

(

a, b,cin : IN STD_LOGIC;

s, co : OUT STD_LOGIC

);

END COMPONENT;

SIGNAL carry : STD_LOGIC_VECTOR(3 DOWNTO 1); BEGIN

u1 : fadder PORT MAP (a=>a(0), b

=>b(0),cin=>c0,s=>s(0),co=>carry (1));

u2 : fadder PORT MAP (a=>a(1),

b=>b(1),cin=>carry(1),s=>s(1),co=>carry (2));

u3 : fadder PORT MAP (a=>a(2),

b=>b(2),cin=>carry(2),s=>s(2),co=>carry (3));

u4 : fadder PORT MAP

(a=>a(3),b=>b(3),cin=>carry(3),s=>s(3),co=>c4); END arc2;

2、使用原理图的方法设计

打开File—>New Project Wizard输入文件名adder4保存在D 盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后选择File-->Create/Update-->Create Symbol Files for Current File,选择File-->New-->Other File-->Vector Waveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。

从Assignments—>Settings—>Simulator Settings —>Functional

然后Processing—>Generate Functional Simnlation Netlist —>确定。

选择Start Simulation保存最后的波形图,打开File —>close关闭工程。

文件:

LIBRARY ieee;

USE fadder IS

PORT

(

Cin,a, b : IN STD_LOGIC;

s, co : OUT STD_LOGIC

);

END fadder;

ARCHITECTURE arc1 OF fadder IS

BEGIN

s<=a xor b xor cin;

co<=((a xor b)and cin)or(a and b); END arc1;

原理图:

四、实验现象

五、实验体会与收获

问题:Error (10500): VHDL syntax error at (10) near text ")"; expecting an identifier, or "constant", or "file", or "signal", or "variable"

Error (10500): VHDL syntax error at (19) near text "COMPONENT"; expecting ";", or an identifier ("component" is a reserved keyword), or "entity"

Error (10396): VHDL syntax error at (27): name used in construct must match previously specified name "adder4"

Error (10523): Ignored construct adder4 at (3) due to previous errors

解决办法:

c4 : OUT STD_LOGIC;

);改为:

c4 : OUT STD_LOGIC);

OUT STD_LOGIC后面无;

收获:第二种方法中只建立熟悉理解一位全加器的工作原理,掌握串行进位加法器的逻辑原理。