触发器的电路结构和工作原理

- 格式:ppt

- 大小:1.14 MB

- 文档页数:16

常用触发器的工作原理和结构常用触发器是数字电路中常见的一种基本元件,它用来存储和稳定输入信号的状态,并在特定条件下产生输出信号。

常用触发器包括RS触发器、D触发器、JK触发器和T触发器。

本文将详细介绍这些触发器的工作原理和结构。

1.RS触发器:RS触发器是一种简单的触发器,由两个互补反馈的门组成。

它有两个输入端R和S以及两个输出端Q和\(\bar{Q}\)。

当R=0、S=1时,Q=0;当R=1、S=0时,Q=1;当R=S=1时,上一状态保持不变。

RS触发器的结构可以用两个门(通常是与非门)构成。

其中一个门的输入是R和Q,输出是\(\bar{Q}\);另一个门的输入是S和\(\bar{Q}\),输出是Q。

当输入的电平变化时,会通过门电路的逻辑运算,产生输出信号。

2.D触发器:D触发器是一种RS触发器的扩展形式,它只有一个输入端D、一个输出端Q和一个时钟信号端CLK。

D触发器通过时钟信号的输入,对输入信号D进行锁存并在时钟的上升沿或下降沿将锁存的值输出到Q。

D触发器的结构也可以用两个门(与非门和与门)构成。

与非门的输入是D和CLK,输出是\(\bar{Q}\);与门的输入是D和CLK,输出是Q。

当时钟信号变化时,根据输入信号D的电平,通过与非门和与门的逻辑运算,传递输出信号。

3.JK触发器:JK触发器是一种RS触发器的改进形式,它相比于RS触发器可以解决RS触发器由于S和R同时为1时的不稳定状态。

JK触发器有两个输入端J和K,以及两个输出端Q和\(\bar{Q}\)。

当J=0、K=1时,Q=0;当J=1、K=0时,Q=1;当J=K=1时,上一状态取反。

JK触发器的结构可以用两个门(与非门和或门)构成。

与非门的输入是J和Q,输出是\(\bar{Q}\);或门的输入是K和\(\bar{Q}\),还有一个输入是J和K的异或。

当输入信号J和K的电平变化时,通过与非门和或门的逻辑运算,传递输出信号。

4.T触发器:T触发器是一种特殊的JK触发器,其输入端只有一个T(Toggle)信号,以及与JK触发器相同的输出端Q和\(\bar{Q}\)。

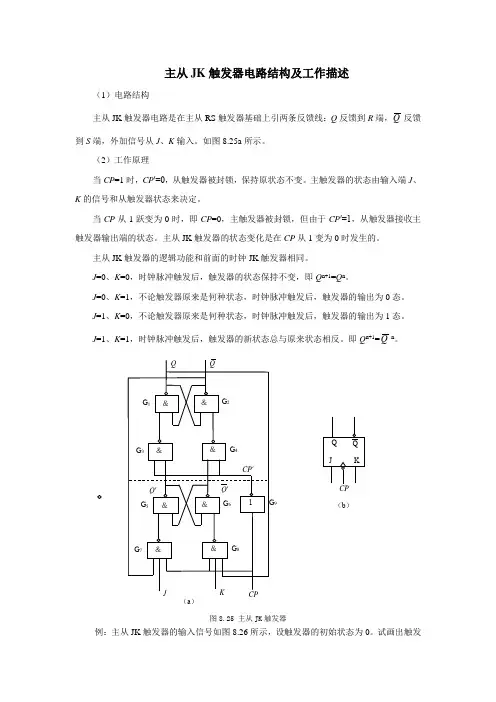

主从JK 触发器电路结构及工作描述(1)电路结构主从JK 触发器电路是在主从RS 触发器基础上引两条反馈线:Q 反馈到R 端,Q 反馈到S 端,外加信号从J 、K 输入。

如图8.25a 所示。

(2)工作原理 当CP =1时,CP ′=0,从触发器被封锁,保持原状态不变。

主触发器的状态由输入端J 、K 的信号和从触发器状态来决定。

当CP 从1跃变为0时,即CP =0,主触发器被封锁,但由于CP ′=1,从触发器接收主触发器输出端的状态。

主从JK 触发器的状态变化是在CP 从1变为0时发生的。

主从JK 触发器的逻辑功能和前面的时钟JK 触发器相同。

J =0、K =0,时钟脉冲触发后,触发器的状态保持不变,即Q n+1=Q n 。

J =0、K =1,不论触发器原来是何种状态,时钟脉冲触发后,触发器的输出为0态。

J =1、K =0,不论触发器原来是何种状态,时钟脉冲触发后,触发器的输出为1态。

J =1、K =1,时钟脉冲触发后,触发器的新状态总与原来状态相反。

即Q n+1=Q n 。

图8.25 主从JK 触发器例:主从JK 触发器的输入信号如图8.26所示,设触发器的初始状态为0。

试画出触发(b )J KQ Q CP Q & & G 1 G 2Q& G 3 & G 4Q ′Q ′ & & G 5 G 6 & G 7 & G 8JK CP 1 G 9 CP ′ (a )器输出的波形图。

CPJKQ图8.26 例题主从JK触发器克服了空翻,但却存在依次变化问题,也就是在CP=1时,JK 中有一端引入干扰信号,主触发器接受时其状态只能变化一次,而干扰信号消失后,触发器无法恢复到干扰前的正常状态,导致输出状态错误。

如图4-17所示。

触发器的初始状态为Q′=0、Q′=1,Q=0、Q=1。

在CP=1期间,J信号变为1,使G7的三个输入端都为1,输出为0,而G8门输入端有0,输出为1。

所以主触发器状态翻转为Q′=1、Q′=0。

第五章 触发器本章教学目的、要求:1. 掌握各种触发器的逻辑功能和工作原理。

2. 熟悉各种触发器的电路结构及动作特点。

3. 了解不同功能触发器之间的相互转换。

重点:触发器的逻辑功能和动作特点。

难点:触发器的不同电路结构及各自的动作特点。

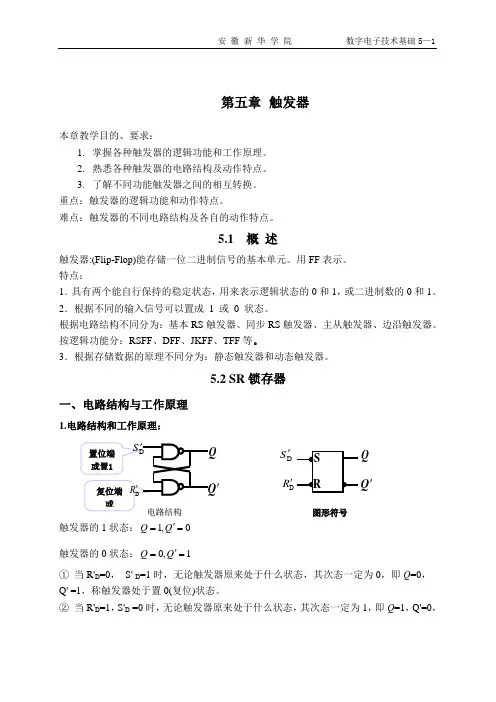

5.1 概 述触发器:(Flip-Flop)能存储一位二进制信号的基本单元。

用FF 表示。

特点:1.具有两个能自行保持的稳定状态,用来表示逻辑状态的0和1,或二进制数的0和1。

2.根据不同的输入信号可以置成 1 或 0 状态。

根据电路结构不同分为:基本RS 触发器、同步RS 触发器、主从触发器、边沿触发器。

按逻辑功能分:RSFF 、DFF 、JKFF 、TFF 等。

3.根据存储数据的原理不同分为:静态触发器和动态触发器。

5.2 SR 锁存器一、电路结构与工作原理1.电路结构和工作原理:触发器的1状态:0,1='=Q Q 触发器的0状态:1,0='=Q Q① 当R'D =0, S' D =1时,无论触发器原来处于什么状态,其次态一定为0,即Q =0,Q' =1,称触发器处于置0(复位)状态。

② 当R'D =1,S'D =0时,无论触发器原来处于什么状态,其次态一定为1,即Q =1,Q'=0,SR图形符号QQ 'D'S D'R 置位端或置1复位端或QQ 'D'S D'R 电路结构称触发器处于置1(置位)状态。

③ 当R'D =1,S'D =1时,触发器状态不变,即Q *=Q ,称触发器处于保持(记忆)状态。

④ 当R'D =0,S'D =0时,两个与非门输出均为1(高电平),此时破坏了触发器的互补输出关系,而且当R'D 、S'D 同时从0变化为1时,由于门的延迟时间不一致,使触发器的次态不确定,即Q *=Ø,这种情况是不允许的。

触发电路的工作原理引言:在现代电子技术中,触发电路是一种重要的电路元件,用于产生特定的脉冲信号,以控制其他电路或设备的工作。

本文将介绍触发电路的工作原理,包括对触发电路的定义、主要类型以及工作原理的详细解释。

一、触发电路的定义触发电路是用于控制其他电路或设备的开关电路,其输入信号被称为触发信号。

触发电路通常由触发器、计数器、比较器等基本元件组成。

通过设置适当的参数和条件,触发电路能够在特定的时刻产生或传递脉冲信号,用于控制其他电路或设备的工作。

二、触发电路的主要类型触发电路根据其工作原理和结构可分为多种类型,其中比较常见的有单稳态触发电路、双稳态触发电路和多稳态触发电路。

下面将分别对这些类型进行详细介绍。

1. 单稳态触发电路:单稳态触发电路在触发信号的作用下,在输出端产生一个持续时间较短的方波脉冲。

单稳态触发电路可分为正脉冲单稳态触发电路和负脉冲单稳态触发电路两种。

正脉冲单稳态触发电路在输入信号为正脉冲时触发,负脉冲单稳态触发电路在输入信号为负脉冲时触发。

2. 双稳态触发电路:双稳态触发电路在触发信号的作用下,在输出端产生两个稳定的状态,即高电平和低电平。

典型的双稳态触发电路有RS触发器、D触发器、JK触发器等。

这些触发器由逻辑门电路构成,能够根据输入信号的变化在输出端产生相应的稳定状态。

3. 多稳态触发电路:多稳态触发电路是指在触发信号的作用下,在输出端产生多个不同的稳定状态。

这类触发电路常用于数字系统中的存储电路和计数器等。

多稳态触发电路的实现较为复杂,通常需要利用逻辑门电路和时序电路来实现。

三、触发电路的工作原理触发电路的工作原理主要涉及触发器的工作机制和逻辑门电路的应用。

触发器是一种存储器件,能够根据输入信号的变化在输出端产生相应的稳定状态。

逻辑门电路则用于控制触发器的输入信号,以实现特定的触发条件。

以JK触发器为例,说明触发电路的工作原理。

JK触发器由两个输入端J和K组成,以及两个输出端Q和Q'。

基本RS触发器电路结构与工作原理依据触发器的电路结构不同,可以将触发器分为基本RS触发器、同步RS触发器、主从型触发器、维持堵塞型触发器和边沿型触发器等类型。

不同类型的触发器具有不同的动作特点。

触发器的动作特点打算它所组成的时序规律电路的规律功能。

分析和设计时序规律电路时,必需首先搞清晰组成该时序规律电路的触发器的电路结构和动作特点,才能得出正确的结果。

基本RS触发器是各种触发器中电路结构最简洁的一种,同时它也是其他简单电路结构触发器的基本组成部分。

图1(a)所示是由非门组成的基本RS触发器的电路,图1(b)所示为基本RS触发器的规律图形符号。

1(a) 电路图1(b) 规律符号如图1(a)所示,基本RS触发器由两个与非门组成。

有两个输入端:端和端。

有两个输出端:Q端和端互为规律相反的状态。

由电路图可以看出,基本RS触发器与组合规律电路相比,基本RS触发器的触发电路中增加了反馈电路,从而实现了触发器的输出状态与电路以前的状态相关的特点。

下面分析基本RS触发器的工作原理。

在学习RS触发器的工作原理以前,首先必需明确几个概念。

基本触发器的输出状态不仅与输入有关,还与触发器原来的状态有关。

在数字电路中,用触发器输出端Q的状态来定义触发器的状态。

当触发器的输出端Q=1时,称触发器的状态为“1”;当触发器的输出端Q=0时,称触发器的状态为“0”。

定义Qn为触发器原来的状态(原态),Qn+1为触发器的新状态(次态)。

依据如图1(a)所示电路,可以写出以下规律式:(1) 依据式(1),可以列出基本RS触发器输入和输出关系的真值表,也叫触发器的特性表,它可直观地描述触发器的动作特点,如表1所示。

表 1 基本RS触发器的特性表QnQn+1功能说明000×不稳定状态001×0101置1(置位)01111000置0(复位)10101100记忆(储存)1111 从表1中可以看出,基本RS触发器的规律功能如下:(1)当=0,=1时,不论触发器原来的状态Qn是0态还是1态,触发器触发后的状态(次态)Qn+1=1,即触发器具有置1(置位)的功能。

常用触发器的工作原理和结构SR触发器的内部结构一般由两个互相激励的双稳态器件组成。

控制信号经过门电路处理,然后通过NAND或NOR逻辑门驱动两个稳态器件,以实现状态的转换。

D触发器是最常用的触发器类型之一、它具有单一输入端D和输出端Q。

D触发器的工作原理和结构比较简单,当D为高电平时,触发器保持之前的状态。

当D为低电平时,触发器的输出将发生变化。

D触发器的内部结构可以由一个稳态器件和传输门构成。

传输门将输入信号传输到稳态器件,从而改变输出状态。

JK触发器是一种综合SR触发器和D触发器的特点而形成的一种触发器。

它具有两个输入端J和K,输出端Q和Q'。

JK触发器的工作原理和结构与SR触发器相似,当J和K的输入信号同时为高电平时,JK触发器的输出将保持之前的状态。

当J为高电平,K为低电平时,触发器将置位。

当J为低电平,K为高电平时,触发器将复位。

而当J和K的输入信号同时为低电平时,相当于输出状态未定义,属于禁止状态。

T触发器是一种特殊的JK触发器,它只有一个输入端T。

T触发器的工作原理和结构与JK触发器类似,当T为高电平时,触发器的输出将保持之前的状态。

当T为低电平时,触发器的输出将发生变化。

T触发器的内部结构可以由一个稳态器件和传输门构成,传输门将输入信号传输到稳态器件,从而改变输出状态。

综上所述,常用触发器的工作原理和结构主要包括不同类型触发器的输入条件、内部结构和实现方式等方面。

它们通过控制输入信号的组合来改变输出状态,并在数字电路中起到存储和持续输出特定逻辑状态的作用。

不同类型的触发器在使用时可以根据实际需求选择合适的类型,以满足不同场景的使用要求。