PCI-Express总线的接口电路设计

- 格式:pdf

- 大小:504.20 KB

- 文档页数:11

PCIE接口的设计与应用培训简介PCI Express(简称PCIE)是一种计算机总线技术,广泛用于计算机的扩展卡和主板之间的高速数据传输。

在现代计算机系统中,PCIE接口已成为一种重要的技术标准。

本文档将介绍PCIE接口的设计原理和应用开发,以帮助读者更好地了解PCIE接口的工作方式和使用方法。

PCIE接口的基本原理PCIE接口采用了串行总线的方式,相比传统的并行总线具有更高的带宽和更快的数据传输速度。

它采用了差分信号传输和包络调制的技术,可以在较短的时间内传输更多的数据。

PCIE接口的主要特点包括以下几点:•高带宽:PCIE接口支持多通道传输,每个通道的带宽都可以达到几GB/s。

•低延迟:PCIE接口采用了点对点的通信模式,减少了数据传输的延迟。

•热插拔支持:PCIE接口可以在计算机运行的过程中插入或拔出设备,而无需重新启动系统。

•可扩展性:PCIE接口支持多种不同大小和功能的插槽,可以连接不同类型的设备。

PCIE接口的设计流程PCIE接口的设计流程包括硬件设计和软件开发两个方面。

硬件设计主要涉及PCIE接口的物理层设计和协议设计,而软件开发则涉及PCIE接口的驱动程序和应用程序开发。

以下是PCIE接口设计的基本流程:1.硬件设计:–确定PCIE接口的连线方式:根据设计需求选择适合的PCIE 接口类型,如PCIE x1、PCIE x4等,并确定接口的连接方式,如插槽式设计或直插式设计。

–进行连线布局:根据选定的PCIE接口类型和连接方式,在硬件电路板上进行连线布局,并保证信号的稳定性和可靠性。

–完成物理层设计:根据PCIE接口的规范和标准,设计PCIE 接口的物理层电路,包括差分信号线、时钟信号线等。

–实施协议设计:设计PCIE接口的协议层,包括数据传输协议、握手协议等。

确保PCIE接口的正常通信和数据传输。

2.软件开发:–编写PCIE接口驱动程序:根据操作系统的要求,编写PCIE 接口的驱动程序,用于管理和控制PCIE接口的硬件设备。

PCI Express 详细设计目录1PCI EXPRESS介绍 (1)2PCI EXPRESS参数与接口 (1)3实现框图与接口时序 ................................................................................ 错误!未定义书签。

4PCI EXPRESS中模块(功能)的原理与实现.. (2)4.1应用层模块 (2)4.1.1 模块介绍 (2)4.1.2结构、算法(或原理)和实现 (3)4.1.3 参数和接口 (7)4.2配置信号采样模块 (7)4.2.1 模块介绍 (7)4.2.2 结构、算法(或原理)和实现.......................................................... 错误!未定义书签。

4.2.3 参数和接口 (8)4.3PCIE硬核模块 (8)4.3.1 模块介绍 (8)4.3.2 结构、算法(或原理)和实现.......................................................... 错误!未定义书签。

4.3.3 参数和接口 (9)4.4LMI配置模块 (9)4.4.1 模块介绍 (9)4.4.2 结构、算法(或原理)和实现 (10)4.4.3 参数和接口 (10)4.5重新配置时钟模块 (10)4.5.1 模块介绍 (10)4.5.2 结构、算法(或原理)和实现.......................................................... 错误!未定义书签。

4.5.3 参数和接口 (10)4.6兼容性测试模块 (10)4.6.1 模块介绍 (10)PCI Express详细设计1PCI Express介绍PCIE设备按照一定的拓扑连接构成总线结构,设备与设备通过协议规定的事务包(TLP)进行通信。

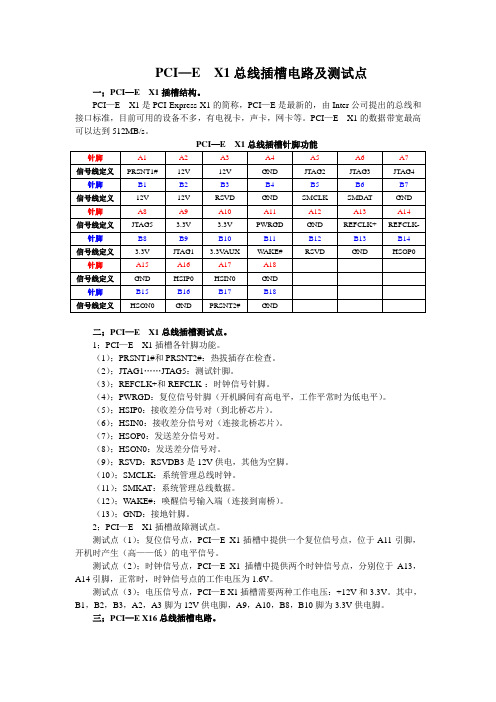

PCI—E X1总线插槽电路及测试点一;PCI—E X1插槽结构。

PCI—E X1是PCI Express X1的简称,PCI—E是最新的,由Inter公司提出的总线和接口标准,目前可用的设备不多,有电视卡,声卡,网卡等。

PCI—E X1的数据带宽最高可以达到512MB/s。

二;PCI—E X1总线插槽测试点。

1;PCI—E X1插槽各针脚功能。

(1);PRSNT1#和PRSNT2#:热拔插存在检查。

(2);JTAG1……JTAG5:测试针脚。

(3);REFCLK+和REFCLK-:时钟信号针脚。

(4);PWRGD:复位信号针脚(开机瞬间有高电平,工作平常时为低电平)。

(5);HSIP0:接收差分信号对(到北桥芯片)。

(6);HSIN0:接收差分信号对(连接北桥芯片)。

(7);HSOP0:发送差分信号对。

(8);HSON0:发送差分信号对。

(9);RSVD:RSVDB3是12V供电,其他为空脚。

(10);SMCLK:系统管理总线时钟。

(11);SMKAT:系统管理总线数据。

(12);W AKE#:唤醒信号输入端(连接到南桥)。

(13);GND:接地针脚。

2;PCI—E X1插槽故障测试点。

测试点(1);复位信号点,PCI—E X1插槽中提供一个复位信号点,位于A11引脚,开机时产生(高——低)的电平信号。

测试点(2);时钟信号点,PCI—E X1插槽中提供两个时钟信号点,分别位于A13,A14引脚,正常时,时钟信号点的工作电压为1.6V。

测试点(3);电压信号点,PCI—E X1插槽需要两种工作电压:+12V和3.3V。

其中,B1,B2,B3,A2,A3脚为12V供电脚,A9,A10,B8,B10脚为3.3V供电脚。

三;PCI—E X16总线插槽电路。

B1 12V (+12V供电端)PRSN T1# A1 B2 12V (+12V供电端)(+12V供电端)12V A2 B3 RS VDB3 (+12V供电端)(+12V供电端)12V A3 B4 GND GND A4 B5 SMCLK (SMBCLK)JTAG2 A5 B6 SMDAT (SMBDATA)JTAG3 A6 B7 GND JTAG4 A7 B8 3.3V (3.3V供电端)JTAG5 A8 B9 JTAG1 (3.3V供电端)3.3V A9 B10 3.3V AUX (3VDUAL供电端)(3.3V供电端)3.3V A10 B11 W AKE# (-PCIE_W AKE) (-PCIE-RST复位信号端)PWRGD A11KEYB12 RS VDB12 GND A12 B13 GND (PCIE-CLK0时钟信号端)REFCLK+ A13 B14 HSOP0 (PCIE-OP0) (-PCIE-CLK0时钟信号端)REFCLK- A14 B15 HSON0 (PCIE-ON0) GND A15 B16 GND (PCIE-IP0)HSIP0 A16 B17 PRSN T2# (PCIE-IN0)HSIN0 A17 B18 GND GND A18。

PCI Express布线指南1.简介这个文档介绍了PCI Express 布线过程中要注意的事项。

2. PCI Express互连PCI Express是一种双单工连接的点对点串行差分低电压互联。

每个通道有两对差分信号:传输对TXP/TXN,接收对RXP/RXN。

该信号工作在2.5 GHz并带有嵌入式时钟。

嵌入式时钟通过消除不同差分对的长度匹配简化了布线规则。

不断增加的PCI Express比特率需要一些特别的设计。

而其中最小化互连损耗和抖动预算是关键要求。

2.1 PCI Express的PCB叠层和参考面在PCI Express并没有使用新技术。

一般的PC主板设计成4层叠层,而服务器,工作站和移动系统主板多使用6层或是更多层的叠层。

插卡可以使用4层或是6层叠层。

使用0.5OZ的镀铜微带线和1OZ的铜带状线。

插卡的整体电路板的厚度必须是0.062inch。

移动平台的PCB厚度可以是0.062inch或是0.050inch。

为了尽可能的减少损耗和抖动预算,最重要的考虑因素是设计的目标阻抗,而且要保持阻抗的公差足够小。

更厚的介质层和更宽的走线将会减少损耗。

微带差分线会比带状差分线产生更大的阻抗变化。

信号对应避免参考平面的不连续,譬如分割和空隙。

当信号线变化层时,地信号的过孔应放得靠近信号过孔。

对每对信号的建议是至少放1到3个地信号过孔。

还有永远不要让走线跨过平面的分割。

2.2 走线2.2.1 阻抗PCI Express的连接走线阻抗在4层或6层板时必须保持100Ω差分/60Ω单端;而对8层或10层板阻抗为85 Ω差分/ 55 Ω单端。

2.2.2线宽和线距差分信号的内部耦合和增加与周边的信号间距有助于减少有害串扰的影响和电磁干扰(EMI)的影响。

在微带情况下,差分线的宽度是5 mil,差分对中的2条走线的间距是7mil。

差分对中信号线中有100mil或超过100mil其信号线间距超过7mil,那么可以把信号线走成7mil的线宽。

PCI Express总线Space Wire接口卡研制一、PCI Express总线的基本原理及实现PCI Express总线是一种高速、可扩展、灵活的串行总线。

本文基于PCI Express Gen3 x8总线,介绍了PCI Express总线的基本原理,包括非常重要的数据传输方式,流控制的实现机制,虚拟通道和总线插槽的使用方法等,总结了技术文档中的硬件设计要点,给出了PCI Express接口卡的设计选项和可行方案,举例说明了I/O虚拟存储管道(IOV)技术。

PCI Express Gen3 x8总线是一种32GB/s的通道,并且具有灵活的可扩展性,可应用于许多不同的应用场合。

本文通过分析数据传输方式、流控制和虚拟通道的实现机制,对PCI Express总线的核心技术有了全面的了解。

其次,本文始终把硬件设计要点作为重中之重,给出了PCI Express接口卡的设计选项和可行方案。

通过一个实例来演示IOV技术(即I/O虚存管道)是如何在PCIE接口卡中实现的。

通过本文的研究,我们可以更好地理解PCIE总线,并为下一步开发提供了基础。

我们可以运用所得的现有PCI Express技术,为各种应用场景提供不同的解决方案。

二、Space Wire总线的基本原理及实现Space Wire技术是高速串行数据传输的最新技术,它的应用极为广泛,包括卫星、深海勘探等领域。

本文介绍了Space Wire 总线的基本原理和实现机制,包括数据传输和连接管理。

通过分析Space Wire总线的实现机制,对Space Wire技术进行了深入的研究。

此外,本文还解释了Space Wire总线的工作原理,包括数据传输和连接管理的实现机制。

Space Wire技术是大规模数据传输的重要手段。

本文分析了Space Wire总线的技术架构,并叙述了Space Wire总线的实现机制。

从Space Wire总线的实现机制和链接管理上找出了技术的优点和短处。

基于Virtex5的PCI-Express总线接口设计PCI Express 是由Intel,Dell,Compaq,IBM,Microsoft 等PCI SIG 联合成立的Arapahoe Work Group 共同草拟并推举成取代PCI 总线标准的下一代标准。

PCI Express 利用串行的连接特点能轻松将数据传输速度提到一个很高的频率,达到远远超出PCI 总线的传输速率。

一个PCI Express 连接可以被配置成x1,x2,x4,x8,x12,x16 和x32 的数据带宽。

x1 的通道能实现单向312.5 MB/s(2.5 Gb/s)的传输速率。

Xilinx 公司的Virtex5 系列FPGA 芯片内嵌PCI- ExpressEndpoint Block 硬核,为实现单片可配置PCI-Express 总线解决方案提供了可能。

本文在研究PCI-Express 接口协议和PCI-Express Endpoint Block 硬核的基础上,使用Virtex5LXT50 FPGA 芯片设计PCI Express 接口硬件电路,实现PCI- Express 数据传输。

1 PCI Express 的拓扑结构PCI Express 是一种能够应用于点设备、台式电脑、工作站、服务器、嵌入式计算机和通信平台等所有周边I/O 设备互连的总线。

其拓扑结构如图1 所示,其中包含ROOT COMPLEX(RC)、多个终端(I/O 器件)、开关和PCI Express/PCI 桥路,它们通过PCI Express 进行互联。

500)this.style.width=500;”border=“0”/>RC 是I/O 层次的根部,将CPU/存储器子系统与I/O 相连。

RC 可以支持一个或多个PCI Express 端口,例如英特尔芯片组。

开关定义为多个虚拟PCI 之间的桥路器件的逻辑组,它们使用一种基于地址路由的PCI 桥路机制来传递执行信息,例如IDT PCI Express 开关。

0 引言PXI总线系统的卓越性能和较低的价格,使得越来越多从事自动测试的工程技术人员开始关注PXI的发展。

而PXI总线是PCI总线在仪器领域的扩展,可以将PXI总线分为PCI 总线和PXI扩展的总线两部分。

将进行PCI总线接口电路的设计,从而为设计PXI模块仪器,组建PXI总线自动测试系统做好准备。

目前,PCI总线接口电路的实现主要有两种方案:一是采用一片大容量FPGA/CPLD实现PCI总线接口逻辑;另一种是采用ASIC芯片完成PCI总线的接口电路。

由于PCI总线速度高,协议复杂,采用第一种方案虽然应用很灵活,但是调试困难,开发周期长,而且采用一片工业级可用于PCI接口的FPGA/CPLD完成PCI总线接口功能,远比使用PCI接口芯片的成本高。

采用第二种方案,功能强,价格低,稳定性好,开发周期较短。

通过对上述两种接口方案的比较,从综合开发难度、芯片功能、开发速度和开发经费等方面考虑,在此采用后一种方案完成PCI总线的接口设计。

1 PCI9030芯片及其主要特点PCI9030是全球最大的PCI接口设备制造商PLXTechnology于1999年3月推出的全新的32 b/33 MHz PCI目标设备接口芯片。

它采用PLX先进的SMARTarget技术,不仅为各种应用提供了最大的灵活性,而且大大简化了系统设计,具有最高的性价比,能够满足各种应用的要求。

PLX计划用它替代应用广泛的PCI9050和PCI9052。

PCI9030主要有以下特点;(1)采用PLX先进的SMARTarget技术,完全兼容PCI 2.2协议规范,PCI突发传输速率高达132 MB,/s,是第一个符合CompactPCI PICMG2.1标准的工业级目标设备接口芯片。

(2)支持高达60 MHz的局部总线操作,突发传输模式下速率可达240 MB/s,支持PCI 目标预取模式、PCI目标可编程突发传输、PCI目标延迟写模式和PMW(Posted Memory Writes)模式。

总线的接口电路设计王福泽 (天津工业大学)一、课题背景计算机技术在高性能计算发展中始终是一个关键技术。

其技术特性决定了计算机的处理能力,进而决定了计算机的整体性能以及应用环境。

从根本上来说,无论现在还是将来,技术都将制约着计算机技术的应用与发展,尤其在高端计算领域。

近年来随着高端计算市场的日益活跃,高性能技术之争也愈演愈烈。

当计算机运算处理能力与总线数据传输速度的矛盾日益突出时,新的总线技术便应运而生。

在过去的十几年间,( )总线是成功的,它的平行总线执行机制现在看来依然具有很高的先进性,但其带宽却早已露出疲态。

总线分有六种规格(表1所示),能提供133到2131的数据传输速率,而对于现有高性能产品例如万兆以太网或者光纤通信,传统的的数据传输速率早已入不敷出[4]。

表1 总线六种规格对于64位总线实现,上述所有带宽加倍仔细分析传统的信号技术,可发现并行式总线已逐渐走近其性能的极限,该种总线已经无法轻易地提升频率或降低电压以提高数据传输率:其时钟和数据的同步传输方式受到信号偏移及布局的限制。

高速串行总线的提出,成功的解决了这些问题,其代表应用就是。

采用的串行方式,并且真正使用“电压差分传输”即是两条信号线,以相互间的电压差作为逻辑“0”,“1”的表示,以此方式传输可以将传输频率作极高的提升,使信号容易读取,噪声影响降低。

由于是差分传输,所以每两条信号线才能单向传送1比特,即一根信号线为正、另一根信号线为负,发送互为反相的信号,每一个“1比特”的两条信号线称为一个差分对。

按技术规范规定,一个差分对的传输速率为2.5。

实际使用中,则要使用两个差分对作为一个条链路,分别用做发送和接收。

因为有了这样的机制,使得数据带宽是可以弹性调配的。

根据相关标准总线能够以248121632进行传输(如表2所示),可提供5到160的传输带宽。

当系统内某一通道需要更高频宽时,可以机动调度多个链路给该通道,让其传输频宽提升,以适应一时激增的数据传输需求[1]。

PCIE总线规范范例:PCI-Express板卡PCB设计在像PCIE这样的高频环境中,传送线在信号线上驱动电压变化时会出现阻抗,信号线的宽度和到接地的距离都会影响其阻抗,所以在设计PCB时需要参考PCIE总线规范,特别要注意考虑信号阻抗匹配。

以下供设计PCB时作为参考:●插卡从金手指边缘到PCIE芯片管脚的走线长度应限制在4英寸(约100mm毫米)以内。

超过该长度后需要使用高频差分传输线,我们可以提供延长300mm以上的技术方案。

●PCIE的PERPN,PETPN,PECKPN是三个差分对线,其中PECKPN是100MHz频率的差分信号线,需要注意保护,前两对是2.5GHz频率的差分信号线,更需要注意保护。

●差分对线中的两条走线要同步布线。

如果走线要转弯,那么两条走线应该同步转弯,并且转弯要避免锐角、直角,而应该使用弧线或者钝角转弯。

●差分对线走线过程中尽量避免使用VIA过孔,如果一定要通过过孔换层,那么两条走线应该同步做过孔,并且应该在靠近信号对线过孔处放置GND地信号过孔,条件允许时适当增加周边GND地信号过孔数量。

●差分对线中的两条走线的长度差应该控制在5mil之内,最大10mil(约0.25mm)。

PCB 走线的线宽建议是7mil(约0.18mm),两条走线的净间距建议是7mil。

有关线宽和线间距的详细分析请参考PCIE规范。

●两对差分对线之间的距离(例如PER对与PECK对)、或者差分对线和其它非PCIE信号的距离,建议不小于20mil(约0.5mm),以减少相互之间的串扰和电磁干扰(EMI)的影响。

建议在两对差分对线之间用GND地线隔离,例如,从左向右是:GND、PECK对线、GND、PER对线、GND、PET对线、GND。

●PCIE芯片,尤其是PCIE信号线的PCB反面,应该尽量避免走高频信号线,最好全GND地铺铜。

例如,CH367芯片的SCL信号线、IORD信号线是相对的高频信号线,建议不要穿越PCIE芯片走线。

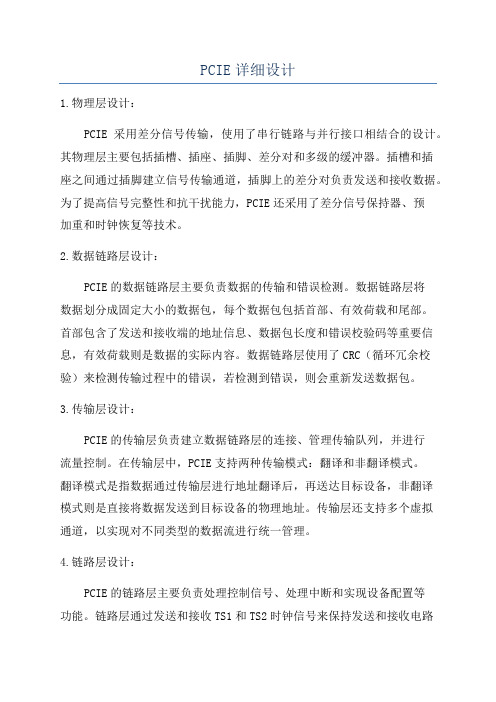

PCIE详细设计1.物理层设计:PCIE采用差分信号传输,使用了串行链路与并行接口相结合的设计。

其物理层主要包括插槽、插座、插脚、差分对和多级的缓冲器。

插槽和插座之间通过插脚建立信号传输通道,插脚上的差分对负责发送和接收数据。

为了提高信号完整性和抗干扰能力,PCIE还采用了差分信号保持器、预加重和时钟恢复等技术。

2.数据链路层设计:PCIE的数据链路层主要负责数据的传输和错误检测。

数据链路层将数据划分成固定大小的数据包,每个数据包包括首部、有效荷载和尾部。

首部包含了发送和接收端的地址信息、数据包长度和错误校验码等重要信息,有效荷载则是数据的实际内容。

数据链路层使用了CRC(循环冗余校验)来检测传输过程中的错误,若检测到错误,则会重新发送数据包。

3.传输层设计:PCIE的传输层负责建立数据链路层的连接、管理传输队列,并进行流量控制。

在传输层中,PCIE支持两种传输模式:翻译和非翻译模式。

翻译模式是指数据通过传输层进行地址翻译后,再送达目标设备,非翻译模式则是直接将数据发送到目标设备的物理地址。

传输层还支持多个虚拟通道,以实现对不同类型的数据流进行统一管理。

4.链路层设计:PCIE的链路层主要负责处理控制信号、处理中断和实现设备配置等功能。

链路层通过发送和接收TS1和TS2时钟信号来保持发送和接收电路的同步。

链路层还负责控制数据包的优先级、设置传输模式和管理中断请求。

此外,链路层还实现了电源管理功能,可以根据需求有效地管理设备的电源消耗。

5.事务层设计:PCIE的事务层负责处理具体的数据传输事务,包括读写操作、配置读写、中断传输和消息传输等。

事务层的处理包括发起者和目标设备两部分,发起者将请求以数据包的形式发送给目标设备,并等待响应。

目标设备接收到请求后,进行相应的处理,并将结果返回给发起者。

总结:PCIE的详细设计包括物理层、数据链路层、传输层、链路层和事务层的设计。

物理层通过差分信号传输实现高速数据传输,数据链路层实现错误检测和数据分组,传输层负责建立连接与进行流量控制,链路层处理控制信号和配置设备,事务层处理具体的数据传输事务。

PCI-Express总线介绍接口设计和实现PCI Express总线是新一代的I/O局部总线标准,是取代PCI总线的革命性总线架构。

PCI总线曾经是PC体系结构发展史上的一个里程碑,但是随着技术的不断发展,新涌现出的一些外部设备对传输速度和带宽有更高的要求,PCI设计之初并没有考虑这些因素,因此并不能完全满足这些外部设备的需求。

PCI Express总线正是在这种背景下应运而生的。

一个PCI Express连接可以被配置成x1、x2、x4、x8、x12、x16和x32的数据带宽。

Xilinx 公司的Virtex5系列FPGA芯片内嵌PCI-Express-Endpoint BLOCk硬核,为实现单片可配置PCI-Express总线解决方案提供了可能。

本文在研究PCI-Express接口协议和PCI-Express Endpoint Block硬核的基础上,使用Virtex5LXT系列的XC5VLX50T FPGA芯片设计PCI- Express接口硬件电路,现YPCI-Express x4总线数据的传输。

1 PCI-Express总线概述PCI-Express是一种高性能、通用的I/O互连技术,可以广泛应用于计算和通讯的平台。

与传统的PCI/PCI-X总线相比,PCI Express用高速串行接口替代了PCI-X的并行接口;用点到点的基于Switch的交换式通讯替代了PCI-X的基于总线的通讯;用基于包的传输协议(PACketbasedprotocol)替代TPCI-X的基于总线的传输协议。

此外,它还引入了一些新的特性:更强的电源管理、服务质量控制(QoS),支持热拔插,以及完善的错误处理和恢复。

1.1 PCI-Express设备/拓扑结构PCI-Express的典型拓扑结构如图1所示。

PCI-Express协议中共定义了三种设备:RootComplex、Endpoint和Switeh。

Root Complex在系统中的位置类似于PCI-X中的主桥,它是I/O层次的根,它将CPU和MM连接至I/O部件。

《基于FPGA的PCIE总线接口和光纤通信模块设计》篇一一、引言随着信息技术和通信技术的快速发展,数据处理和传输速度的需求不断提高。

在高速通信系统中,现场可编程门阵列(FPGA)以其强大的并行处理能力和可定制性,成为了设计高速、高效接口的重要选择。

本文将介绍一种基于FPGA的PCI Express(PCIE)总线接口和光纤通信模块的设计方法。

二、设计概述该设计以FPGA为核心,构建了PCIE总线接口和光纤通信模块。

PCIE总线接口负责数据与主机之间的传输,而光纤通信模块则负责数据的高速、远距离传输。

通过将这两大模块有机结合,可以实现高速、高效、远距离的数据传输和处理。

三、PCIE总线接口设计PCIE总线是一种高速串行计算机扩展总线标准,具有高带宽、低延迟等优点。

在FPGA上实现PCIE总线接口,需要完成以下步骤:1. 确定接口规范:根据实际需求,明确PCIE总线接口的规范,包括数据传输速率、接口协议等。

2. 设计硬件逻辑:根据接口规范,设计FPGA的硬件逻辑,包括PCIe核心、数据通道、缓冲区等。

3. 编程实现:使用硬件描述语言(HDL)对设计进行编程实现,完成FPGA的配置和逻辑控制。

4. 测试验证:通过仿真和实际测试,验证PCIE总线接口的功能和性能。

四、光纤通信模块设计光纤通信模块负责数据的远距离传输,其设计同样需要基于FPGA实现。

具体步骤如下:1. 确定传输标准:根据实际需求,选择合适的光纤传输标准,如SFP、SFP+等。

2. 设计光模块接口:设计FPGA与光模块之间的接口电路,包括光信号的发送和接收。

3. 光纤传输协议设计:根据传输标准,设计光纤传输协议,包括数据编码、解码、纠错等。

4. 实现FPGA逻辑控制:使用HDL编程实现FPGA对光模块的控制,包括数据的发送和接收。

5. 测试验证:对光纤通信模块进行测试,确保其功能和性能满足要求。

五、整体设计与实现将PCIE总线接口和光纤通信模块有机结合,需要在FPGA 上实现整体设计和控制。

PCIExpress总线接口板的设计与实现作者:李丹贺占庄李灏来源:《现代电子技术》2009年第04期摘要:当前,PCI Express总线以其串行点对点传输方式,传输速率高,扩展性灵活等特点广泛应用于台式机、笔记本电脑、服务器、通信、工作站的内置设备等领域。

介绍PCI Express总线接口板的设计与实现。

简要介绍PCI Express总线,采用PLX公司的PEX8311芯片实现接口设计,描述了方案的具体软硬件设计和实现。

关键词:PCI Express;体系结构;PEX8311;复杂可编程逻辑器件;Windriver中图分类号:TP334.7 文献标识码:B 文章编号:1004-373X(2009)04-158-04Design and Implementation of PCI Express Bus Interface BoardLI Dan,HE Zhanzhuang,LI Hao(Xi′an Micro-electronics Technology Institute,Xi′an,710065,China)Abstract:At present,PCI Express bus with its serial point-to-point transmission,high transfer rate and flexible extension is widely used in desktop and notebookcomputers,servers,communications,workstations and other fields. The design and implementation of PCI Express bus interface board and PCI Express bus are introduced briefly.This design uses the chip PEX8311 of PLX Company.This article mainly describes the hardware and software designs.Keywords:PCI Express;system architecture;PEX8311;CPLD;Windriver在过去的十几年中,PCI总线得到了广泛的应用。

基于PCI Express总线的接口模块设计与实现张晓敏;刘炜【期刊名称】《航空计算技术》【年(卷),期】2014(000)005【摘要】为满足高度综合化发展对嵌入式处理系统交联信号的多样性要求,提出了一种基于PCI Express总线架构的多功能接口模块的设计实现方案。

采用一片FPGA作为逻辑设计芯片,实现了包括FC、RS422、ARINC429、USB、IDE等多种接口,满足了综合化发展对模块功能、功耗和重量等要求,可通用于各类综合处理系统接口设计中。

%Aimed at the highly integrated development of the embedded variable signal processing do-main,this paper proposed a design of the multifunctional interface module based of PCI Express bus to -pology ,The module selected a piece of FPGA to meet the logic function requirement and accomplished multi-bus interface includingFC,RS422,ARINC429,USB,IDE and so on,it may meet the requirement of module function ,module energy and module weight and apply to the diversified integrated processing systems .【总页数】4页(P125-127,136)【作者】张晓敏;刘炜【作者单位】中航工业西安航空计算技术研究所,陕西西安710068;中航工业西安航空计算技术研究所,陕西西安710068【正文语种】中文【中图分类】TP336【相关文献】1.基于PCI Express总线的数据处理与传输卡的设计与实现 [J], 王大磊;王斌2.基于PCI Express总线的高速光纤接口卡的设计与实现 [J], 陈雪;李佩玥;章明朝;隋永新;杨怀江3.基于PCI Express总线的高速数据传输卡设计与实现 [J], 潘玉霞;马游春;熊继军4.基于PCI Express总线的同步时钟卡的设计与实现 [J], 陈永志;魏丰;王旭东5.基于PCIe总线的双路1394B接口模块设计与实现 [J], 范祥辉;闫海明;史岩;吴娇因版权原因,仅展示原文概要,查看原文内容请购买。

PCI-Express总线的接口电路设计王福泽 (天津工业大学)一、课题背景计算机I/O技术在高性能计算发展中始终是一个关键技术。

其技术特性决定了计算机I/O的处理能力,进而决定了计算机的整体性能以及应用环境。

从根本上来说,无论现在还是将来,I/O技术都将制约着计算机技术的应用与发展,尤其在高端计算领域。

近年来随着高端计算市场的日益活跃,高性能I/O技术之争也愈演愈烈。

当计算机运算处理能力与总线数据传输速度的矛盾日益突出时,新的总线技术便应运而生。

在过去的十几年间,PCI(Peripheral component Interconnect)总线是成功的,它的平行总线执行机制现在看来依然具有很高的先进性,但其带宽却早已露出疲态。

PCI总线分有六种规格(表1所示),能提供133MBps到2131MBps的数据传输速率,而对于现有高性能产品例如万兆以太网或者光纤通信,传统的PCI的数据传输速率早已入不敷出[4]。

表1 PCI总线六种规格对于64位总线实现,上述所有带宽加倍仔细分析传统的PCI信号技术,可发现并行式总线已逐渐走近其性能的极限,该种总线已经无法轻易地提升频率或降低电压以提高数据传输率:其时钟和数据的同步传输方式受到信号偏移及PCB 布局的限制。

高速串行总线的提出,成功的解决了这些问题,其代表应用就是PCI Express。

PCI Express采用的串行方式,并且真正使用“电压差分传输”即是两条信号线,以相互间的电压差作为逻辑“0”,“1”的表示,以此方式传输可以将传输频率作极高的提升,使信号容易读取,噪声影响降低。

由于是差分传输,所以每两条信号线才能单向传送1比特,即一根信号线为正、另一根信号线为负,发送互为反相的信号,每一个“1比特”的两条信号线称为一个差分对。

按PCI Express技术规范规定,一个差分对的传输速率为2.5Gbps。

实际使用中,则要使用两个差分对作为一个条链路,分别用做发送和接收。

因为有了这样的机制,使得数据带宽是可以弹性调配的。

根据相关标准PCI-Express总线能够以xl/x2/x4/x8/x12/x16/x32进行传输(如表2所示),可提供5Gbps到160Gbps的传输带宽。

当系统内某一通道需要更高频宽时,可以机动调度多个链路给该通道,让其传输频宽提升,以适应一时激增的数据传输需求[1]。

表2 PCI-Express多链路传输速率表除了传输方式的改变外,PCI Express还有一个更有意义的改变,即连接方式的改变。

PCI Express采用点对点连接方式,较PCI的共享总线方式是一个重要的进步。

对于PCI的共享总线方式,PCI总线上在某一时刻只能有一个设备进行通信,一旦PCI总线上挂接的设备增多,每个设备的实际传输速率就会下降,性能也得不到保证。

而PCI Express则采用一种较为先进的连接方式,以点对点的方式处理通信,每个设备在要求传输数据时建立独立的传输通道,对于其它设备这个信道是封闭的,这种操作方式保证了通道的专有性,避免其它设备的干扰,使信号的质量和可靠性增加。

由于是点对点的关系,也很好的保证了其扩展性。

由于PCI-Express只是扩展总线,与操作系统无关,也可保证其与原有PCI的兼容性,给用户的升级带来了方便。

下图为PCI-Express的拓扑结构。

图1 PCI-Express系统拓扑结构PCI Express不但具有高性能的传输速率,而且其通用性也有重要的意义。

由于其通用的模式,不仅可用于北南桥和其它设备的连接,也可以延伸到芯片组间的连接,甚至也可以用于连接图形芯片。

这样整个计算机的I/O系统将重新统一起来,将更进一步的简化计算机系统,使其具有更强的通用性。

从目前己经显现的特点看,PCI Express一改传统PCI的并行总线架构,因此比其它I/O技术有着更为领先的带宽优势,随着时间的推移有逐步取代PCI和PCI-X的趋势。

PCI Express被广泛地认为是一项革命性的总线技术,其重要性可以满足不同使用者的需求。

随着未来持续增加的带宽需求,PCI Express具有广泛的应用前景[2]。

二、基于FPGA的PCI-Express接口具体设计方案本设计将采用Xilinx公司最新的Virtex5LXT设计平台,使用了两个用于实现PCI Express 功能的集成端点模块,其中一个模块(主控模块)具有配置另一个模块(从属模块)的功能。

数据可以在这两个集成端点模块之间双向(即在全双工模式下)流动。

该设计的用户接口是通过本地链路 (LL) 接口提供的。

该设计能够在 x1、x2、x4 和 x8 通道配置下操作[3]。

设计功能如下:•用户接口的本地链路成帧接口♦ 64 位数据总线宽度与 3 位提醒总线♦包化接口,带用于标记包的帧起始 (SOF) 和帧结束 (EOF)•传输和接收方向用户接口的包中断特性•帧错误检测支持•多通道配置支持:x1、x2、x4 和 x8•每通道 1.62 Gb/s 或更高的吞吐量•自动初始化、恢复与通道维护,对用户应用是透明的• Virtex-5 LXT 器件中的集成端点模块1.Xilinx IP核及其应用说明该设计的完整框图如图3所示。

两个端点可以直接通信,其中一个模块(主控模块)具有配置另一个模块(从属模块)的功能,数据可以在两个集成端点模块之间双向流动,用户接口由本地接口提供。

图3 基于PCI-Express的点到点连接结构框图其中主控端可以在本地自行配置,另一端作为从属端,由主控端通过PCI-Express链路进行配置。

进行配置后,该设计便已经准备好可以在全双工模式下进行数据传输操作了。

设计的用户接口符合本地链路协议的要求。

在传输期间,用户提供的本地链路帧在前往集成端点模块进行传输之前,会先被转换成传输层包(TLP)。

在接收期间,来自集成端点模块的TLP会被转换正本地链路帧,而数据以及其他控制信号将通过本地链路接口传送给用户,因此,PCI-Express会分为三个架构模块:配置IP(config IP)、Context IP传输和Context IP接收。

配置IP模块配置IP模块负责在本地配置主控端,并通过 PCI Express 协议链路配置从属端。

配置完成后,会触发 LINK_READY,以表明链路已准备好可以进行数据传输了。

配置期间,将在主控端和从属端设置最大有效载荷大小。

配置 IP 会根据选择的用户设计选项设置集成端点模块的最大有效载荷大小 (MPS),如果是设计选项 1,则设置为 512 字节,如果是设计选项 2,则设置为 1024 字节。

Context IP传输模块Context IP 传输模块采用存储转发技术原理,通过协议链路以存储器写TLP 的形式传输用户帧。

存储器写 TLP 标头中的 TAG 区段未经过定义,可以包含任何值,因此可用于存储帧起始、帧结束、帧中断等标记,这些标记有助于在收到结束信号时重建本地链路帧。

传输器逻辑可将从用户处传来的数据存储在 FIFO 中。

FIFO 的容量等于为选定设计选项设置的MPS。

长度计数器会对有效载荷的长度进行计数,有效载荷的长度用于建立 TLP 标头中的长度区段。

计数器在达到最高计数值(MPS = 512 时为 511, MPS = 1024 时为 1023)后会归零。

帧的长度会存储在长度缓冲器内。

Context传输框图如下图所示:图4 Context传输框图Virtex-5 器件中的内置 FIFO用于进行存储。

如果数据传输之间的链路断开(LINK_UP 信号变为低),则当前存储在缓冲器内的所有数据都将丢失。

由于必须重新进行配置,因此可以将数据传输之间的链路断开视为复位。

如果用户帧大小小于在集成端点模块中设置的MPS,整个帧将作为单个TLP 进行传输,。

Context IP 接收该模块(如图5)可接收来自传输层接收接口的 TLP,然后提取其中的有效载荷。

从TLP的TAG区段提取的标记位将被写入到接收端 FIFO 的数据奇偶位输入区段。

提取的数据以及相应的本地链路成帧信号会被发送给接收端的用户[6]。

图5 Context IP 接收框图2.PCI-Express端点IP核说明Xilinx 提供的 Endpoint Block Plus for PCIe 解决方案适用于 Virtex™-5 LXT/SXT FPGA 架构,是一种可靠的高带宽可缩放串行互连构建模块。

其顶层功能模块如图6所示,从中可以看出,核接口分为系统(SYS)接口、PCI-Express (PCI-EXP)接口、配置(CFG)接口以及事务(TRN)接口。

图6 顶层功能模块和接口核使用数据包在各模块之间交换信息。

数据包在事务层和数据链路层形成,用来承载从发送元件到接收元件的信息。

传输的数据包中包括在各层处理数据包所需的必要信息。

在接收端,各层接收元件处理输入的数据包,剥取相关信息,然后将数据包传送到下一层。

于是,接收到的数据包从其物理层表现形式转换为数据链路层表现形式和事务层表现形式。

Endpoint Block Plus for PCIe核包括顶层信号接口,这些接口按接收方向、发送方向和双向共用信号分组。

下面主要对各个接口进行分别介绍。

系统(SYS)接口系统 (SYS) 接口信号由系统复位信号 sys_reset_n 和系统时钟信号sys_clk 组成,如下表所示:系统复位信号是异步低有效输入信号。

sys_reset_n 的有效置位致使整个核(包括Rocket I/O GTP和Rocket I/O GTX收发器)硬复位。

复位信号发出后,核尝试进行链路初始化并恢复到正常工作状态。

在典型的端点应用中,通常存在应连接到sys_reset_n的边带复位信号。

系统输入时钟的频率必须是100MHz或250MHz,在Core Generator的GUI中选定。

PCI-Express系统的时钟控制方式有两种:其一就是使用同步实在哦好难过控制,其中所有器件共用一个时钟源,另一种是使用非同步始终控制,其中各器件使用自己的时钟源[7]。

PCI-Express接口PCI Express (PCI_EXP) 接口信号由按多个通道组织的收发差分信号对组成。

每个 PCI Express 通道由一对发送差分信号 {pci_exp_txp、pci_exp_txn} 和一对接收差分信号 {pci_exp_rxp、pci_exp_rxn} 组成。

一通道核仅支持通道 0;四通道核支持通道 0-3;八通道核支持通道 0-7。

事务接口事务 (TRN) 接口为用户设计提供生成和使用 TLP 的机制,分为共用事务接口、发送实物接口以及接收事务接口。

配置接口配置 (CFG) 接口供用户设计用来检查 Endpoint for PCIe 配置空间的状态。