专业英语翻译的作业

- 格式:pdf

- 大小:540.75 KB

- 文档页数:4

百度文库- 让每个人平等地提升自我!1Written Assignments for 1301080 (7’) Name Student’s Number ScoreI have been asked many times, what is the role of an outside advisor? How should Presidents use them? My answer is simple: even if he ignores the advice, every President should ensure that he gets a third opinion from selected and seasoned private citizens he trusts, (the second opinion should come from congressional leaders). Though Cabinet members and senior White House aides often resent outside advisors, a President takes too many risks when he relies solely on his staff and the Federal bureaucracy for advice. Each has its own personal or institutional priorities to protect. An outside advisor can serve the role of a Doubting Thomas when the burearucracies line up behind a single position, or help the President reach a judgment where there is a dispute within the government. They can give the President a different perspective on his own situation; they can be frank with him when those in the White House are not.我曾经多次遇到这样的问题,外部进谏者的作用是什么?总统们应当如何利用这些进谏者?我的回答很简单:总统可以不纳谏,但每位总统都应当确保他能从精挑细选、经验丰富,自己信任的第三方那里得到建议(第二方的建议应有国会的领导者提供)。

专业英语翻译作业译文1.科学家们认为,这样微弱的粒子正则轨道实际上是不存在的。

的想法现在已被事实否定了。

2.虽然小行星很小很微弱,天文学家已经知道很多关于它们的大小,形状和组合物,通过使用各种直接和间接的技术。

例如,它是已知的许多小行星的亮度的周期性变化。

3.随着疾病的进展,大肌肉也稳步增长疲软。

如果不治疗,患者变得瘫痪有呼吸非常困难,并最终死亡。

4.将信息从计算机的一部分转移到另一个取决于电流进行了线。

5.只有两件事是天文观测----站立的地方和地方看需要。

6.太阳风严重扭曲地球磁场,把它拖了一个长长的尾巴。

7.使用计算机,我们组成了一系列的合成歌曲的混合自然音节为不同的模式。

8.苍头燕雀的显示,找出正确的声音模仿的本能,这表明本能学习鸟类作为他们发展他们的歌曲一样重要。

9.We know from the fossil record that our ancestors and other intelligent creatures,the australopithecines,branched off from an apelike creature 2.5 million to 3 million years ago ,and coexisted until the australopithecines died out a little less than a million years ago.Stone tools and other evidence at campsites that date form about 2,000,000 B.C.indicate that some form of australopithecine performed human activities ------ making tools,sharing food and working together.我们知道从化石记录我们的祖先和其他智能生物,猿,分枝从远古的生物2500000到3000000年前,南方古猿和共存直到死了比一百万年前少了一点。

一、改译宰客slaughter customers(cheating customers)自学self learn(study on one’s self)彩票colorful tickets(lottery)救火save a fire(Firefighting)(电脑)死机systerm dead(computer crash)吃食堂eat the canteen(eat in the canteen)风凉话cold word(sarcastic remark)太平门safe door(emergency exit)三角债triangle debts(chain debts)扣帽子put a hat on(put a label on)文化程度cultural degree(education level)抓紧时间grasp time firmly(hurry up)来信写道the latter writes(the letter reads)提高英语水平raise the level of one’s English(Improve one’s English)胸有成竹have a bamboo in one’s stomach(have a well-thought-out plan) 二、直译大海捞针Look for a needle in the ocean猫哭耗子假慈悲Cat cry for mouse嫁鸡随鸡嫁狗随狗Marry a chicken with chicken married dog follows dog挥金如土Spend money like water易如反掌As easy as to turn one's hand打草惊蛇To beat the grass and frighten away the snake呆若木鸡Dumb as a wooden chicken千里之行始于足下Every journey begins with the first step瑞雪兆丰年A timely heavy snow promises a good harvest .跑得了和尚跑不了庙Run a monk can not run the temple三、重点翻译她经常在邻里之间搬弄是非She always makes mischief between neighbors.她毛遂自荐来这所学校当老师She recommending herself to be a teacher in this school.正真的好朋友应该是雪中送炭True friend is who provides you timely help.我要有个三长两短,你给我娘捎个话If something happens to me, please give my mother a massage.留得青山在,不愁没柴烧As long as the green mountains are there, one need not worry about firewood.你这人真的是狗嘴里吐不出象牙他对你的许诺不过是个空头支票而已His promise to you just a blank check.我喜欢那套房子,但美中不足的是离上班的地方太远I like that house,but the fly in the ointment is too far away from the work place.四、翻译句子中国将永远与亚洲各国一道,荣辱相依,休戚与共,共同开创亚洲新未来China will forge ahead and share weal and woe with other Asian countries in a joint effort to open up new vistas for Asia's development.在中国文化中,每12年是一个生肖循环,照此说来,博鳌亚种论坛正处于一个新的起点上,希望更上一层楼In the Chinese culture, 12 years form a zodiac cycle. In this sense, the Boao Forum has reached a new starting point and I hope it will scale an even greater height.面对这些新情况,新问题,亚洲国家要同舟共济、共克时艰,把经济的互补性转化为发展的互助力,不断扩大利益交汇点,实现互惠共存、互利共赢Faced with these new situations and problems, the Asian countries should help each other to overcome the difficulties, to transformed economic comp -lementarity and mutual assistance into development power, continues to ex pand common interests and achieve mutual coexistence, mutual benefit and win-win.不当家不知当家难,事实上,单就解决面临的日常问题需要我们长期扶持大量的投入和心意Never kown how difficult it is to keep house even you did. I fact,it needs a large number and long-term support of investment and mind only to manage the daily problems facing.凡是预则立,面对当前复杂形势,我们既要冷机观察、保持定力,又要未雨绸缪,主动作为,宏观调控要把握总量平衡,更要着眼结构优化,根据形势变化合理把控调控的政策力度,适时采取针对性强的差异化措施Preparedness ensures success.Faced with this complex situation, we need to calmly assess the current developments, stay focused, and take initiatives as called for. In exercising macro-control, we will endeavor to strike a balance between aggregate supply and demand, focus on improving the economic structure, ensure proper policy intensity of macro-control in the light of changing situation and take targeted and differentiated measures as appropriate.。

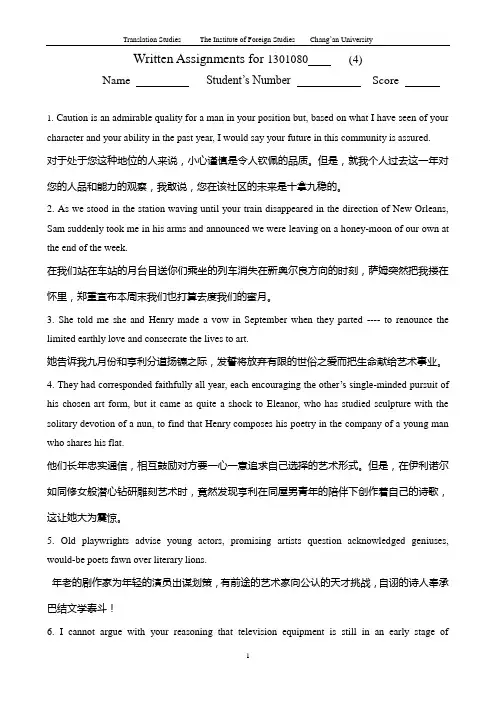

Written Assignments for 1301080 (4)Name Student’s Number Score1. Caution is an admirable quality for a man in your position but, based on what I have seen of your character and your ability in the past year, I would say your future in this community is assured.对于处于您这种地位的人来说,小心谨慎是令人钦佩的品质。

但是,就我个人过去这一年对您的人品和能力的观察,我敢说,您在该社区的未来是十拿九稳的。

2. As we stood in the station waving until your train disappeared in the direction of New Orleans, Sam suddenly took me in his arms and announced we were leaving on a honey-moon of our own at the end of the week.在我们站在车站的月台目送你们乘坐的列车消失在新奥尔良方向的时刻,萨姆突然把我搂在怀里,郑重宣布本周末我们也打算去度我们的蜜月。

3. She told me she and Henry made a vow in September when they parted ---- to renounce the limited earthly love and consecrate the lives to art.她告诉我九月份和亨利分道扬镳之际,发誓将放弃有限的世俗之爱而把生命献给艺术事业。

4. They had corresponded faithfully all year, each encouraging the other’s single-minded pursuit of his chosen art form, but it came as quite a shock to Eleanor, who has studied sculpture with the solitary devotion of a nun, to find that Henry composes his poetry in the company of a young man who shares his flat.他们长年忠实通信,相互鼓励对方要一心一意追求自己选择的艺术形式。

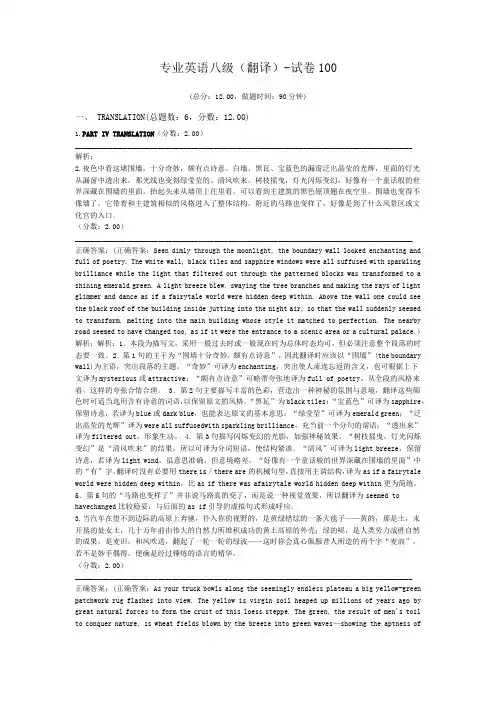

专业英语八级(翻译)-试卷100(总分:12.00,做题时间:90分钟)一、 TRANSLATION(总题数:6,分数:12.00)1.PART IV TRANSLATION(分数:2.00)__________________________________________________________________________________________解析:2.夜色中看这堵围墙,十分奇妙,颇有点诗意。

白墙、黑瓦、宝蓝色的漏窗泛出晶莹的光辉,里面的灯光从漏窗中透出来,那光线也变得绿莹莹的。

清风吹来,树枝摇曳,灯光闪烁变幻,好像有一个童话般的世界深藏在围墙的里面。

抬起头来从墙顶上往里看,可以看到主建筑的黑色屋顶翘在夜空里,围墙也变得不像墙了,它带着和主建筑相似的风格进入了整体结构。

附近的马路也变样了,好像是到了什么风景区或文化宫的入口。

(分数:2.00)__________________________________________________________________________________________正确答案:(正确答案:Seen dimly through the moonlight, the boundary wall looked enchanting and full of poetry. The white wall, black tiles and sapphire windows were all suffused with sparkling brilliance while the light that filtered out through the patterned blocks was transformed to a shining emerald green. A light breeze blew, swaying the tree branches and making the rays of light glimmer and dance as if a fairytale world were hidden deep within. Above the wall one could see the black roof of the building inside jutting into the night air, so that the wall suddenly seemed to transform, melting into the main building whose style it matched to perfection. The nearby road seemed to have changed too, as if it were the entrance to a scenic area or a cultural palace.) 解析:解析:1.本段为描写文,采用一般过去时或一般现在时为总体时态均可,但必须注意整个段落的时态要一致。

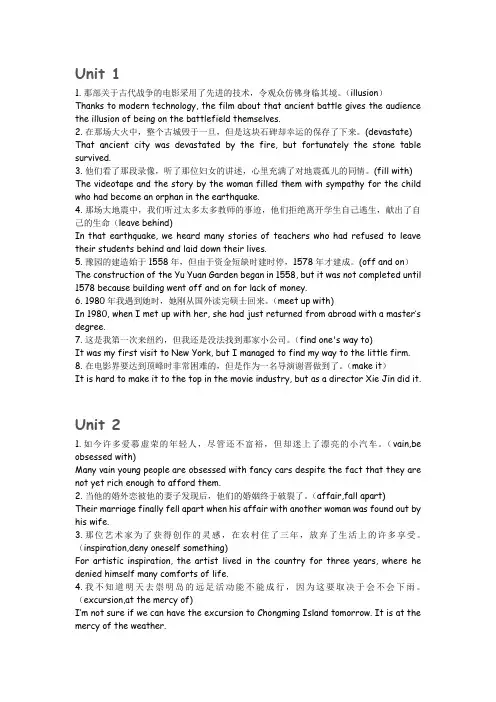

Unit 11.那部关于古代战争的电影采用了先进的技术,令观众仿佛身临其境。

(illusion)Thanks to modern technology, the film about that ancient battle gives the audience the illusion of being on the battlefield themselves.2.在那场大火中,整个古城毁于一旦,但是这块石碑却幸运的保存了下来。

(devastate) That ancient city was devastated by the fire, but fortunately the stone table survived.3.他们看了那段录像,听了那位妇女的讲述,心里充满了对地震孤儿的同情。

(fill with) The videotape and the story by the woman filled them with sympathy for the child who had become an orphan in the earthquake.4.那场大地震中,我们听过太多太多教师的事迹,他们拒绝离开学生自己逃生,献出了自己的生命(leave behind)In that earthquake, we heard many stories of teachers who had refused to leave their students behind and laid down their lives.5.豫园的建造始于1558年,但由于资金短缺时建时停,1578年才建成。

(off and on)The construction of the Yu Yuan Garden began in 1558, but it was not completed until 1578 because building went off and on for lack of money.6.1980年我遇到她时,她刚从国外读完硕士回来。

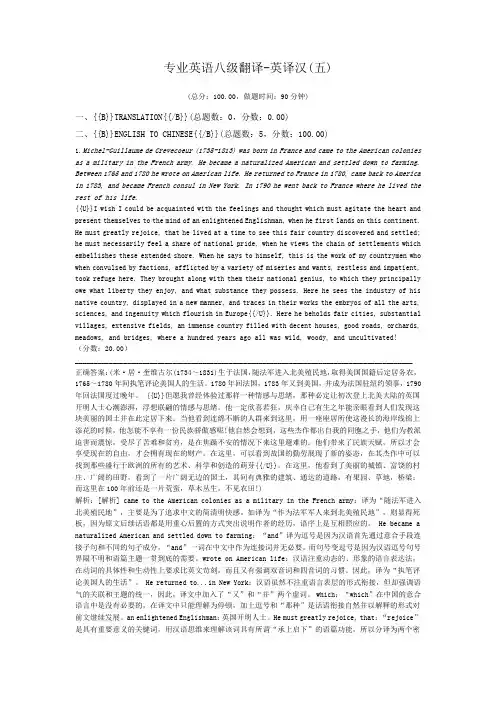

专业英语八级翻译-英译汉(五)(总分:100.00,做题时间:90分钟)一、{{B}}TRANSLATION{{/B}}(总题数:0,分数:0.00)二、{{B}}ENGLISH TO CHINESE{{/B}}(总题数:5,分数:100.00)1.Michel-Guillaume de Crevecoeur (1735-1813) was born in France and came to the American colonies as a military in the French army. He became a naturalized American and settled down to farming. Between 1765 and 1780 he wrote on American life. He returned to France in 1780, came back to America in 1783, and became French consul in New York. In 1790 he went back to France where he lived the rest of his life.{{U}}I wish I could be acquainted with the feelings and thought which must agitate the heart and present themselves to the mind of an enlightened Englishman, when he first lands on this continent. He must greatly rejoice, that he lived at a time to see this fair country discovered and settled; he must necessarily feel a share of national pride, when he views the chain of settlements which embellishes these extended shore. When he says to himself, this is the work of my countrymen who when convulsed by factions, afflicted by a variety of miseries and wants, restless and impatient, took refuge here. They brought along with them their national genius, to which they principally owe what liberty they enjoy, and what substance they possess. Here he sees the industry of his native country, displayed in a new manner, and traces in their works the embryos of all the arts, sciences, and ingenuity which flourish in Europe{{/U}}. Here he beholds fair cities, substantial villages, extensive fields, an immense country filled with decent houses, good roads, orchards, meadows, and bridges, where a hundred years ago all was wild, woody, and uncultivated!(分数:20.00)__________________________________________________________________________________________ 正确答案:(米·居·奎维古尔(1734~1831)生于法国,随法军进入北美殖民地,取得美国国籍后定居务农,1765~1780年间执笔评论美国人的生活。

期末翻译试题题型及各部分分值1-2 长句部分上课列举的例子1. 他的观点被驳地体无完肤2. 但是一百年后,黑人依旧没有获得自由,一百年后,黑人的生活仍然不幸地被种族隔离的镣铐和歧视的枷锁桎梏着。

3. 将这一事实一带而过是无济于事的,需要强调和重复,充分地加以说明。

4. 所有的商品都免费送货,这个新计划在1998年亚洲经济危机最糟糕的时候启动实施。

5. 大规模杀伤性武器没有消失,由于在印度和巴基斯坦进行的核试验,核不扩散条约现在正遭到严重的破坏。

6. 对自己所做的事感到震惊,杰克冲向护栏,纵身跳向下面的岩石,在那里,大海迅速的淹没了他。

7. 将为中国提供多边论坛,用于商讨贸易问题年8. 决不能把个人利益凌驾于国家利益之上个9. 因此需要建立一种机制,让人们即能买得到,又能买得起.10. 他的谎言被当场曝光了重复1.发言人称国务院将修改安全规范和卫生规范2.电流的主要影响是磁效应,电效应,化学效应3.这是我们的立场,不是他们的立场4.他是个石油大亨,一个白手起家的石油大亨5.轰炸外国大使馆很明显的违背了国际法,尤其是违背了日内瓦公约。

6.无知是畏惧的根源,也是羡慕的根源7.世界人们正越来越关注另一项措施,这个措施使吸烟者越来越意识到自己的不良习惯8.总统十分欣慰地宣布,飞机从虚幻的遥远的喜玛拉雅地势低平的地方起飞9.尽管据称原子能发电站没有危害,但这种发电站依然被建在远离人群的地方。

10.这些请愿书一定会送到驻莫斯科的外国记者手里11.字母I代表我,O代表owe12.普通加速度是自由落体的加速度13.太空探测器在不到600英尺的地方穿过了火星,向地面传回许多火星表面的图片14.Out of sight, out of mind眼不见心不烦15.季节的每一次更迭,气候的每一次变换,以及一天中的每一个小时,使山峦的奇幻色彩和形状发生了变化,那些远近的家庭好主妇都把这看做准确的晴雨表正说反译1,第一次轰炸未击中目标2,Hasty makes waste勿用力过猛3,欲速则不达4,We may safely say so我们这样说万无一失5,The explanation is pretty thin这个解释是十分不充分的6,The doubt was still unsolved---他一再解释,一团仍然存在7,He was an indecisive sort of person and always capricious.他这人优柔寡断,而且总是反复无常8,Don’t lose time in doing—赶紧把信寄出去9,With no exception无一例外10,The significance of these incidents wasn’t lost on us.这些事件引起了我们的重视合译1. 安然起初一家公司的名字,然后变成了一桩丑闻的代名词,现在又用做一个及物动词2. 那声音来自远处,但他知道这是一群猎狗在狂吠3. 1953年,我刚从爱尔兰的科尔克勒来此寻找出路被动语态1. 这种不分党派的态度,最常见于秘密会议中2. 许多盆地是由于地壳下沉而形成的3. 他昨晚在一家剧院遇刺了定语从句1. 月球是一个声断音绝的地方,一个万籁俱寂的世界2. There are many people很多人想看这部电影3. 这些会议促使他辞职,理由就是他的年纪越来越大,身体越来越差4. 我们驾驶的飞机几乎每一个部件都有国籍的某种标志5. 只有你能做到这件事6. 这是第一次我和老板发生严重的纠纷,7. 大使只宴请了几个人,因为他特别想她眼里是不错的丈夫人选和这几个人谈谈,听听他们的看法8. 他吃了一只蘑菇,结果就病倒了9. 钢零件上通常涂有油脂,免得生锈10. 水如果不清洁就会引起重病11. 趁你年富力强的时候,为人民做出更多的贡献吧12. 科学家皆勤奋分译1. 离公园几个街区便是与公园平行的克莱门特大街,哪有几十家民族餐馆,热闹得像第二个唐人街2. 他在公司的地位无可争议,又有相当可观的收入,这使得他在他眼里是不错的丈夫人选3. 他没料到他的知识如此渊博,但是觉得有些不好意思,没有说出口4. On December 31,2001,a dozen of members of the European Union 2001年12月31日,十二个欧盟成员国决定启用欧元5. 无论是在事实上,还是在感情上,我都不是他们的敌人,而是他们的朋友6. The shining flowerpot holder stood importantly in the west window--课外Neither should seek hegemony in the Asia-Pacific region and each is opposed to efforts (by any other country or group of countries) (to establish such hegemony), and neither is prepared to negotiate [on behalf of any third party] or to enter into agreements or understandings [with the other] (directed at other states).任何一方都不应该在“亚洲-太平洋”地区谋求霸权,每一方都反对任何国家或国家集团建立这种霸权的努力;任何一方都不准备代表任何第三方进行谈判,也不准备同对方达成针对其他国家的协议或谅解。

2023年自考专业(英语)《英语翻译》考试历年真题摘选附带答案第1卷一.全考点综合测验(共20题)1.【问答题】翻译:I believe Chinese economic authorities recognize the problem and the next Five-Year Plan will address it effectively.2.【问答题】翻译:老年人有长处,但也有很大的弱点—— 老年人容易固执,因此老年人也要有点自觉性。

3.【问答题】翻译:China may well be the favorite whipping boy of manufacturers in the United States these days. But in the developing world, the country is becoming the trading partner of choice, drawing in airplanes from Brazil, soybeans from Argentina and seafood from Malaysia, boosting economies and leading to new political alliances. The growing appetite of the world ’most s populous nation has made China a new source of income for the developing economies of South America and Asia. “ China ’ s booming imports from developing countries especially of commodities — —are not only helping growth in countries from Brazil to Africa, but are already reshaping international trade relations, ” said Kenneth Rogoff, an economics professor at Harvard University. Developed countries also are sending more goods to Chins, the world -largest economy, with an estimated ’ s sixth $1.334 trillion gross domestic product in 2003, according to the IMF.4.【问答题】翻译:It is no use telling grown-up children not to make mistakes, both because they will not believe you, and because mistakes are an essential part of education.5.【单选题】Cicero said, “ In doing so, I did not think it necessary()A. to translate word for wordB.to preserve the general styleC. to keep the force of the languageD.to change the form of the original6.【问答题】英语翻译:Vatican7.【单选题】The devastating floods and droughts that imposed a recurrent tax of suffering on the farmers no longer occur. Egyptian agriculture has been transformed, and industry is benefiting from power generated by the dam.()A.过去不断给农民带来灾难的旱涝两灾,现在不再发生了。

C. Manufacturing Cells (Group Technology)(Familyof Parts Concept)The use of manufacturing cells represents a particular kind of factory layout for manufacturing equipment. The essence of the concept is that, when manufacturing a particular part or family of similar parts in substantial quantities, the equipment for successive operations on the part should be grouped together. The operator - or team of operators who make that part (or the family of parts) - operate all the equipment in the cell. This arrangement is in contrast to a more traditional factory layout that groups like equipment together in departments. Then parts move from departmentto department for each operation. The advantage of the cell layout is that lines of communication and transportation are made very short. The factory's through-put rate is speeded; work-in-process inventory is greatly reduced; when problems arise at one operation, their effect on subsequent operations is immediately recognized. Route sheets to control movement of parts through the factory are greatly simplified or not needed. Operators learn what is needed at each operation to avoid problems at subsequent operations and have the satisfaction of seeing the results of their efforts.Quality tends to improve. The dis-advantage is that C.制造单元(成组技术)(零件族概念)制造单元的使用代表生产设备一种特殊的工厂布局方式。

他总是喝很多酒。

He is a heavy drinker.他在讲话中特别强调提高产品质量。

In his speech, he emphasized on improving the quality of the products in particular.绝对不许违反这个原则。

Never allowed to violate this principle。

林则徐认为,要成功地禁止鸦片买卖,就得首先把鸦片焚毁了。

In Lin Zexu’s opinion, a successful ban of opium trade must be preceded by destruction.医生迅速到达,做了仔细检查,病人得以很快康复。

The doctor’s prompt arrival and careful examination of the patient brought his speedy recovery.一看到校门,我就想起了我的大学时代。

The sight of school gate reminds me of college life.获悉贵国遭受地震,我们极为关切。

We are deeply concerned at the news that your country has been struck by an earthquake.有人在背后支持他。

He got someone behind him.街中的一切逐渐消失在灰暗的暮色里。

Everything in the street was gradually disappeared into gray twilight.经过学校的门口,也改换了名称和模样,令我很生疏。

When I passed the school gate, that too had changed its name and appearance, making me feel quite a stranger.空气是这样的清香,使人感到分外凉爽、舒畅。

翻译作业小组成员:李倩 2140095002 陈玉丹 2140095011 廖江花 2140095001 陈杏文 2140095019 郭琦 2140095015 龚明正 2140095018定语从句1. People who live in the areas where earthquakes are a common occurrence should build houses that are resistant to ground movement.居住在地震多发区的人们应该建造能够抵抗地层移动的房屋。

2. Plants that bear their seeds in this manner are known as angiosperms(被子植物),or flowering plants(显花植物).以这种方式结种子的植物叫做被子植物或者是显花植物。

3. In those days when science remained undeveloped, the crew's knowledge of thunder and lightning was next to nothing.在科学不发达的年代里,水手们对雷电知识几乎一窍不通。

4.He unnecessarily spent a lot of time introducing this book which the students are quite familiar with.他花了大量的时间来介绍学生都十分熟悉的这本书,这是不必要的。

5. The proposal was surprisingly criticized by all walks of people.这条建议受到各阶层人民的反对,真是令人吃惊。

6. Interestingly, America is now dependent on Africa for 40% of its oil imports.有趣的是,现在美国40%的石油进口都依靠非洲。

英语翻译与写作实习作业学院:班级:姓名:学号:翻译练习一、翻译下列各句(注意理解原文)1.she is no fool.她很精明。

2.He is not incapable.他不是无能。

3.I can’t help thinking that he is still alive.我不禁想到还活着。

4.It is a long lane that has no turning.这是一个长巷口没有转弯处。

5.She never comes without bringing some candy for the children.她没有来过没有带来一些糖果给孩子们。

二、翻译下列各句(注意时态的变换)6.After the outbreak of the war, the whole country was armed in a few days.战争爆发后,全国武装起来了好几天。

7.At that meeting an agreement was very soon arrived at.本协议会议非常很快就到了。

8.I’m afraid I shall be laughed at.恐怕我要被人嘲笑。

9.My first twenty years were spent in a poverty-stricken countryside.我的头二十年之前一直在一个非常贫困的农村。

10.They were given a hearty welcome.他们受到热烈欢迎。

11.Rivers are controlled by dams.拦河坝把河流控制住了。

12.Hitler was also washed away by the storms of history.希特勒被历史的风暴席卷而去。

13.Most of the questions have been settled satisfactorily, only a few of secondary大部分问题已经圆满地解决了,只有几次要的14.importance remain to be discussed.重要有待讨论。

1)这种力,是一般人看不见的生命力,只要生命存在,这种力就要显现。

It is an invisible force of life. So long as there is life, the force will show itself2)凭窗站了一会,微微的觉得凉意侵入。

转过身来,忽然眼花缭乱,屋子里的别的东西,都隐在光云里;……Standing at the window for a while, I felt a bit chilly. As I turned round, my eyes suddenly dazzled before the bright light and could not see things distinctly. Everything in the room was blurred by a haze of light.3)这架收音机该有多大的重量啊!它载着解放区人民的心,载着全中国人民的希望,载着我们国家的命运。

What a heavy load this aero plane bore! It carried the hearts of people of the liberated areas, the hopes of the entire Chinese people, and the destiny of our country.4)看着信,林震不禁独自笑起来了,他拿起笔把“中于”改成“终于”,准备在回信时告诉他们下次要避免别字。

5)人无千日好,花无百日红。

Man cannot be alwaysfortunate; flowers do not last forever.(1)6)除了我这间房,大院里还有二十多间房呢。

一共住着多少家子,谁说得清?住两间房的就不多,又搭上今儿个搬来,明儿个又搬走。

我没那么好的记性。

大家见面,招呼声“吃了吗?”透着和气。

英语专业八级翻译练习题1.英译汉(1)Possession for its own sake or in competition with the rest of the neighborhood would have been Thoreau's idea of the low levels. The active discipline of heightening one's perception of what is enduring in nature would have been his idea of the high. What he saved from the low was time and effort he could spend on the high. Thoreau certainly disapproved of starvation, but he would put into feeding himself only as much effort as would keep him functioning for more important efforts.Effort is the gist of it. There is no happiness except as we take on life-engaging difficulties. Short of the impossible, as Yeats put it, the satisfaction we get from a lifetime depends on how high we choose our difficulties. Robert Frost was thinking in something like the same terms when he spoke of "The pleasure of taking pains". The mortal flaw in the advertised version of happiness is in the fact that it purports to be effortless.We demand difficulty even in our games. We demand it because without difficulty there can be no game. A game is a way of making something hard for the fun of it. The rules of the game are an arbitrary imposition of difficulty. When someone ruins the fun, he always does so by refusing to play by the rules. It is easier to win at chess if you are free, at your pleasure, to change the wholly arbitrary rules, but the fun is in winning within the rules. No difficulty, no fun.梭罗所理解的"低层次",即为了拥有而去拥有,或与所有的邻居明争暗斗而致拥有。